UNITRODE UC1875, UC1876, UC1877, UC1878, UC2875 Technical data

...

UC1875DWP

application

INFO

available

UC1875/6/7/8

UC2875/6/7/8

UC3875/6/7/8

Phase Shift Resonant Controller

FEATURES

•Zero to 100% Duty Cycle Control

•Programmable Output Turn-On Delay

•Compatible with Voltage or Current Mode Topologies

•Practical Operation at Switching Frequencies to 1MHz

•Four 2A Totem Pole Outputs

•10MHz Error Amplifier

•Undervoltage Lockout

•Low Startup Current –150 A

•Outputs Active Low During UVLO

•Soft-Start Control

•Latched Over-Current Comparator With Full Cycle Restart

•Trimmed Reference

DESCRIPTION

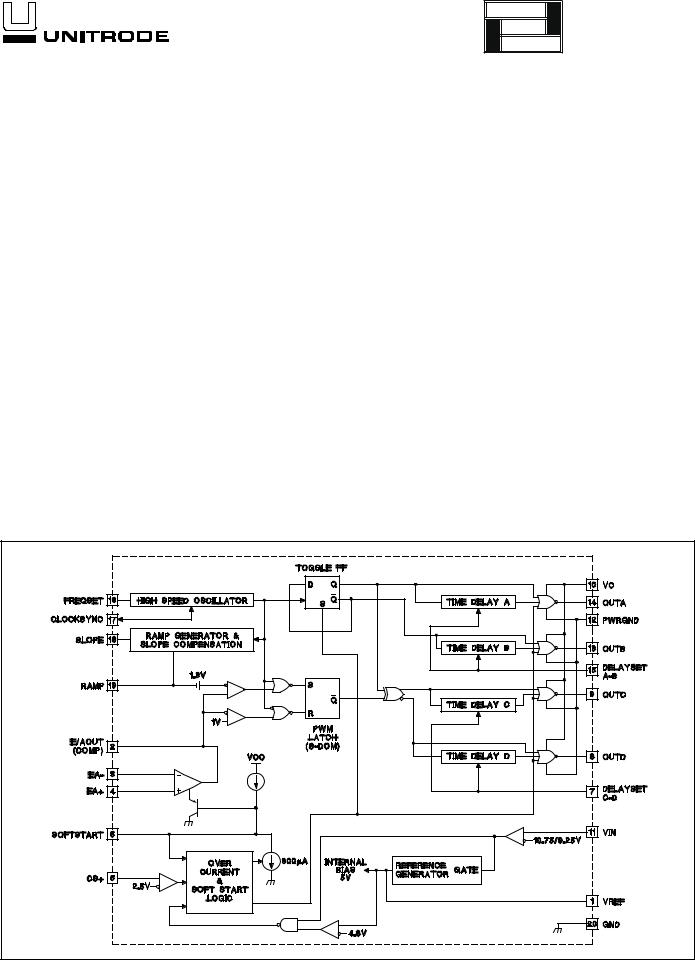

The UC1875 family of integrated circuits implements control of a bridge power stage by phase-shifting the switching of one half-bridge with respect to the other, allowing constant frequency pulse-width modulation in combination with resonant, zero-voltage switching for high efficiency performance at high frequencies. This family of circuits may be configured to provide control in either voltage or current mode operation, with a separate over-current shutdown for fast fault protection.

A programmable time delay is provided to insert a dead-time at the turn-on of each output stage. This delay, providing time to allow the resonant switching action, is independently controllable for each output pair (A-B, C-D).

With the oscillator capable of operation at frequencies in excess of 2MHz, overall switching frequencies to 1MHz are practical. In addition to the standard free running mode, with the CLOCKSYNC pin, the user may configure these devices to accept an external clock synchronization signal, or may lock together up to 5 units with the operational frequency determined by the fastest device.

Protective features include an undervoltage lockout which maintains all outputs in an active-low state until the supply reaches a 10.75V threshold. 1.5V hysteresis is built in for reliable, boot-strapped chip supply. Over-current protection is provided, and will latch the outputs in the OFF state within 70nsec of a fault. The current-fault circuitry implements full-cycle restart operation.

BLOCK DIAGRAM

UDG-95073 |

07/99 |

DESCRIPTION (cont.)

Additional features include an error amplifier with bandwidth in excess of 7MHz, a 5V reference, provisions for soft-starting, and flexible ramp generation and slope compensation circuitry.

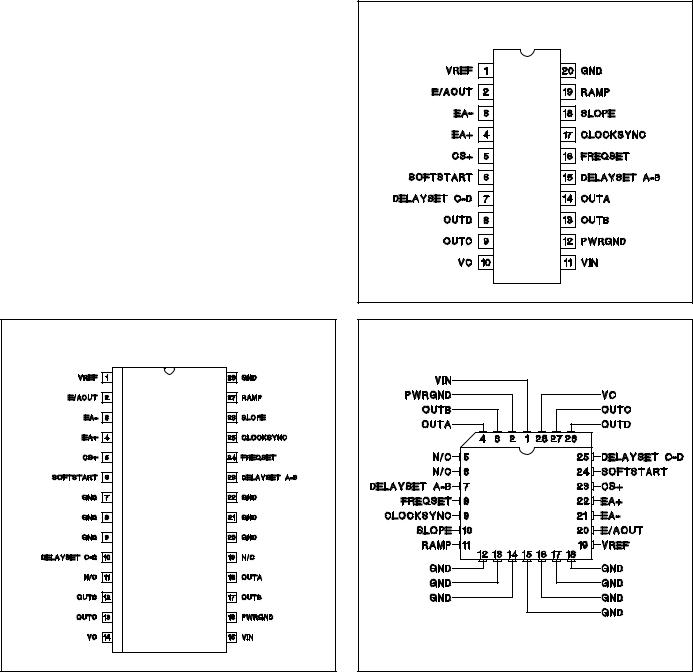

These devices are available in 20-pin DIP, 28-pin “bat-wing” SOIC and 28 lead power PLCC plastic packages for operation over both 0°C to 70°C and –25°C to +85°C temperature ranges; and in hermetically sealed cerdip, and surface mount packages for –55°C to +125°C operation.

|

|

|

UC1875/6/7/8 |

|

|

|

|

UC2875/6/7/8 |

|

|

|

|

UC3875/6/7/8 |

|

|

|

|

|

|

Device |

UVLO |

UVLO |

|

Delay |

|

Turn-On |

Turn-Off |

|

Set |

UC1875 |

10.75 |

9.25V |

|

Yes |

UC1876 |

15.25V |

9.25V |

|

Yes |

UC1877 |

10.75V |

9.25V |

|

No |

UC1878 |

15.25V |

9.25V |

|

No |

ABSOLUTE MAXIMUM RATINGS

Supply Voltage (VC, VIN) . . . . . . . . . . . . . . . . . . . . . . . . . . 20V Output Current, Source or Sink

DC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5A Pulse (0.5 s). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3A

Analog I/0s

(Pins 1, 2, 3, 4, 5, 6, 7, 15, 16, 17, 18, 19) . . . . –0.3 to 5.3V Storage Temperature Range . . . . . . . . . . . . . –65°C to +150°C Junction Temperature. . . . . . . . . . . . . . . . . . . –55°C to +150°C Lead Temperature (Soldering, 10 sec.) . . . . . . . . . . . . +300°C

Note: Pin references are to 20 pin packages. All voltages are with respect to ground. Currents are positive into, negative out of, device terminals. Consult Unitrode databook for information regarding thermal specifications and limitations of packages.

CONNECTION DIAGRAMS

Dil-20 (Top View)

J or N Package

SOIC-28, (Top View)

DWP Package

PLCC-28 (Top View) |

QP Package |

2

UC1875/6/7/8

UC2875/6/7/8

UC3875/6/7/8

Unless otherwise stated, –55°C < TA < 125°C for the UC1875/6/7/8, –25°C < TA <

85°C for the UC2875/6/7/8 and 0°C < TA < 70°C for the UC3875/6/7/8, VC = VIN = 12V, RFREQSET = 12kΩ , CFREQSET = 330pF,

RSLOPE = 12kΩ , CRAMP = 200pF, CDELAYSET A-B = CDELAYSET C-D = 0.01µ F, IDELAYSET A-B = IDELAYSET C-D = –500µ A, TA = TJ.

PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNITS |

Undervoltage Lockout |

|

|

|

|

|

Start Threshold |

UC1875/UC1877 |

|

10.75 |

11.75 |

V |

|

UC1876/UC1878 |

|

15.25 |

|

V |

UVLO Hysteresis |

UC1875/UC1877 |

0.5 |

1.25 |

2.0 |

V |

|

UC1876/UC1878 |

|

6.0 |

|

V |

Supply Current |

|

|

|

|

|

IIN Startup |

VIN = 8V, VC = 20V, RSLOPE open, IDELAY = 0 |

|

150 |

600 |

µ A |

IC Startup |

VIN = 8V, VC = 20V, RSLOPE open, IDELAY = 0 |

|

10 |

100 |

µ A |

IIN |

|

|

30 |

40 |

mA |

IC |

|

|

15 |

30 |

mA |

Voltage Reference |

|

|

|

|

|

Output Voltage |

TJ = +25°C |

4.92 |

5 |

5.08 |

V |

Line Regulation |

11 < VIN < 20V |

|

1 |

10 |

mV |

Load Regulation |

IVREF = –10mA |

|

5 |

20 |

mV |

Total Variation |

Line, Load, Temperature |

4.9 |

|

5.1 |

V |

Noise Voltage |

10Hz to 10kHz |

|

50 |

|

µ Vrms |

Long Term Stability |

TJ = 125°C, 1000 hours |

|

2.5 |

|

mV |

Short Circuit Current |

VREF = 0V, TJ = 25°C |

|

60 |

|

mA |

Error Amplifier |

|

|

|

|

|

Offset Voltage |

|

|

5 |

15 |

mV |

Input Bias Current |

|

|

0.6 |

3 |

µ A |

AVOL |

1V < VE/AOUT < 4V |

|

60 |

90 |

dB |

CMRR |

1.5V < VCM < 5.5V |

75 |

95 |

|

dB |

PSRR |

11V < VIN < 20V |

85 |

100 |

|

dB |

Output Sink Current |

VE/AOUT = 1V |

1 |

2.5 |

|

mA |

Output Source Current |

VE/AOUT = 4V |

|

–1.3 |

–0.5 |

mA |

Output Voltage High |

IE/AOUT = –0.5mA |

4 |

4.7 |

5 |

V |

Output Voltage Low |

IE/AOUT = 1mA |

0 |

0.5 |

1 |

V |

Unity Gain BW |

|

7 |

11 |

|

MHz |

Slew Rate |

|

6 |

11 |

|

V/µ sec |

3

UC1875/6/7/8

UC2875/6/7/8

UC3875/6/7/8

Unless otherwise stated, –55°C < TA < 125°C for the UC1875/6/7/8, –25°C < TA <

85°C for the UC2875/6/7/8 and 0°C < TA < 70°C for the UC3875/6/7/8, VC = VIN = 12V, RFREQSET = 12kΩ , CFREQSET = 330pF,

RSLOPE = 12kΩ , CRAMP = 200pF, CDELAYSET A-B = CDELAYSET C-D = 0.01µ F, IDELAYSET A-B = IDELAYSET C-D = –500µ A, TA = TJ.

PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNITS |

PWM Comparator |

|

|

|

|

|

Ramp Offset Voltage |

TJ = 25°C (Note 3) |

|

1.3 |

|

V |

Zero Phase Shift Voltage |

(Note 4) |

0.55 |

0.9 |

|

V |

PWM Phase Shift (Note1) |

VE/AOUT > (Ramp Peak + Ramp Offset) |

98 |

99.5 |

102 |

% |

|

VE/AOUT < Zero Phase Shift Voltage |

0 |

0.5 |

2 |

% |

Output Skew (Note 1) |

VE/AOUT < 1V |

|

5 |

±20 |

nsec |

Ramp to Output Delay |

UC3875/6/7/8 (Note 6) |

|

65 |

100 |

nsec |

|

UC1875/6/7/8, UC2875/6/7/8 (Note 6) |

|

65 |

125 |

nsec |

Oscillator |

|

|

|

|

|

Initial Accuracy |

TJ = 25°C |

0.85 |

1 |

1.15 |

MHz |

Voltage Stability |

11V < VIN < 20V |

|

0.2 |

2 |

% |

Total Variation |

Line, Temperature |

0.80 |

|

1.20 |

MHz |

Sync Pin Threshold |

TJ = 25°C |

|

3.8 |

|

V |

Clock Out Peak |

TJ = 25°C |

|

4.3 |

|

V |

Clock Out Low |

TJ = 25°C |

|

3.3 |

|

V |

Oscillator (cont.) |

|

|

|

|

|

Clock Out Pulse Width |

RCLOCKSYNC = 3.9kΩ |

|

30 |

100 |

nsec |

Maximum Frequency |

RFREQSET = 5kΩ |

2 |

|

|

MHz |

Ramp Generator/Slope Compensation |

|

|

|

|

|

Ramp Current, Minimum |

ISLOPE = 10µ A, VFREQSET = VREF |

|

–11 |

–14 |

µ A |

Ramp Current, Maximum |

ISLOPE = 1mA, VFREQSET = VREF |

–0.8 |

–0.95 |

|

mA |

Ramp Valley |

|

|

0 |

|

V |

Ramp Peak - Clamping Level |

RFREQSET = 100kΩ |

|

3.8 |

4.1 |

V |

Current Limit |

|

|

|

|

|

Input Bias |

VCS+ = 3V |

|

2 |

5 |

µ A |

Threshold Voltage |

|

2.4 |

2.5 |

2.6 |

V |

Delay to Output |

UC3875/6/7/8 |

|

85 |

125 |

nsec |

|

UC1875/6/7/8, UC2875/6/7/8 |

|

85 |

150 |

nsec |

Soft-Start/Reset Delay |

|

|

|

|

|

Charge Current |

VSOFTSTART = 0.5V |

–20 |

–9 |

–3 |

µ A |

Discharge Current |

VSOFTSTART = 1V |

120 |

230 |

|

µ A |

Restart Threshold |

|

4.3 |

4.7 |

|

V |

Discharge Level |

|

|

300 |

|

mV |

4

Loading...

Loading...