Texas Instruments DAC8550IDGKTG4, DAC8550 Datasheet

DAC8550

DAC8550

DAC8550

SLAS476D – MARCH 2006 – REVISED OCTOBER 2006

16-BIT, ULTRA-LOW GLITCH, VOLTAGE OUTPUT

DIGITAL-TO-ANALOG CONVERTER

FEATURES

∙Relative Accuracy: 3LSB

∙Glitch Energy: 0.1nV-s

∙MicroPower Operation: 140μA at 2.7V

∙Power-On Reset to Midscale

∙Power Supply: +2.7V to +5.5V

∙16-Bit Monotonic Over Temperature

∙Settling Time: 10μs to ±0.003% FSR

∙Low-Power Serial Interface with Schmitt-Triggered Inputs

∙On-Chip Output Buffer Amplifier with Rail-to-Rail Output Amplifier

∙Power-Down Capability

∙2'sComplement Input

∙SYNC Interrupt Facility

∙Drop-In Compatible with DAC8531/01 and DAC8551 (Binary Input)

∙Available in a Tiny MSOP-8 Package

APPLICATIONS

∙Process Control

∙Data Acquisition Systems

∙Closed-Loop Servo-Control

∙PC Peripherals

∙Portable Instrumentation

∙Programmable Attenuation

DESCRIPTION

The DAC8550 is a small, low-power, voltage output, 16-bit digital-to-analog converter (DAC). It is monotonic, provides good linearity, and minimizes undesired code-to-code transient voltages. The DAC8550 uses a versatile, 3-wire serial interface that operates at clock rates of up to 30MHz and is compatible with standard SPI™, QSPI™, Microwire™, and digital signal processor (DSP) interfaces.

The DAC8550 requires an external reference voltage to set its output range. The DAC8550 incorporates a power-on reset circuit that ensures that the DAC output powers up at midscale and remains there until a valid write takes place to the device. The DAC8550 contains a power-down feature, accessed over the serial interface, that reduces the current consumption of the device to 200nA at 5V.

The low-power consumption of this device in normal operation makes it ideal for portable, battery-operated equipment. Power consumption is 0.38mW at 2.7V, reducing to less than 1μW in power-down mode.

The DAC8550 is available in an MSOP-8 package.

For additional flexibilty, see the DAC8551, a binary-coded counterpart to the DAC8550.

|

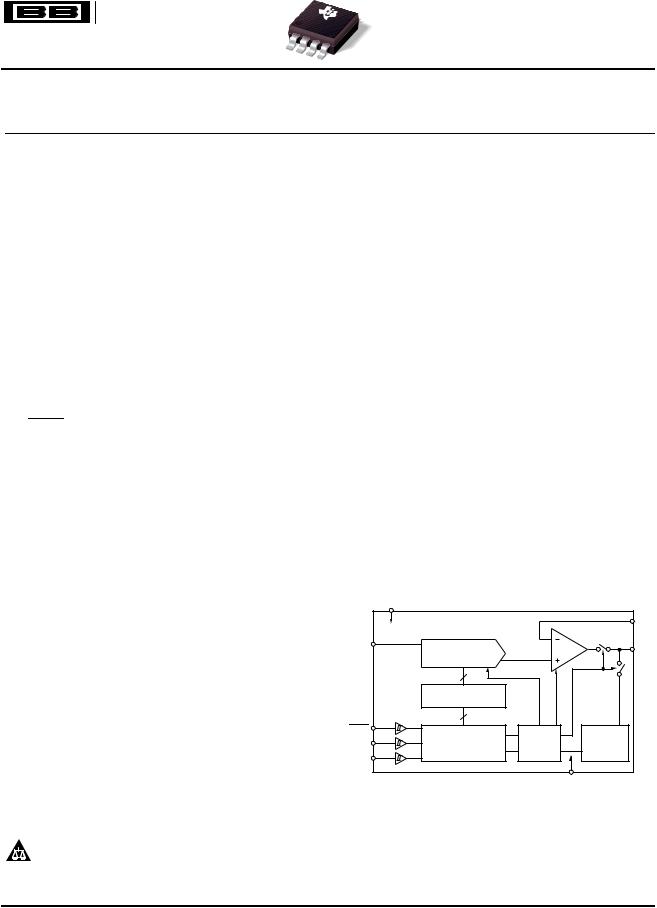

FUNCTIONAL BLOCK DIAGRAM |

|||

|

VDD |

|

|

|

|

|

|

VFB |

|

VREF |

REF (+) |

|

VOUT |

|

|

16-Bit DAC |

|

||

|

16 |

|

|

|

|

DAC Register |

|

|

|

|

16 |

|

|

|

SYNC |

|

|

|

|

SCLK |

Shift Register |

PWB |

Resistor |

|

Control |

Network |

|||

|

|

|||

DIN |

|

|

|

|

|

|

|

GND |

|

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SPI, QSPI are trademarks of Motorola, Inc. Microwire is a trademark of National Semiconductor.

All other trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date. |

Copyright © 2006, Texas Instruments Incorporated |

Products conform to specifications per the terms of the Texas |

|

Instruments standard warranty. Production processing does not |

|

necessarily include testing of all parameters. |

|

DAC8550

www.ti.com

SLAS476D – MARCH 2006 – REVISED OCTOBER 2006

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

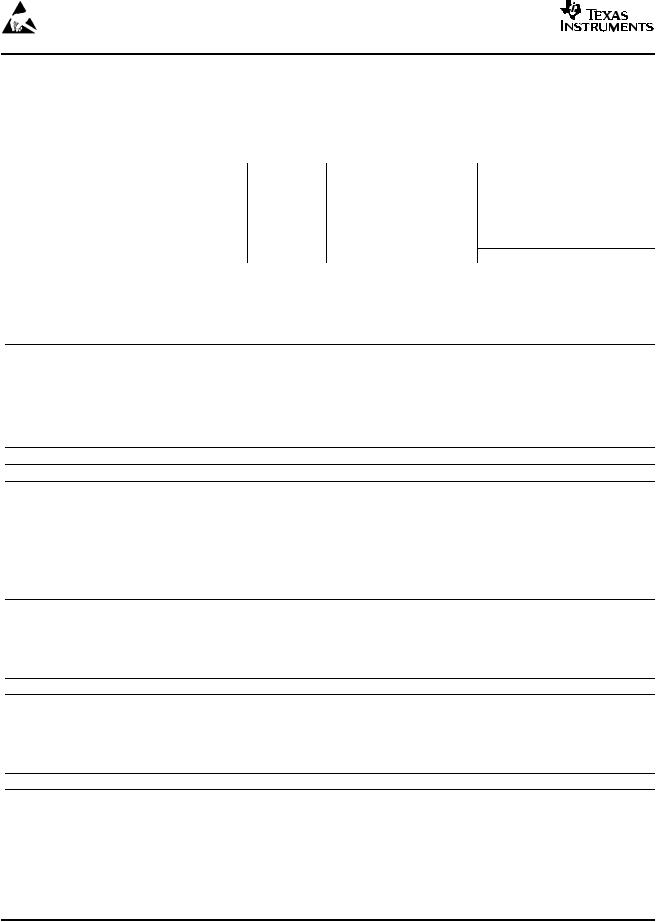

PACKAGING/ORDERING INFORMATION

|

MAXIMUM |

MAXIMUM |

|

|

SPECIFIED |

|

|

TRANSPORT |

|

|

RELATIVE |

DIFFERENTIAL |

PACKAGE |

PACKAGE |

PACKAGE |

ORDERING |

|||

PRODUCT |

TEMPERATURE |

MEDIA, |

|||||||

ACCURACY |

NONLINEARITY |

LEAD |

DESIGNATOR(1) |

MARKING |

NUMBER |

||||

|

RANGE |

QUANTITY |

|||||||

|

(LSB) |

(LSB) |

|

|

|

|

|||

|

|

|

|

|

|

|

|||

DAC8550 |

±12 |

±1 |

MSOP-8 |

DGK |

–40°C to +105°C |

D80 |

DAC8550IDGKT |

Tape and Reel, 250 |

|

DAC8550IDGKR |

Tape and Reel, 2500 |

||||||||

|

|

|

|

|

|

|

|||

DAC8550B |

±8 |

±1 |

MSOP-8 |

DGK |

–40°C to +105°C |

D80 |

DAC8550IBDGKT |

Tape and Reel, 250 |

|

DAC8550IBDGKR |

Tape and Reel, 2500 |

||||||||

|

|

|

|

|

|

|

(1)For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

ABSOLUTE MAXIMUM RATINGS(1)

|

UNIT |

Supply voltage, VDD to GND |

–0.3V to 6V |

Digital input voltage range, VI to GND |

–0.3V to +VDD + 0.3V |

Output voltage, VOUT to GND |

–0.3V to +VDD + 0.3V |

Operating free-air temperature range, TA |

–40°C to +105°C |

Storage temperature range, TSTG |

–65°C to +150°C |

Junction temperature range, TJ(max) |

150°C |

Power dissipation (DGK package) |

(TJmax – TA)/θJA |

Thermal impedance, θJA |

206°C/W |

Thermal impedance, θJC |

44°C/W |

(1)Stresses above those listed under absolute maximum ratings may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

ELECTRICAL CHARACTERISTICS

VDD = 2.7V to 5.5V, –40°C to +105°C range (unless otherwise noted).

|

PARAMETER |

TEST CONDITIONS |

|

MIN |

TYP |

MAX |

UNIT |

STATIC PERFORMANCE(1) |

|

|

|

|

|

|

|

|

Resolution |

|

|

16 |

|

|

Bits |

EL |

Relative accuracy |

Measured by line passing through codes |

DAC8550 |

|

±3 |

±12 |

LSB |

|

|

|

|

|

|||

–32283 and +32063 |

DAC8550B |

|

±3 |

±8 |

LSB |

||

|

|

|

|||||

ED |

Differential nonlinearity |

16-bit Monotonic |

|

|

±0.25 |

±1 |

LSB |

EO |

Zero-code error |

|

|

|

±2 |

±12 |

mV |

EFS |

Full-scale error |

Measured by line passing through codes –32283 and +32063. |

|

±0.05 |

±0.5 |

% of FSR |

|

EG |

Gain error |

|

|

|

±0.02 |

±0.2 |

% of FSR |

|

Zero-code error drift |

|

|

|

±5 |

|

μV/°C |

|

Gain temperature coefficient |

|

|

|

±1 |

|

ppm of FSR/°C |

PSRR |

Power-supply rejection ratio |

RL = 2kΩ, CL = 200pF |

|

|

0.75 |

|

mV/V |

(1)Linearity calculated using a reduced code range of –32283 to +32063; output unloaded.

2 |

Submit Documentation Feedback |

|

|

|

|

|

|

DAC8550 |

|

www.ti.com |

SLAS476D – MARCH 2006 – REVISED OCTOBER 2006 |

||||

|

|

|||||

ELECTRICAL CHARACTERISTICS (continued) |

|

|

|

|

||

VDD = 2.7V to 5.5V, –40°C to +105°C range (unless otherwise noted). |

|

|

|

|

||

|

PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNIT |

OUTPUT CHARACTERISTICS(2) |

|

|

|

|

|

|

VO |

Output voltage range |

|

0 |

|

VREF |

V |

tSD |

Output voltage settling time |

To ±0.003% FSR, 1200h to 8D00h, RL = 2kΩ, 0pF < CL < 200pF |

|

8 |

10 |

μs |

RL = 2kΩ, CL = 500pF |

|

12 |

|

μs |

||

SR |

Slew rate |

|

|

1.8 |

|

V/μs |

|

Capacitive load stability |

RL = ∞ |

|

470 |

|

pF |

|

RL = 2kΩ |

|

1000 |

|

pF |

|

|

|

|

|

|||

|

Code change glitch impulse |

1LSB change around major carry |

|

0.1 |

|

nV-s |

|

Digital feedthrough |

SCLK toggling, FSYNC high |

|

0.1 |

|

|

|

|

|

|

|||

zO |

DC output impedance |

At mid-code input |

|

1 |

|

Ω |

IOS |

Short-circuit current |

VDD = 5V |

|

50 |

|

mA |

VDD = 3V |

|

20 |

|

|||

tON |

Power-up time |

Coming out of power-down mode, VDD = 5V |

|

2.5 |

|

μs |

Coming out of power-down mode, VDD = 3V |

|

5 |

|

|||

|

|

|

|

|

||

AC PERFORMANCE

AC PERFORMANCE

SNR |

Signal-to-noise ratio |

THD |

Total harmonic distortion |

SFDR |

Spurious-free dynamic range |

SINAD |

Signal-to-noise and distortion |

REFERENCE INPUT |

|

VREF |

Reference voltage |

II(REF) |

Reference current input range |

zI(REF) |

Reference input impedance |

LOGIC INPUTS (3) |

|

Input current |

|

VIL |

Low-level input voltage |

VIH |

High-level input voltage |

Pin capacitance

POWER REQUIREMENTS

POWER REQUIREMENTS

VDD

IDD (normal mode)

VDD = 3.6V to 5.5V

VDD = 2.7V to 3.6V

IDD (all power-down modes)

IDD (all power-down modes)

VDD = 3.6V to 5.5V

VDD = 2.7V to 3.6V

POWER EFFICIENCY

POWER EFFICIENCY

IOUT/IDD

TEMPERATURE RANGE

TEMPERATURE RANGE

Specified performance

|

95 |

|

|

|

BW = 20kHz, VDD = 5V, fOUT = 1kHz, |

–85 |

|

dB |

|

|

|

|||

1st 19 harmonics removed for SNR calculation |

87 |

|

||

|

|

|||

|

|

|

||

|

84 |

|

|

|

|

0 |

VDD |

V |

|

VREF = VDD = 5V |

40 |

75 |

μA |

|

VREF = VDD = 3.6V |

30 |

45 |

μA |

|

|

125 |

|

kΩ |

|

|

±1 |

|

μA |

|

VDD = 5V |

|

0.8 |

V |

|

VDD = 3V |

|

0.6 |

||

|

|

|||

VDD = 5V |

2.4 |

|

V |

|

VDD = 3V |

2.1 |

|

||

|

|

|||

|

|

3 |

pF |

|

|

2.7 |

5.5 |

V |

|

Input code equals mid-scale, no load, does not include reference |

|

|

|

|

current |

|

|

|

|

VIH = VDD and VIL = GND |

160 |

250 |

μA |

|

140 |

240 |

|||

|

|

|||

VIH = VDD and VIL = GND |

0.2 |

2 |

μA |

|

|

0.05 |

2 |

||

|

|

|||

ILOAD = 2mA, VDD = 5V |

89 |

|

% |

|

|

–40 |

+105 |

°C |

(2)Specified by design and characterization, not production tested.

(3)Specified by design and characterization, not production tested.

Submit Documentation Feedback |

3 |

DAC8550

www.ti.com

SLAS476D – MARCH 2006 – REVISED OCTOBER 2006

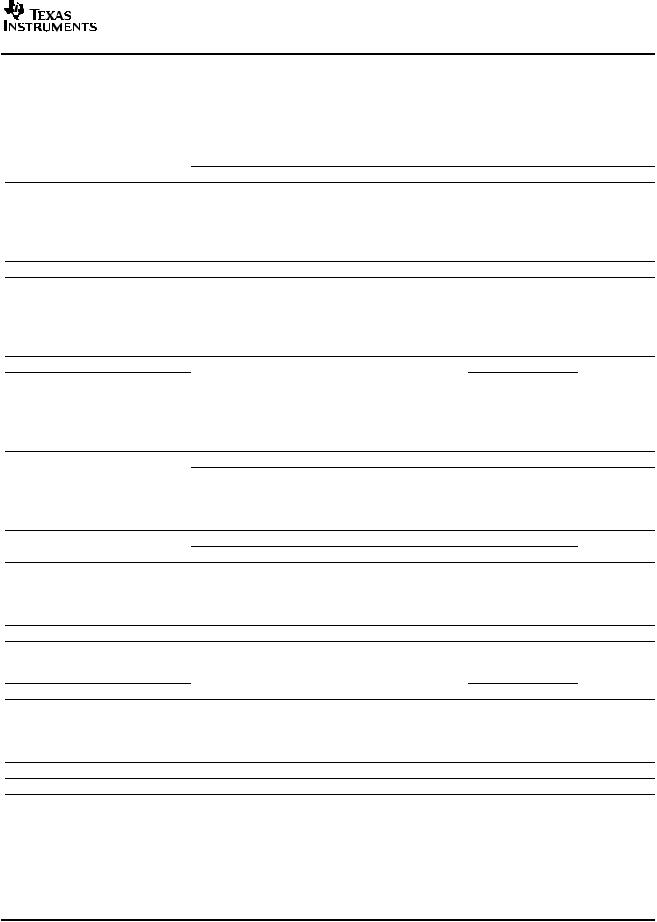

PIN CONFIGURATION

MSOP-8

(Top View)

VDD |

|

|

|

|

GND |

1 |

|

8 |

|

||

VREF |

|

|

|

|

DIN |

2 |

|

7 |

|

||

VFB |

|

DAC8550 |

|

|

SCLK |

|

|

|

|||

3 |

|

6 |

|

||

|

|

|

|

|

|

VOUT |

4 |

|

5 |

|

SYNC |

|

|

|

|

|

|

|

|

PIN DESCRIPTIONS |

|

PIN |

NAME |

DESCRIPTION |

|

1 |

VDD |

Power-supply input, 2.7V to 5.5V. |

|

2 |

VREF |

Reference voltage input. |

|

3 |

VFB |

Feedback connection for the output amplifier. |

|

4 |

VOUT |

Analog output voltage from DAC. The output amplifier has rail-to-rail operation. |

|

|

|

Level-triggered control input (active LOW). This is the frame synchronization signal for the input data. When SYNC goes |

|

5 |

SYNC |

LOW, it enables the input shift register and data is transferred in on the falling edges of the following clocks. The DAC is |

|

updated following the 24th clock (unless SYNC is taken HIGH before this edge, in which case the rising edge of SYNC |

|||

|

|

||

|

|

acts as an interrupt and the write sequence is ignored by the DAC8550). Schmitt-Trigger logic input. |

|

6 |

SCLK |

Serial clock input. Data can be transferred at rates up to 30MHz. Schmitt-Trigger logic input. |

|

7 |

DIN |

Serial data input. Data is clocked into the 24-bit input shift register on each falling edge of the serial clock input. |

|

Schmitt-Trigger logic input. |

|||

8 |

GND |

Ground reference point for all circuitry on the part. |

4 |

Submit Documentation Feedback |

DAC8550

www.ti.com

SLAS476D – MARCH 2006 – REVISED OCTOBER 2006

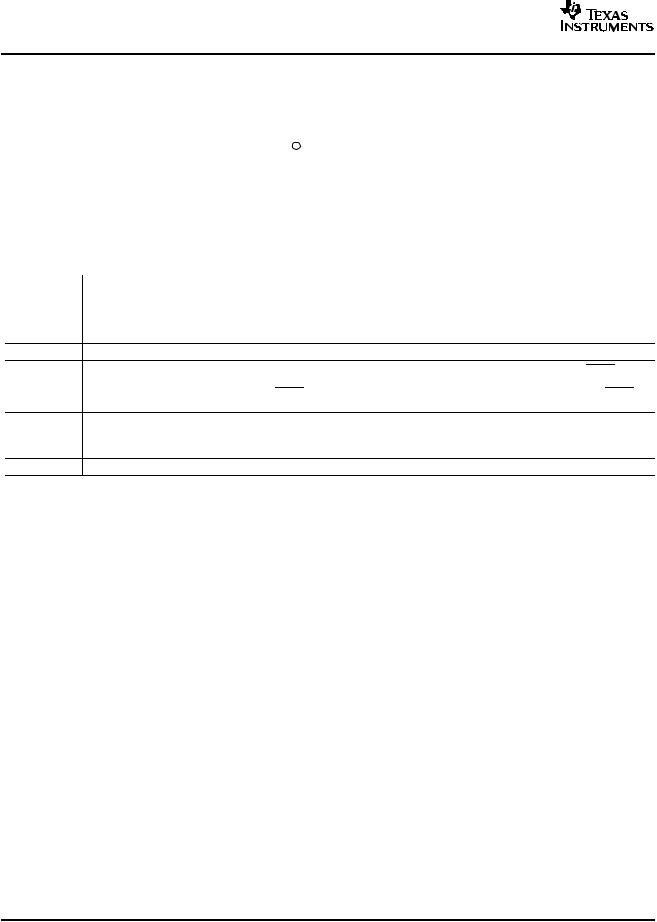

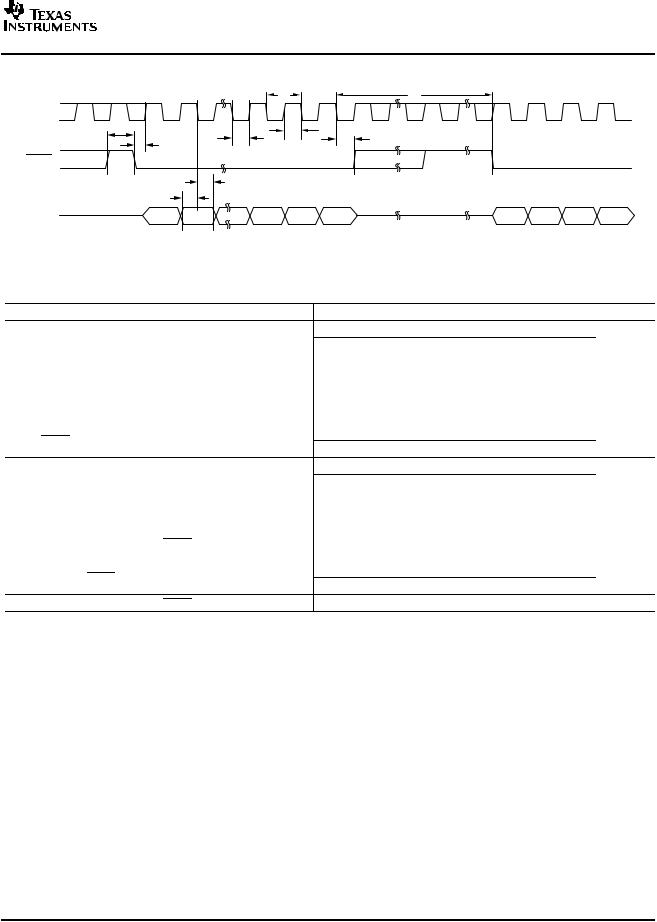

SERIAL WRITE OPERATION

|

t1 |

|

t9 |

SCLK |

1 |

24 |

|

|

t8 |

t2 |

|

|

t3 |

|

|

|

t7 |

|

|

|

t4 |

|

|

SYNC |

|

|

|

|

t6 |

|

|

|

t5 |

|

|

DIN |

DB23 |

DB0 |

DB23 |

TIMING CHARACTERISTICS(1) (2)

VDD = 2.7V to 5.5V, all specifications –40°C to +105°C (unless otherwise noted).

|

PARAMETER |

TEST CONDITIONS |

MIN TYP MAX |

UNIT |

|

t (3) |

SCLK cycle time |

VDD = 2.7V to 3.6V |

50 |

ns |

|

|

|

||||

1 |

|

VDD = 3.6V to 5.5V |

33 |

|

|

|

|

|

|||

t2 |

SCLK HIGH time |

VDD = 2.7V to 3.6V |

13 |

ns |

|

VDD = 3.6V to 5.5V |

13 |

||||

|

|

|

|||

t3 |

SCLK LOW time |

VDD = 2.7V to 3.6V |

22.5 |

ns |

|

VDD = 3.6V to 5.5V |

13 |

||||

|

|

|

|||

t4 |

SYNC to SCLK rising edge setup time |

VDD = 2.7V to 3.6V |

0 |

ns |

|

VDD = 3.6V to 5.5V |

0 |

||||

|

|

|

|||

t5 |

Data setup time |

VDD = 2.7V to 3.6V |

5 |

ns |

|

VDD = 3.6V to 5.5V |

5 |

||||

|

|

|

|||

t6 |

Data hold time |

VDD = 2.7V to 3.6V |

4.5 |

ns |

|

VDD = 3.6V to 5.5V |

4.5 |

||||

|

|

|

|||

t7 |

24th SCLK falling edge to SYNC rising edge |

VDD = 2.7V to 3.6V |

0 |

ns |

|

VDD = 3.6V to 5.5V |

0 |

||||

|

|

|

|||

t8 |

Minimum SYNC HIGH time |

VDD = 2.7V to 3.6V |

50 |

ns |

|

VDD = 3.6V to 5.5V |

33 |

||||

|

|

|

|||

t9 |

24th SCLK falling edge to SYNC falling edge |

VDD = 2.7V to 5.5V |

100 |

ns |

(1)All input signals are specified with tR = tF = 5ns (10% to 90% of VDD) and timed from a voltage level of (VIL + VIH)/2.

(2)See Serial Write Operation Timing Diagram.

(3)Maximum SCLK frequency is 30MHz at VDD = 3.6V to 5.5V and 20MHz at VDD = 2.7V to 3.6V.

Submit Documentation Feedback |

5 |

DAC8550

www.ti.com

SLAS476D – MARCH 2006 – REVISED OCTOBER 2006

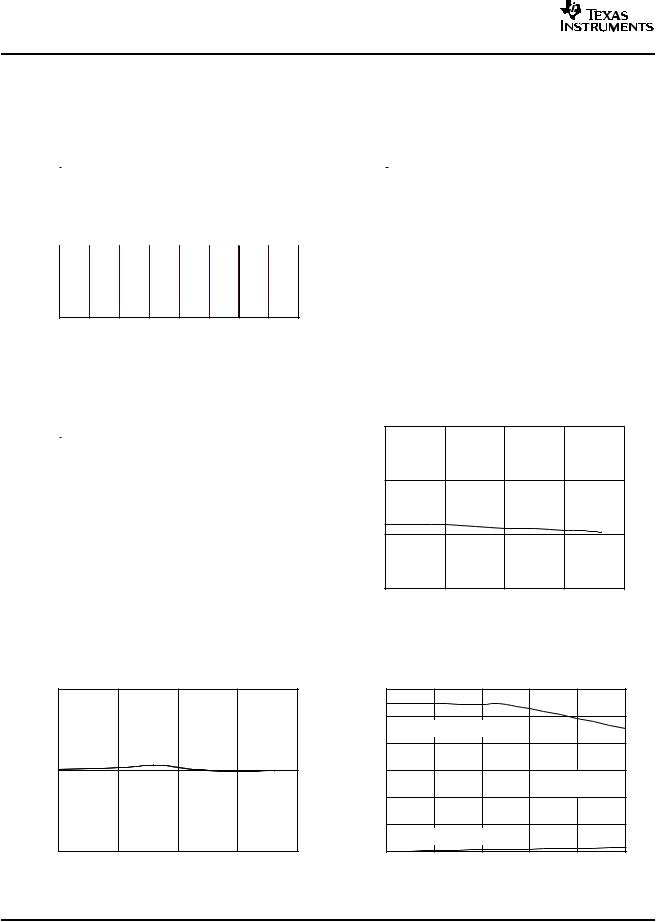

TYPICAL CHARACTERISTICS: VDD = 5 V

At TA = +25°C, unless otherwise noted.

DLE(LSB) LE(LSB)

|

|

|

LINEARITY ERROR AND |

||||||

|

|

DIFFERENTIAL LINEARITY ERROR |

|||||||

|

|

vs DIGITAL INPUT CODE (-40°C) |

|||||||

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

VDD = 5V, VREF = 4.99V |

|

|

|

|

|

|||

|

|

|

|

|

|||||

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

−2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

−4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

−6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

−0.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

−1.0

08192 16384 24576 32768 40960 49152 57344 65536

Digital Input Code

DLE(LSB) LE(LSB)

|

|

|

LINEARITY ERROR AND |

||||||

|

|

DIFFERENTIAL LINEARITY ERROR |

|||||||

|

|

vs DIGITAL INPUT CODE (+25°C) |

|||||||

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

VDD = 5V, VREF = 4.99V |

|

|

|

|

|

|||

|

|

|

|

|

|||||

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

−2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

−4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

−6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

−0.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

−1.0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

08192 16384 24576 32768 40960 49152 57344 65536

Digital Input Code

Figure 1. |

Figure 2. |

|

|

|

|

LINEARITY ERROR AND |

||||||

|

|

|

DIFFERENTIAL LINEARITY ERROR |

|||||||

|

|

|

vs DIGITAL INPUT CODE (+105°C) |

|||||||

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LE(LSB) |

4 |

VDD = 5V, VREF = 4.99V |

|

|

|

|

|

|||

|

|

|

|

|

||||||

−2 |

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

−4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

−6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DLE(LSB) |

1.0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

0.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

−0.5 |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

−1.0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

08192 16384 24576 32768 40960 49152 57344 65536

Digital Input Code

Figure 3.

FULL-SCALE ERROR vs TEMPERATURE

|

0 |

|

|

|

|

|

VDD = 5V |

|

|

|

|

|

VREF = 4.99V |

|

|

|

|

Error(mV) |

−5 |

|

|

|

|

|

|

|

|

|

|

|

−10 |

|

|

|

|

|

−40 |

0 |

40 |

80 |

120 |

|

|

|

Temperature (°C) |

|

|

Figure 5.

ZERO-SCALE ERROR vs TEMPERATURE

10 |

|

|

|

|

VDD = 5V |

|

|

|

|

VREF = 4.99V |

|

|

|

|

5 |

|

|

|

|

Error(mV) |

|

|

|

|

0 |

|

|

|

|

−5 |

|

|

|

|

−40 |

0 |

40 |

80 |

120 |

|

|

Temperature (°C) |

|

|

Figure 4.

SOURCE AND SINK CURRENT CAPABILITY

|

6 |

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

DAC Loaded with FFFFh |

|

|

|

|

(mV) |

4 |

|

|

|

|

|

3 |

|

|

|

|

|

|

OUT |

|

|

|

VDD = 5.5V |

|

|

|

|

|

|

|

||

V |

|

|

|

|

VREF = VDD − 10mV |

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

DAC Loaded with 0000h |

|

|

|

|

|

0 |

|

|

|

|

|

|

0 |

2 |

4 |

6 |

8 |

10 |

|

|

|

I(SOURCE/SINK) (mA) |

|

||

Figure 6.

6 |

Submit Documentation Feedback |

DAC8550

www.ti.com

SLAS476D – MARCH 2006 – REVISED OCTOBER 2006

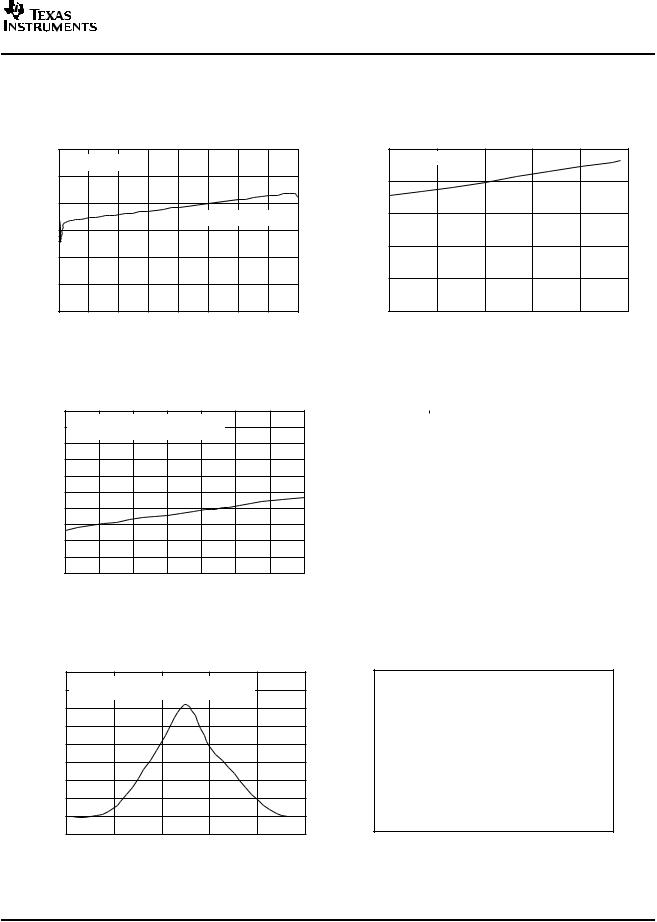

TYPICAL CHARACTERISTICS: VDD = 5 V (continued)

At TA = +25°C, unless otherwise noted.

SUPPLY CURRENT vs DIGITAL INPUT CODE

|

300 |

|

|

|

|

|

|

|

|

|

VDD = VREF = 5V |

|

|

|

|

|

|

|

250 |

|

|

|

|

|

|

|

|

200 |

|

|

|

|

|

|

|

A) |

|

|

|

Reference Current Included |

||||

( |

150 |

|

|

|

|

|

|

|

DD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

|

|

|

|

|

|

|

|

|

100 |

|

|

|

|

|

|

|

|

50 |

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

0 |

8192 |

16384 |

24576 32768 |

40960 |

49152 |

57344 |

65536 |

|

|

|

|

Digital Input Code |

|

|

|

|

Figure 7.

SUPPLY CURRENT vs SUPPLY VOLTAGE

300

280VREF = VDD

Reference Current Included, No Load

|

260 |

|

|

|

|

|

|

|

|

|

240 |

|

|

|

|

|

|

|

|

( A) |

220 |

|

|

|

|

|

|

|

|

200 |

|

|

|

|

|

|

|

|

|

DD |

|

|

|

|

|

|

|

|

|

180 |

|

|

|

|

|

|

|

|

|

I |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

160 |

|

|

|

|

|

|

|

|

|

140 |

|

|

|

|

|

|

|

|

|

120 |

|

|

|

|

|

|

|

|

|

100 |

|

|

|

|

|

|

|

|

|

|

2.7 |

3.1 |

3.5 |

3.9 |

4.3 |

4.7 |

5.1 |

5.5 |

|

|

|

|

|

VDD (V) |

|

|

|

|

|

|

|

|

|

Figure 9. |

|

|

|

|

|

|

|

|

SUPPLY CURRENT |

|

|

|

||

|

|

|

|

vs LOGIC INPUT VOLTAGE |

|

|

|||

|

1800 |

|

|

|

|

|

|

|

|

|

1600 |

TA = 25°C, SCL Input (all other inputs = GND) |

|

|

|||||

|

VDD |

= VREF = 5.5V |

|

|

|

|

|

||

|

|

|

|

|

|

|

|||

|

1400 |

|

|

|

|

|

|

|

|

|

1200 |

|

|

|

|

|

|

|

|

A) |

1000 |

|

|

|

|

|

|

|

|

( |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DD |

800 |

|

|

|

|

|

|

|

|

I |

|

|

|

|

|

|

|

|

|

|

600 |

|

|

|

|

|

|

|

|

|

400 |

|

|

|

|

|

|

|

|

|

200 |

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

2 |

3 |

|

4 |

5 |

|

|

|

|

|

VLOGIC (V) |

|

|

|

|

Figure 11.

POWER-SUPPLY CURRENT vs TEMPERATURE

|

250 |

|

|

|

|

|

|

VREF = VDD = 5V |

|

|

|

|

|

|

200 |

|

|

|

|

|

(µA) |

150 |

|

|

|

|

|

|

|

|

|

|

|

|

DD |

|

|

|

|

|

|

I |

100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

50 |

|

|

|

|

|

|

0 |

|

|

|

|

|

|

−40 |

−10 |

20 |

50 |

80 |

110 |

|

|

|

Temperature (°C) |

|

|

|

Figure 8.

POWER-DOWN CURRENT vs SUPPLY VOLTAGE

|

1.0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VREF = VDD |

|

|

|

|

|

|

|

|

|

|

||

A) |

0.8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

( |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DownCurrent |

0.6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Power- |

0.4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

0.2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2.7 |

3.1 |

3.5 |

4.3 |

4.7 |

5.1 |

5.5 |

||||||||

|

|

|

|

|

|

|

|

VDD (V) |

|

|

|

|

|

|

|

Figure 10.

FULL-SCALE SETTLING TIME: 5V RISING EDGE

Trigger Pulse 5V/div

VDD = 5V

VREF = 4.096V

From Code: D000

To Code: FFFF

Rising Edge

1V/div Zoomed Rising Edge

1mV/div

Time (2 s/div)

Figure 12.

Submit Documentation Feedback |

7 |

Loading...

Loading...