TelCom Semiconductor Inc TC14433EJG, TC14433ELI, TC14433COG, TC14433AEPG, TC14433EPG Datasheet

...

3-1/2 DIGIT A/D CONVERTERS

1

TC14433

TC14433A

FEATURES

■ Accuracy ...................±0.05% of Reading ±1 Count

■ Two Voltage Ranges .............1.999V and 199.9 mV

■ Up to 25 Conversions Per Second

■ ZIN > 1000M Ohms

■ Single Positive Voltage Reference

■ Auto-Polarity and Auto-Zero

■ Overrange and Underrange Signals Available

■ Operates in Auto-Ranging Circuits

■ Uses On-Chip System Clock or External Clock

■ Wide Supply Range .................... e.g., ±4.5V to ±8V

■ Package Available .................................. 24-Pin DIP

24-Pin CerDIP, 28-Pin SOIC and 28-Pin PLCC

APPLICATIONS

■ Portable Instruments

■ Digital Voltmeters

■ Digital Panel Meters

■ Digital Scales

■ Digital Thermometers

■ Remote A/D Sensing Systems

■ MPU Systems

■ See Application Notes 19 and 21

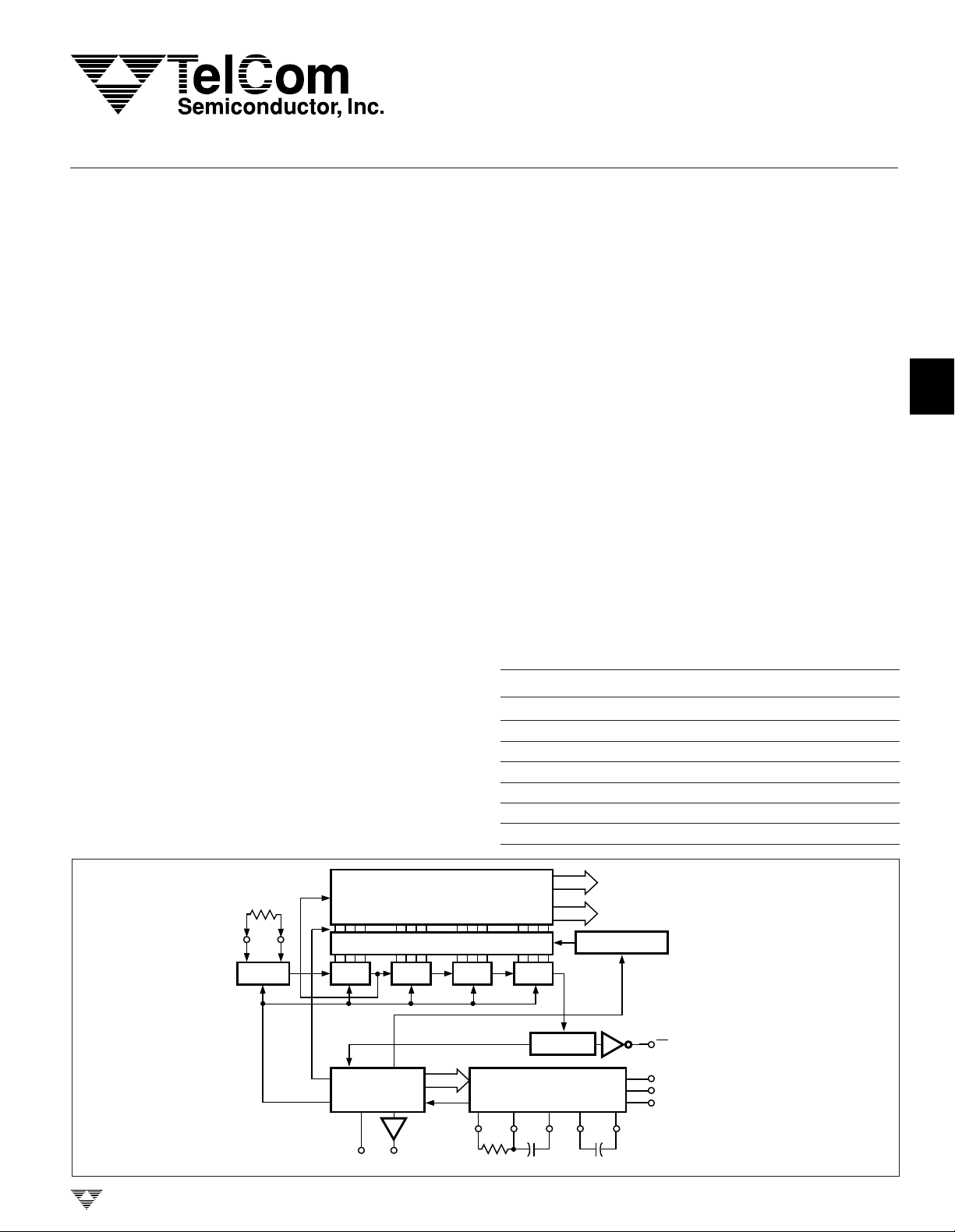

FUNCTIONAL BLOCK DIAGRAM

R

C

10

CLK111CLK0

MULTIPLEXER

LATCHES

GENERAL DESCRIPTION

The TC14433 is a low power, high-performance, monolithic CMOS 3-1/2 digit A/D converter. The TC14433 combines both analog and digital circuits on a single IC, thus

minimizing the number of external components. This dualslope A/D converter provides automatic polarity and zero

correction with the addition of two external resistors and two

capacitors. The full-scale voltage range of this ratiometric IC

extends from 199.9 millivolts to 1.999 volts. The TC14433

can operate over a wide range of power supply voltages,

including batteries and standard 5-volt supplies.

The TC14433 will interface with the TC7211A LCD

display driver.

The TC14433A features improved performance over

the industry standard TC14433. Rollover, which is the

measurement of identical positive and negative signals, is

guaranteed to have the same reading within one count for

the TC14433A. Power consumption of the TC14433A is

typically 4 mW, approximately one-half that of the industry

standard TC14433.

ORDERING INFORMATION

Part No. Package Temp.Range

TC14433AEJG 24-Pin CerDIP – 40°C to +85°C

TC14433AELI 28-Pin PLCC – 40°C to +85°C

TC14433AEPG 24-Pin Plastic DIP – 40°C to +85°C

TC14433COG 24-Pin SOIC 0°C to +70°C

TC14433EJG 24-Pin CerDIP – 40°C to +85°C

TC14433ELI 28-Pin PLCC – 40°C to +85°C

TC14433EPG 24-Pin Plastic DIP – 40°C to +85°C

20–23

Q

0–Q3

BCD DATA

16–19

–DS

DS

1

4

DIGIT STROBE

POLARITY DETECT

2

3

4

5

6

1'S

DISPLAY

UPDATE

TELCOM SEMICONDUCTOR, INC.

CONTROL

LOGIC

14

9

DU

EOC

10'S 100'S 1,000'SCLOCK

END OF

CONVERSION

OVERFLOW

CMOS

ANALOG

SUBSYSTEM

456

R

R1C1/

1

INTEGRATOR

C

1

78

CO1CO

OFFSET

7

15

OVERRANGE

OR

2

1

3

2

REFERENCE VOLTAGE

V

REF

ANALOG GROUND

V

AG

V

ANALOG INPUT

X

= PIN 24

V

DD

V

= PIN 13

SS

V

= PIN 12

EE

8

TC14433/A-6 10/21/96

3-127

TC14433

TC14433A

3-1/2 DIGIT A/D CONVERTERS

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage (VDD – VEE) ...................... – 0.5V to +18V

Voltage on Any Pin,

Reference to VEE.......................– 0.5V to (VDD + 0.5)

DC Current, Any Pin.............................................. ±10mA

Operating Temperature Range ...............– 40°C to +85°C

Power Dissipation (TA < 70°C)

SOIC................................................................940mW

CerDIP...............................................................1.45W

Storage Temperature Range ................– 65°C to +160°C

Lead Temperature (Soldering, 10 sec) .................+300°C

*This is a stress rating only and functional operation of the device at these

or any other conditions above those indicated in the operation sections of

the specifications is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

Plastic PLCC .......................................................1.0W

Plastic DIP.......................................................940mW

ELECTRICAL CHARACTERISTICS: V

= +5V, VEE = – 5V, C1 = 0.1µF (mylar), CO = 0.1µF, RC = 300kΩ, R1 =

DD

470kΩ @ V

= 2V, R1 = 27kΩ @ V

REF

= 200mV, unless otherwise specified.

REF

TA = +25°C– 40°C < TA < +85°C

Symbol Parameter Test Conditions Min Typ Max Min Typ Max Unit

Analog Input

SYE Rollover Error (Positive 200mV Full Scale V

and Negative Full –V

= +V

IN

IN

IN

Scale Symmetry

NL Linearity Output V

Reading (Note 1) V

SOR Stability Output Reading VX = 1.99V, V

(Note 2) VX = 199mV, V

ZOR Zero Output Reading VX = 0V, V

I

IN

Bias Current:

= 2V – 0.05 +0.05 +0.05 — — — %rdg

REF

= 200mV – 1 count — +1 count — — —

REF

= 2V — — 2 — — — LSD

REF

= 200mV — — 3 — — —

REF

= 2V — 0 0 — — — LSD

REF

Analog Input — ±20 ±100 — — — pA

Reference Input — ±20 ±100 — — —

Analog Ground — ±20 ±500 — — —

CMRR Common-Mode Rejection V

= 1.4V, V

X

= 2V, — 65 — — — — dB

REF

fOC = 32kHz

Digital

V

OL

Output Voltage VSS = 0V, "0" Level — 0 0.05 — — 0.05 V

Pins 14 to 23 (Note 3) VSS = – 5V, "0" Level — – 5 –4.95 — — – 4.95

V

OH

Output Voltage VSS = 0V, "1" Level 4.95 5 — 4.95 — — V

Pins 14 to 23 (Note 3) VSS = – 5V, "1" Level 4.95 5 — 4.95 — —

I

OH

Output Current VSS = 0V, VOH = 4.6V Source – 0.2 – 0.36 — – 0.14 — — mA

Pins 14 to 23 VSS = – 5V, VOH = 5V Source – 0.5 – 0.9 — – 0.35 — —

I

OL

Output Current VSS = 0V, VOL = 0.4V Sink 0.51 0.88 — 0.36 — — mA

Pins 14 to 23 VSS = – 5V, VOL = – 4.5V Sink 1.3 2.25 — 0.9 — —

f

CLK

Clock Frequency RC = 300kΩ — 66 — ———kHz

IDUInput Current – DU —

Power

I

Q

Quiescent Current VDD to VEE, ISS = 0, 14433A:

= 5, VEE = – 5 — 0.4 2 — — 3.7 mA

V

DD

= 8, VEE = –8 — 1.4 4 — — 7.4

V

DD

V

to VEE, ISS = 0, 14433:

DD

= 5, VEE = – 5 — 0.9 2 — — 3.7

V

DD

VDD = 8, VEE = –8 — 1.8 4 — — 7.4

PSRR Supply Rejection

VDD to VEE, ISS = 0, V

REF

= 2V

VDD = 5, VEE = – 5

–1 — +1 — — — Counts

±0.00001

±0.3 — — ±1 µA

— 0.5 — — — — mV/V

3-128

TELCOM SEMICONDUCTOR, INC.

3-1/2 DIGIT A/D CONVERTERS

TC14433

TC14433A

NOTES: 1. Accuracy — The accuracy of the meter at full-scale is the accuracy of the setting of the reference voltage. Zero is recalculated during

each conversion cycle. The meaningful specification is linearity. In other words, the deviation from correct reading for all inputs other

than positive full-scale and zero is defined as the linearity specification.

2. The LSD stability for 200mV scale is defined as the range that the LSD will occupy 95% of the time.

3. Pin numbers refer to 24-pin DIP.

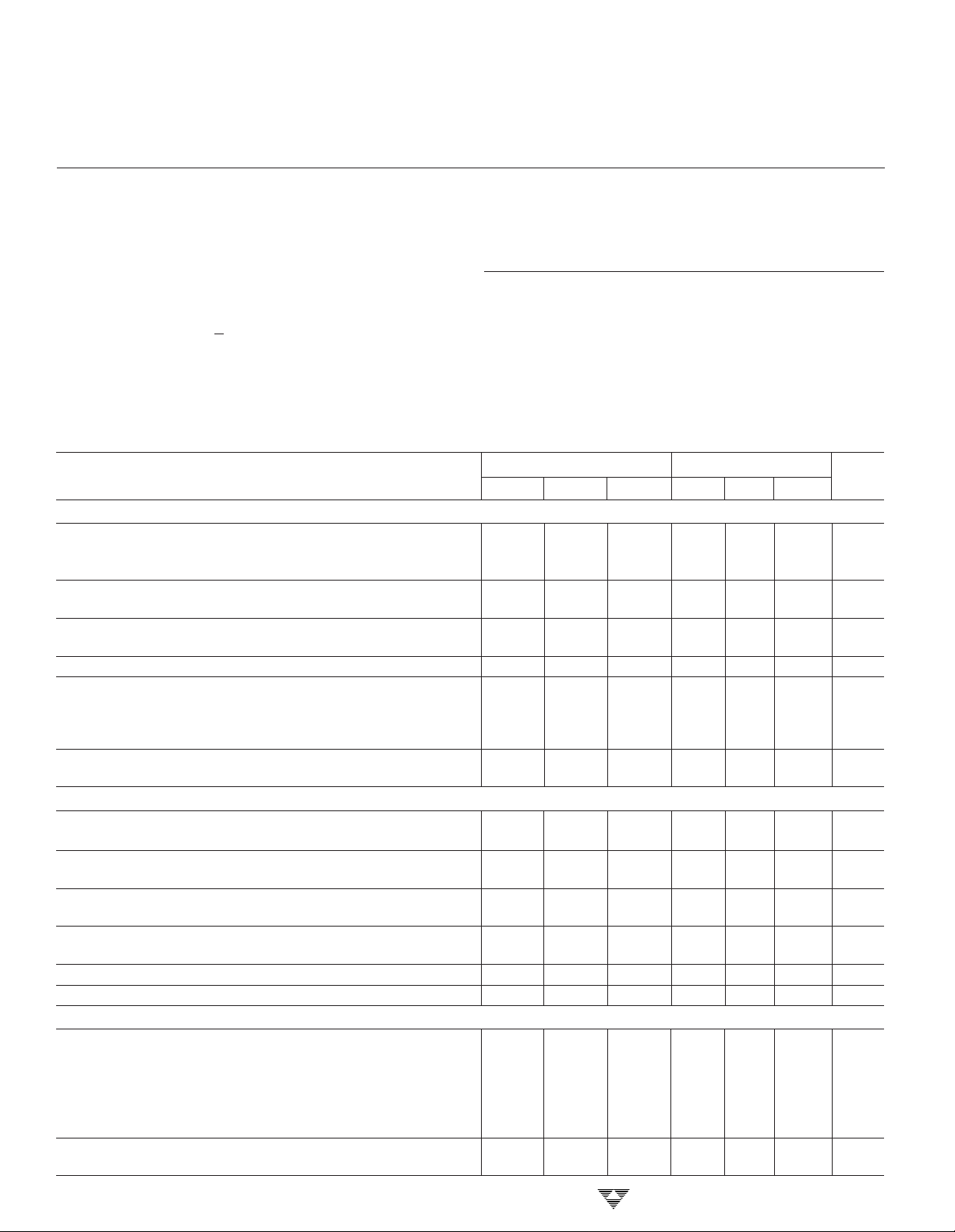

PIN CONFIGURATIONS

1

2

V

AG

V

REF

V

R

R1/C

C

CO

CO

DU

CLK1

CLK0

V

EE

1

2

3

X

4

1

5

1

6

1

TC14433AEPG

TC14433EPG

7

1

TC14433AEJG

8

2

TC14433EJG

9

10

11

12

(PDIP)

(CerDIP)

24

V

DD

23

Q

3

22

Q

2

Q

21

1

VDDQ

SS

3

EOC

R1/C

CLK1

CLK0

2

Q

OR

Q

20

0

DS

19

1

DS

18

2

17

DS

3

16

DS

4

15

OR

14

EOC

V

13

SS

X

REF

V

4 3 2 1 27 2628

R

5

1

R1/C

6

1

C

7

1

8

NC NC

CO

9

1

CO

10

2

11

DU

12 13 14 15 17 18

CLK1

AG

V

NC

V

TC14433AELI

TC14433ELI

(PLCC)

16

EE

NC

V

CLK0

V

V

V

REF

CO

CO

V

25

24

23

22

21

20

19

AG

V

R

C

DU

EE

X

1

1

1

1

2

Q

Q

DS

DS

DS

DS

1

2

3

4

5

6

7

8

9

10

11

12

1

0

1

2

3

4

TC14433COG

(SOIC)

24

23

22

21

20

19

18

17

16

15

14

13

V

DD

Q

3

Q

2

Q

1

Q

0

DS

DS

DS

DS

OR

EOC

V

SS

3

1

2

3

4

4

5

6

TELCOM SEMICONDUCTOR, INC.

7

8

3-129

3-1/2 DIGIT A/D CONVERTERS

TC14433

TC14433A

PIN DESCRIPTIONS

Pin No. Pin No. Pin No.

24-Pin 24-Pin 28-Pin

PDIP/CerDip SOIC PLCC Symbol Description

112V

223V

AG

REF

334V

445R

556R

/C

1

667C

779CO

8810CO

9 9 11 DU Display update input pin — When DU is connected to the EOC output every

10 10 12 CLK

11 11 13 CLK

12 12 14 V

13 13 16 V

EE

SS

14 14 17 EOC End of conversion output generates a pulse at the end of each conversion

15 15 18 OR Overrange pin — Normally this pin is set high. When V

This is the analog ground; it has a high input impedance — This pin

determines the reference level for the unknown input voltage (V

reference voltage (V

REF

).

Reference voltage — Full-scale output is equal to the voltage applied to

. Therefore, full-scale voltage of 1.999V requires 2V reference and

V

REF

199.9 mV full-scale requires a 200 mV reference. V

reset also. When switched to V

, the system is reset to the beginning of

EE

functions as system

REF

the conversion cycle.

The unknown input voltage (VX) is measured as a ratio of the reference

X

voltage (V

These pins are for external components used for the integration function in

1

) in a ratiometric A/D conversion.

REF

the dual slope conversion. Typical values are 0.1 µF (mylar) capacitor for C1.

R1 = 470 kW (resistor) for 2V full-scale.

1

R

1

= 27 kW (resistor) for 200 mV full-scale. Clock frequency of 66 kHz gives

1

250 msec conversion time. See equation below for calculation of integrator

component values.

These pins are used for connecting the offset correction capacitor. The

1

recommended value is 0.1 µF.

2

conversion is displayed. New data will be strobed into the output latches

during the conversion cycle if a positive edge is received on DU prior to the

ramp-down cycle. When this pin is driven from an external source, the

voltage should be referenced to VSS.

Clock input pins — The TC14433 has its own oscillator system clock.

1

Connecting a single resistor between CLK1 and CLK0 sets the clock frequency.

A crystal or OC circuit may be inserted in lieu of a resistor for improved

0

, the clock input, can be driven from an external clock source,

CLK

1

which need only have standard CMOS output drive. This pin is referenced to

VEE for external clock inputs. A 300 kW resistor yields a clock frequency of

about 66 kHz. (See typical characteristic curves; see Figure 9 for alternate

circuits.)

Negative power current — Connection pin for the most negative supply. Please

note the current for the output drive circuit is returned through V

supply current is 0.8 mA.

Negative power supply for output circuitry — This pin sets the low voltage level

for the output pins (BCD, Digit Selects, EOC, OR). When connected to analog

ground, the output voltage is from analog ground to VDD. If connected to VEE,

the output swing is from V

to VDD. The recommended operating range for

EE

VSS is between the VDD –3 volts and VEE.

cycle. This generated pulse width is equal to one-half the period of the system

clock.

exceeds V

X

pin is low.

) and the

X

. Typical

SS

REF

the OR

3-130

TELCOM SEMICONDUCTOR, INC.

3-1/2 DIGIT A/D CONVERTERS

PIN DESCRIPTIONS (Cont.)

Pin No. Pin No. Pin No.

24-Pin 24-Pin 28-Pin

PDIP/CerDip SOIC PLCC Symbol Description

16 16 19 DS

17 17 20 DS

18 18 21 DS

19 19 23 DS

20 20 24 Q

21 21 25 Q

22 22 26 Q

23 23 28 Q

24 24 28 V

8,15, 22 NC Not Used.

DD

Digit select pins — The digit select output goes high when the respective digit

4

is selected. The MSD (1/2 digit) turns on immediately after an EOC pulse.

The remaining digits turn on in sequence from MSD to LSD.

3

To ensure that the BCD data has settled, an inter-digit blanking time of two

2

clock periods is included.

Clock frequency divided by 80 equals multiplex rate. For example, a system

1

clock of 60 kHz gives a multiplex rate of 0.8 kHz.

See Figure 12 for digit select timing diagram.

0

BCD data output pins — Multiplexed BCD outputs contain three full digits of

1

information during digit select DS2, DS3, DS4.

During DS1, the 1/2 digit, overrange, underrange and polarity information is

2

available.

Refer to truth table.

3

Positive power supply — This is the most positive power supply pin.

1

TC14433

TC14433A

2

3

4

CIRCUIT DESCRIPTION

The TC14433 CMOS IC becomes a modified dualslope A/D with a minimum of external components. This IC

has the customary CMOS digital logic circuitry, as well as

CMOS analog circuitry. It provides the user with digital

functions (such as counters, latches, multiplexers) and

analog functions (such as operational amplifiers and comparators) on a single chip.

Features of this system include auto-zero, high input

impedances and auto-polarity. Low power consumption

and a wide range of power supply voltages are also advantages of this CMOS device. The system's auto-zero function

compensates for the offset voltage of the internal amplifiers

and comparators. In this "ratiometric system," the output

reading is the ratio of the unknown voltage to the reference

voltage, where a ratio of 1 is equal to the maximum count of

1999. It takes approximately 16,000 clock periods to complete one conversion cycle. Each conversion cycle may be

divided into 6 segments. Figure 7 shows the conversion

cycle in 6 segments for both positive and negative inputs.

Segment 1 — The offset capacitor (CO), which com-

pensates for the input offset voltages of the buffer and

integrator amplifiers, is charged during this period. However, the integrator capacitor is shorted. This segment

requires 4000 clock periods.

Segment 2 — During this segment, the integrator

output decreases to the comparator threshold voltage. At

this time, a number of counts equivalent to the input offset

voltage of the comparator is stored in the offset latches for

later use in the auto-zero process. The time for this segment

is variable and less than 800 clock periods.

START

TIME

SEGMENT

NUMBER

BUFFER

–

V

+

X

Figure 8. Equivalent Circuit Diagrams of the Analog

Section During Segment 4 of the Timing Cycle

1

Figure 7. Integrator Waveforms at Pin 6

3

2

R

1

45

V

X

C

INTEGRATOR

–

+

END

6

V

X

TYPICAL

POSITIVE

INPUT

VOLTAGE

TYPICAL

NEGATIVE

INPUT

VOLTAGE

1

COMPARATOR

+

–

5

6

7

8

TELCOM SEMICONDUCTOR, INC.

3-131

TC14433

TC14433A

3-1/2 DIGIT A/D CONVERTERS

(A) Crystal Oscillator Circuit

10

CLK

1

18M

C

1

47k

C

2

10 pF < C AND C < 200 pF

TC14433

11

CLK

0

1

2

Figure 9. Alternate Oscillator Circuits

Segment 3 — This segment of the conversion cycle is

the same as Segment 1.

Segment 4 — Segment 4 is an up-going ramp cycle with

the unknown input voltage (VX) as the input to the integrator.

Figure 8 shows the equivalent configuration of the analog

section of the TC14433. The actual configuration of the

analog section is dependent upon the polarity of the input

voltage during the previous conversion cycle.

Segment 5 — This segment is a down-going ramp

TC04

+5V

0.1 µF

V

*R

= 470k FOR 2V RANGEΩ

1

R

= 27k FOR 200mV RANGEΩ

1

**MYLAR CAPACITOR

1

3

x

2

µF

0.1

0.1 µF**

0.1 µF

300k

R

*

R

1

20K

C

11 10 2 12 24

3

1

4

5

TC14433

6

7

8

15

19 18 17 16

DS

DS

1

2

DS

23

22

21

20

13

9

14

DS

3

+5V

0.1 0.1 µF

–5V

14013B

–5V

4

5

D

3

C

4

9

D

11

C

10

714

(B) LC Oscillator Circuit

10

CLK

1

L

C

FOR L = 5 mH AND C = 0.01 µF, f 32 kHz

C

TC14433

11

CLK

0

1

=

2/LC

f =

p

2

≅

period with the reference voltage as the input to the integrator. Segment 5 of the conversion cycle has a time equal to

the number of counts stored in the offset storage latches

during Segment 2. As a result, the system zeros automatically.

Segment 6 — This is an extension of Segment 5. The

time period for this portion is 4000 clock periods. The results

of the A/D conversion cycle are determined in this portion of

the conversion cycle.

–5V

+5V

7

6

5

4

3

2

1

1413

–5V–5V

–5V

MPS-A12

–5V

51k

+5V

50 µF 0.1 µF

–5V

10

11

12

13

14

15

16

MINUS SIGN

PLUS SIGN

COMMON

ANODE LED

DISPLAY

MPS-A12

SEGMENT

RESISTORS

150 (7)

Ω

Ω

200

Ω

110

(4)

fgedcba

S

R

S

R

–5V

6

Q

Q

Q

Q

1

4

2

3

5

4543B

8

67

1

2

8

13

12

+5V

+5V

16

9

10

11

12

13

14

15

3-132

Figure 10. 3-1/2 Digit Voltmeter Common-Anode Displays, Flashing Overrange

TELCOM SEMICONDUCTOR, INC.

3-1/2 DIGIT A/D CONVERTERS

1

TC14433

TC14433A

TC04

+V

27k

20k

+V

14013B

D

C

R

14013B

D

C

RR

0.1 µF

C0

1C02

V

x

V

AG

V

REF

V

DDVSSVEE

–V

1/4

Q

Q

R

Q

Q

–V

+V

R

1

TC14433

EOC DU

14070B

1/4

14070B

470k

R1/C

RCR

1/2 DIGIT

PLUS

SIGN

MINUS

SIGN

0.1 µF

1

300k

C

1

DS

4

DS

3

DS

2

DS

1

Q

0

Q

1

Q

2

Q

3

C

BIDCBAPhLD

14543B

gfedcba

BIDCBAPhLD

+V

–V

14543B

gfedcba

14070B 1/4

+V

+V

–V

+V

BIDCBAPhLD

14543B

gfedcba

–V

C

R

14024B

+V

–V

2

3

4

5

Figure 11. 3-1/2 Digit Voltmeter with LCD Display

EOC 1/2 CLOCK CYCLE

DS

1/2 DIGIT

(MSD)

DS

DS

DS

(LSD)

1

2

3

4

2 CLOCK

CYCLES

18 CLOCK CYCLES

TELCOM SEMICONDUCTOR, INC.

Figure 12. Digit Select Timing Diagram

≈

16,400 CLOCK CYCLES

BETWEEN EOC PULSES

6

7

8

3-133

TC14433

TC14433A

3-1/2 DIGIT A/D CONVERTERS

APPLICATIONS INFORMATION

Figure 10 is an example of a 3-1/2 digit voltmeter using

the TC14433 with common-anode displays. This system

requires a 2.5V reference. Full-scale may be adjusted to

1.999V or 199.9 mV. Input overrange is indicated by flashing

a display. This display uses LEDs with common anode digit

lines. Power supply for this system is shown as a dual ±5V

supply; however, the TC14433 will operate over a wide

voltage range (see recommended operating conditions,

page 2).

The circuit in Figure 11 shows a 3-1/2 digit LCD voltmeter. The 14024B provides the low frequency square wave

signal drive to the LCD backplane. Dual power supplies are

shown here; however, one supply may be used when VSS is

connected to VEE. In this case, VAG must be at least 2.8V

above VEE.

When only segments b and c of the decoder are connected to the 1/2 digit of the display, 4, 0, 7 and 3 appear as 1.

The overrange indication (Q3 = 0 and Q0 = 1) occurs

when the count is greater than 1999; e.g., 1.999V for a

reference of 2V. The underrange indication, useful for autoranging circuits, occurs when the count is less than 180; e.g.,

0.180V for a reference of 2V.

CAUTION

If the most significant digit is connected to a

display other than a "1" only, such as a full

digit display, segments other than b and c must

be disconnected. The BCD to 7-segment

decoder must blank on BCD inputs 1010 to 1111.

Figure 14 is an example of a 3-1/2 digit LED voltmeter

with a minimum of external components (only 11 additional

components). In this circuit, the 14511B provides the segment drive and the 75492 or 1413 provides sink for digit

current. Display is blanked during the overrange condition.

TRUTH TABLE

Coded Condition BCD to 7-Segment

of MSD Q3Q2Q1Q

0

+0 1 1 1 0 Blank

–0 1 0 1 0 Blank

+0 UR 1 1 1 1 Blank

–0 UR 1 0 1 1 Blank

+1 0 1 0 0 4–1 Hook up

–1 0 0 0 0 0–1 only

+1 OR 0 1 1 1 7–1 segments

–0 OR 0 0 1 1 3–1 b and c

NOTES: Q3 — 1/2 digit, low for "1", high for "0"

Q2 — Polarity: "1" = positive, "0" = negative

Q0 — Out of range condition exists if Q0 = 1. When used in

conjunction with Q3, the type of out of range condition is

indicated; i.e., Q3 = 0 → OR or Q3 = 1 → UR.

Decoding

to MSD

3-134

DS

DS

1

2

D

D1D2D

0

V

DD

POL 14042B C

Q

Q1Q2Q

0

D

0D1D2D3

V

DD

R 14175B C POL 14175B C

Q

Q1Q2Q

0

3

3

V

DD

3

MULTIPLEXED

BCD

V

D0D1D2D

C 14042B POL POL 14042B C C 14042B POL

Q0Q1Q2Q

D0D1D2D

Q0Q1Q2Q

Figure 13. Demultiplexing for TC14433 BCD Data

3

3

3

3

DD

V

DD

DS

DS

1

2

D0D1D2D

Q0Q1Q2Q

D0D1D2D

POL 14175B C POL 14175B C

Q0Q1Q2Q

DS

DS

3

4

V

DD

D0D1D2D

Q0Q1Q2Q

D0D1D2D

Q0Q1Q2Q

3

3

3

3

3

3

3

3

TELCOM SEMICONDUCTOR, INC.

V

DD

EOC

3-1/2 DIGIT A/D CONVERTERS

470k

0.1µF

R /C

R

1

+5V

V

X

27kΩ

TC04

For V = 2000V

REF

V : 1.999V full scale

For V = 200 mV

REF

V : 199.9 mV full scale

(change 470k to R = 27k

and decimal point position)

Peak digit current for an eight

displayed is 7 times the segment

current.

*To increase segment current

capability add two 75491 ICs

between 14511B and Resistor

Network. The use of the 1413

as digit driver increases digit

current capability over the 75492.

**V can range between –2.8 and

–11V.

100kΩ

INPUT

11 1 1 2

V

X

V

AG

DU

EOC

TC14433

V

REF

DS

DS

43 21

ALTERNATE OVERRANGE CIRCUIT

1/6

1/7 1413

0.1µF

CC0

C0

CLK1

CLK0

DS

DS

WITH SEPARATED LED

75492

OR

OR

V

V

V

Q

Q

Q

SS

DD

EE

300k

0

1

2

V

EE**

(MINUS)

+5V

MINUS

CONTROL

1

TC14433

TC14433A

2

RESISTOR

NETWORK

OR

INDIVIDUAL

A

B

C

D

I4511B

LT

LE

V

SS

B1

V

DD

+5V

a

b

c

d

e

f

g

R

M

RESISTOR*

R

R

3

DP

COMMON

CATHODE

LED DISPLAY

4

75492

OR

1413*

DIGIT DRIVERS

R

R

+5VOR

5

Figure 14. 3-1/2 Digit Voltmeter with Low Component Count Using Common Cathode Displays

TELCOM SEMICONDUCTOR, INC.

6

7

8

3-135

TC14433

TC14433A

TYPICAL CHARACTERISTICS

3-1/2 DIGIT A/D CONVERTERS

4

3

2

1

0

–1

–2

–3

(PLUS COUNT LESS MINUS COUNT)

–4

ROLLOVER ERROR (IN LSD) AT FULL-SCALE

5

4

3

2

— SINK CURRENT (mA)

1

D

I

0

01234 5

ROLLOVER ERROR IS THE DIFFERENCE

NOTE:

IN OUTPUT READING FOR THE SAME

ANALOG INPUT SWITCHED FROM

POSITIVE TO NEGATIVE.

–3 –2 –1 0 1

(IV I–IV I)

DD

— DRAIN TO SOURCE VOLTAGE (Vdc)

V

DS

— SUPPLY VOLTAGE SKEW (V)

EE

234

–40°C

+25°C

+85°C

4

3

2

1

— QUIESCENT CURRENT (mA)I

Q

–40 –20 0 20 40 60 80 100

0

–3

–2

–1

— SINK CURRENT (mA)

D

I

0

0–1–2–3–4–5

V

V = –8V

EE

V = +8V

DD

V = –5V

EE

V = +5V

DD

— TEMPERATURE (°C)

T

A

— DRAIN TO SOURCE VOLTAGE (Vdc)

DS

–40°C

–25°C

–85°C

3-136

NOTE: ±5% TYPICAL VARIATION OVER

1M

100k

— CLOCK FREQUENCY (Hz)

CLK

I

10k

10 kΩ 100 kΩ 1 MΩ

— CLOCK FREQUENCY RESISTOR

R

C

SUPPLY VOLTAGES RANGE OF

±4.5V TO ±8V.

CONVERSION RATE =

MULTIPLEX RATE =

4

3

2

1

0

–1

–2

–3

— CLOCK FREQUENCY (% CHANGE)

–4

CLK

I

CLOCK FREQUENCY

16,400

CLOCK FREQUENCY

80

±5V SUPPLY

±8V SUPPLY

NORMALIZED AT 25°C

–40 –20 0 20 40 60 80

±1.5%

— TEMPERATURE (°C)

T

A

TELCOM SEMICONDUCTOR, INC.

Loading...

Loading...