ST uPSD3312D-40T6, uPSD3312DV-40T6, uPSD3333D-40T6, uPSD3333DV-40T6, uPSD3333D-40U6 User Manual

...

UPSD3312D-40T6T

uPSD33xx

Turbo Series

Fast 8032 MCU with Programmable Logic

PRELIMINARY DATA

FEATURES SUMMARY

■FAST 8-BIT TURBO 8032 MCU, 40MHz

–Advanced core, 4-clocks per instruction

–10 MIPs peak performance at 40MHz (5V)

–JTAG Debug and In-System Programming

–Branch Cache & 6 instruction Prefetch Queue

–Dual XDATA pointers with auto incr & decr

–Compatible with 3rd party 8051 tools

■DUAL FLASH MEMORIES WITH MEMORY MANAGEMENT

–Place either memory into 8032 program address space or data address space

–READ-while-WRITE operation for InApplication Programming and EEPROM emulation

–Single voltage program and erase

–100K guaranteed erase cycles, 15-year retention

■CLOCK, RESET, AND SUPPLY MANAGEMENT

–SRAM is Battery Backup capable

–Flexible 8-level CPU clock divider register

–Normal, Idle, and Power Down Modes

–Power-on and Low Voltage reset supervisor

–Programmable Watchdog Timer

■PROGRAMMABLE LOGIC, GENERAL PURPOSE

–16 macrocells

–Create shifters, state machines, chipselects, glue-logic to keypads, panels, LCDs, others

■COMMUNICATION INTERFACES

–I2C Master/Slave controller, 833KHz

–SPI Master controller, 10MHz

–Two UARTs with independent baud rate

–IrDA protocol support up to 115K baud

–Up to 46 I/O, 5V tolerant on 3.3V uPSD33xxV

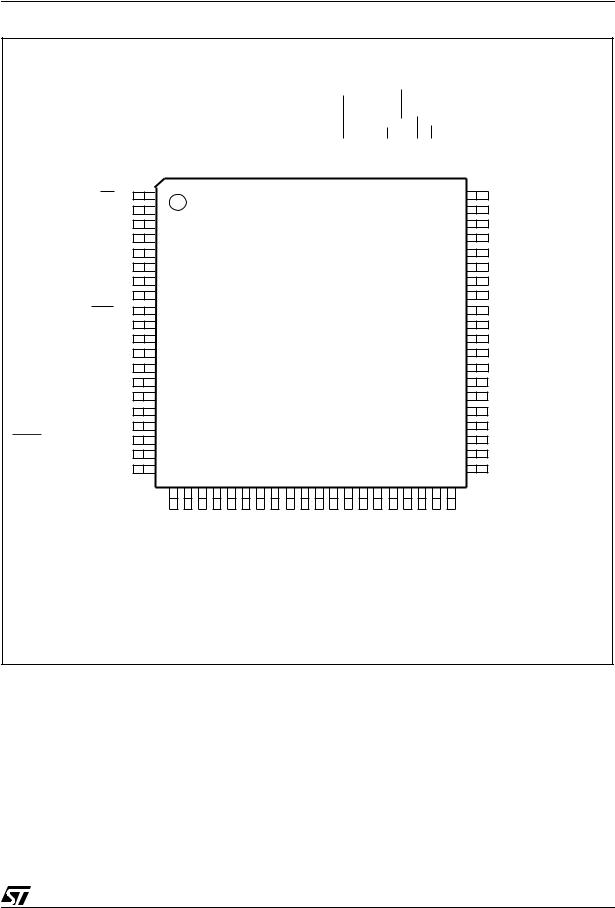

Figure 1. Packages

TQFP52 (T)

52-lead, Thin,

Quad, Flat

TQFP80 (U)

80-lead, Thin,

Quad, Flat

■A/D CONVERTER

–Eight Channels, 10-bit resolution, 6µs

■TIMERS AND INTERRUPTS

–Three 8032 standard 16-bit timers

–Programmable Counter Array (PCA), six 16-bit modules for PWM, CAPCOM, and timers

–8/10/16-bit PWM operation

–11 Interrupt sources with two external interrupt pins

■OPERATING VOLTAGE SOURCE (±10%)

–5V devices use both 5.0V and 3.3V sources

–3.3V devices use only 3.3V source

January 2005 |

1/231 |

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

uPSD33xx

Table 1. Device Summary

|

1st |

2nd |

SRAM |

|

8032 |

VCC |

VDD |

|

|

|

Part Number |

Flash |

Flash |

GPIO |

Pkg. |

Temp. |

|||||

(bytes) |

Bus |

|||||||||

|

(bytes) |

(bytes) |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

uPSD3312D-40T6 |

64K |

16K |

2K |

37 |

No |

3.3V |

5.0V |

TQFP52 |

–40°C to 85°C |

|

|

|

|

|

|

|

|

|

|

|

|

uPSD3312DV-40T6 |

64K |

16K |

2K |

37 |

No |

3.3V |

3.3V |

TQFP52 |

–40°C to 85°C |

|

|

|

|

|

|

|

|

|

|

|

|

uPSD3333D-40T6 |

128K |

32K |

8K |

37 |

No |

3.3V |

5.0V |

TQFP52 |

–40°C to 85°C |

|

|

|

|

|

|

|

|

|

|

|

|

uPSD3333DV-40T6 |

128K |

32K |

8K |

37 |

No |

3.3V |

3.3V |

TQFP52 |

–40°C to 85°C |

|

|

|

|

|

|

|

|

|

|

|

|

uPSD3333D-40U6 |

128K |

32K |

8K |

46 |

Yes |

3.3V |

5.0V |

TQFP80 |

–40°C to 85°C |

|

|

|

|

|

|

|

|

|

|

|

|

uPSD3333DV-40U6 |

128K |

32K |

8K |

46 |

Yes |

3.3V |

3.3V |

TQFP80 |

–40°C to 85°C |

|

|

|

|

|

|

|

|

|

|

|

|

uPSD3334D-40U6 |

256K |

32K |

8K |

46 |

Yes |

3.3V |

5.0V |

TQFP80 |

–40°C to 85°C |

|

|

|

|

|

|

|

|

|

|

|

|

uPSD3334DV-40U6 |

256K |

32K |

8K |

46 |

Yes |

3.3V |

3.3V |

TQFP80 |

–40°C to 85°C |

|

|

|

|

|

|

|

|

|

|

|

|

uPSD3354D-40T6 |

256K |

32K |

32K |

37 |

No |

3.3V |

5.0V |

TQFP52 |

–40°C to 85°C |

|

|

|

|

|

|

|

|

|

|

|

|

uPSD3354DV-40T6 |

256K |

32K |

32K |

37 |

No |

3.3V |

3.3V |

TQFP52 |

–40°C to 85°C |

|

|

|

|

|

|

|

|

|

|

|

|

uPSD3354D-40U6 |

256K |

32K |

32K |

46 |

Yes |

3.3V |

5.0V |

TQFP80 |

–40°C to 85°C |

|

|

|

|

|

|

|

|

|

|

|

|

uPSD3354DV-40U6 |

256K |

32K |

32K |

46 |

Yes |

3.3V |

3.3V |

TQFP80 |

–40°C to 85°C |

|

|

|

|

|

|

|

|

|

|

|

2/231

uPSD33xx

TABLE OF CONTENTS

FEATURES SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

SUMMARY DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

PIN DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

uPSD33xx HARDWARE DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

MEMORY ORGANIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Internal Memory (MCU Module, Standard 8032 Memory: DATA, IDATA, SFR) . . . . . . . . . . . . 16 External Memory (PSD Module: Program memory, Data memory). . . . . . . . . . . . . . . . . . . . . . 16

8032 MCU CORE PERFORMANCE ENHANCEMENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Pre-Fetch Queue (PFQ) and Branch Cache (BC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

PFQ Example, Multi-cycle Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Aggregate Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

MCU MODULE DISCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

8032 MCU REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Stack Pointer (SP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Data Pointer (DPTR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Program Counter (PC). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Accumulator (ACC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

B Register (B). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

General Purpose Registers (R0 - R7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Program Status Word (PSW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

SPECIAL FUNCTION REGISTERS (SFR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

8032 ADDRESSING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Register Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Direct Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Register Indirect Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Immediate Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

External Direct Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

External Indirect Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Indexed Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Relative Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Absolute Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Long Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Bit Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

uPSD33xx INSTRUCTION SET SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3/231

uPSD33xx

DUAL DATA POINTERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Data Pointer Control Register, DPTC (85h) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37 Data Pointer Mode Register, DPTM (86h) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

DEBUG UNIT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

INTERRUPT SYSTEM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Individual Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

MCU CLOCK GENERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

MCU_CLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46 PERIPH_CLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

POWER SAVING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Idle Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Power-down Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Reduced Frequency Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

OSCILLATOR AND EXTERNAL COMPONENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

I/O PORTS of MCU MODULE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

MCU Port Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

MCU BUS INTERFACE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Bus Read Cycles (PSEN or RD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62 Bus Write Cycles (WR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62 Controlling the PFQ and BC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

SUPERVISORY FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

External Reset Input Pin, RESET_IN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Low VCC Voltage Detect, LVD. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Power-up Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

JTAG Debug Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Watchdog Timer, WDT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

STANDARD 8032 TIMER/COUNTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Standard Timer SFRs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Clock Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

SFR, TCON . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

SFR, TMOD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Timer 0 and Timer 1 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Timer 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

SERIAL UART INTERFACES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

UART Operation Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

4/231

uPSD33xx

Serial Port Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82 UART Baud Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84 More About UART Mode 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85 More About UART Mode 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87 More About UART Modes 2 and 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

IrDA INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Pulse Width Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

I2C INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

I2C Interface Main Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Communication Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Bus Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Clock Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

General Call Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Serial I/O Engine (SIOE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

I2C Interface Control Register (S1CON) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

I2C Interface Status Register (S1STA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

I2C Data Shift Register (S1DAT). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

I2C Address Register (S1ADR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

I2C START Sample Setting (S1SETUP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

I2C Operating Sequences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

SPI (SYNCHRONOUS PERIPHERAL INTERFACE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

SPI Bus Features and Communication Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Full-Duplex Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Bus-Level Activity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

SPI SFR Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

SPI Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Dynamic Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

ANALOG-TO-DIGITAL CONVERTOR (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Port 1 ADC Channel Selects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

PROGRAMMABLE COUNTER ARRAY (PCA) WITH PWM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

PCA Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

PCA Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Operation of TCM Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Capture Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Timer Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Toggle Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

PWM Mode - (X8), Fixed Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

PWM Mode - (X8), Programmable Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

PWM Mode - Fixed Frequency, 16-bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

5/231

uPSD33xx

PWM Mode - Fixed Frequency, 10-bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129 Writing to Capture/Compare Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129 Control Register Bit Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129 TCM Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

PSD MODULE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

PSD Module Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Memory Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

Runtime Control Register Definitions (csiop). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

PSD Module Detailed Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

PSD Module Reset Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

AC/DC PARAMETERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

DC AND AC PARAMETERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

PACKAGE MECHANICAL INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

REVISION HISTORY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

6/231

uPSD33xx

SUMMARY DESCRIPTION

The Turbo uPSD33xx Series combines a powerful 8051-based microcontroller with a flexible memory structure, programmable logic, and a rich peripheral mix to form an ideal embedded controller. At its core is a fast 4-cycle 8032 MCU with a 6-byte instruction prefetch queue (PFQ) and a 4-entry fully associative branching cache (BC) to maximize MCU performance, enabling loops of code in smaller localities to execute extremely fast.

Code development is easily managed without a hardware In-Circuit Emulator by using the serial JTAG debug interface. JTAG is also used for InSystem Programming (ISP) in as little as 10 seconds, perfect for manufacturing and lab development. The 8032 core is coupled to Programmable System Device (PSD) architecture to optimize the 8032 memory structure, offering two independent

banks of Flash memory that can be placed at virtually any address within 8032 program or data address space, and easily paged beyond 64K bytes using on-chip programmable decode logic. Dual Flash memory banks provide a robust solution for remote product updates in the field through In-Ap- plication Programming (IAP). Dual Flash banks also support EEPROM emulation, eliminating the need for external EEPROM chips. General purpose programmable logic (PLD) is included to build an endless variety of glue-logic, saving external logic devices. The PLD is configured using the software development tool, PSDsoft Express, available from the web at www.st.com/psm, at no charge. The uPSD33xx also includes supervisor functions such as a programmable watchdog timer and low-voltage reset.

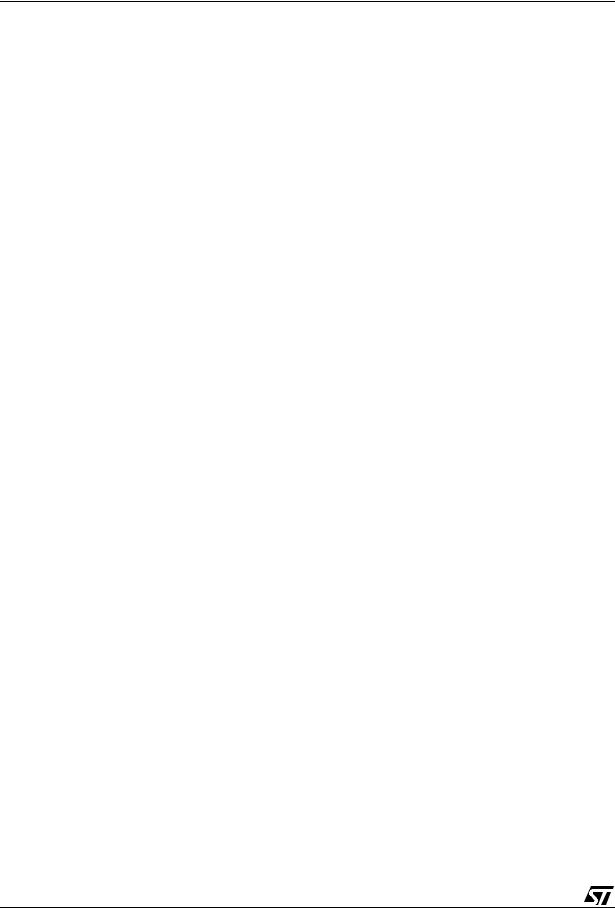

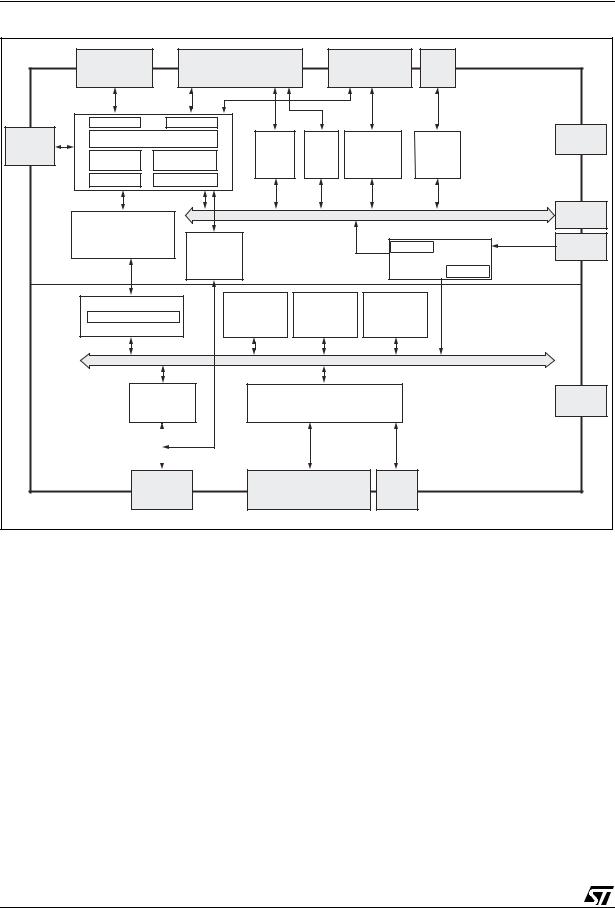

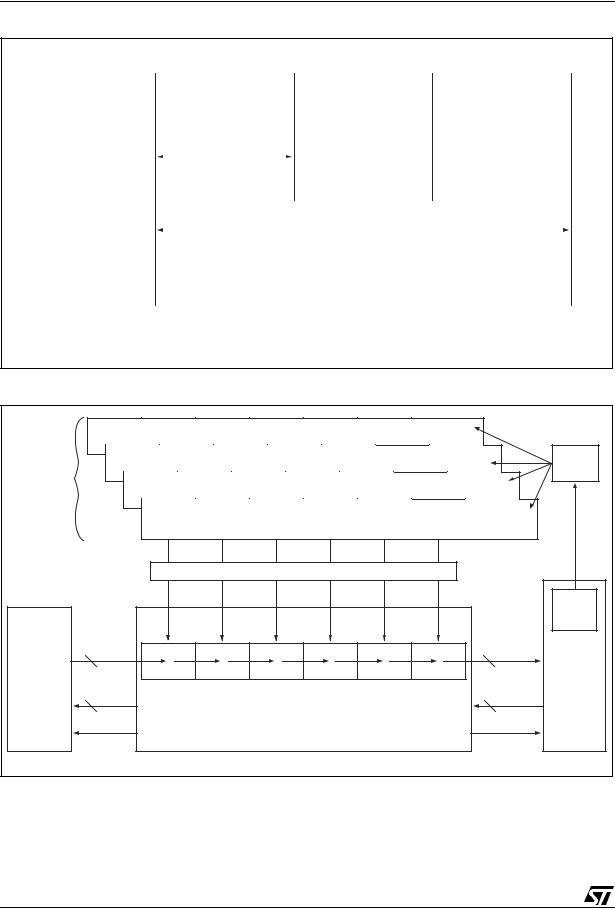

Figure 2. Block Diagram

|

|

|

|

uPSD33xx |

|

|

||

|

(3) 16-bit |

|

|

|

|

|

|

|

|

Timer/ |

Turbo |

|

PFQ |

|

1st Flash Memory: |

|

|

|

Counters |

|

|

|

||||

|

(2) |

8032 |

|

& |

|

64K, 128K, |

|

|

|

Core |

|

BC |

Programmable |

or 256K Bytes |

|

||

|

External |

|

|

|||||

|

|

|

|

|

|

|||

|

Interrupts |

|

|

|

Decode and |

|

|

|

|

|

|

|

|

Page Logic |

2nd Flash Memory: |

|

|

|

|

|

|

|

|

|

||

P3.0:7 |

|

I2C |

|

|

|

16K or 32K Bytes |

|

|

|

|

|

|

|

|

SRAM: |

|

|

|

|

|

|

|

|

2K, 8K, or 32K Bytes |

|

|

|

|

UART0 |

|

|

|

|

|

|

|

|

|

|

|

|

(8) GPIO, Port A |

PA0:7 |

|

|

|

|

|

|

|

(80-pin only) |

||

|

(8) GPIO, Port 3 |

|

|

|

||||

|

|

General |

|

|

||||

|

|

|

|

|

(8) GPIO, Port B |

PB0:7 |

||

|

|

|

|

|

Purpose |

|||

P1.0:7 |

(8) GPIO, Port 1 |

BUS |

Programmable |

|

|

|||

Logic, |

(2) GPIO, Port D |

PD1:2 |

||||||

|

|

|

|

|||||

|

|

|

|

16 Macrocells |

||||

|

|

|

|

|

|

|||

|

(8) 10-bit ADC |

|

SYSTEM |

|

(4) GPIO, Port C |

|

||

|

|

|

|

|

|

PC0:7 |

||

|

Optional IrDA |

|

|

|

|

|||

|

UART1 |

JTAG ICE and ISP |

|

|||||

|

Encoder/Decoder |

|

||||||

|

|

|

|

|

|

|||

|

|

SPI |

|

|

8032 Address/Data/Control Bus |

MCU |

||

|

|

|

|

(80-pin device only) |

Bus |

|||

|

|

|

|

|

||||

|

16-bit PCA |

|

|

Supervisor: |

|

|||

|

(6) PWM, CAPCOM, TIMER |

Watchdog and Low-Voltage Reset |

|

|||||

P4.0:7 |

(8) GPIO, Port 4 |

|

VCC, VDD, GND, Reset, Crystal In |

Dedicated |

||||

|

Pins |

|||||||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

AI08875 |

|

|

|

|

|

|

|

|

7/231 |

|

uPSD33xx

PIN DESCRIPTIONS

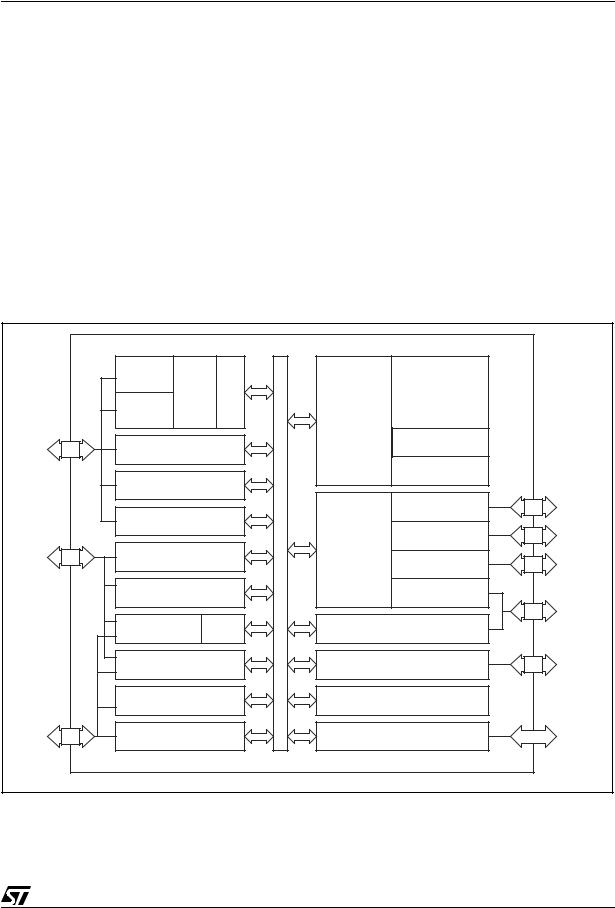

Figure 3. TQFP52 Connections

PD1/CLKIN 1 PC7 2 JTAG TDO 3 JTAG TDI 4 DEBUG 5 3.3V VCC 6

PC4/TERR 7 VDD(1) 8 GND 9

PC3/TSTAT 10 PC2/VSTBY 11 JTAG TCK 12 JTAG TMS 13

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

/ADC7 |

|

/ADC6 |

|

|

|

|

|

|

|

|

|

|

(3) REF |

|

|

|

|

|

|

|

|

|

|

|

(2) |

(2) |

||

PB0 |

PB1 |

PB2 |

|

PB3 |

PB4 |

|

PB5 |

|

|

|

RESETIN |

|

PB6 |

|

PB7 |

P1.7/SPISEL |

|

P1.6/SPITXD |

|||||||

|

|

AV |

GND |

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

/V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

52 |

|

51 |

|

50 |

49 |

|

48 |

47 |

|

46 |

|

45 |

|

44 |

43 |

42 |

|

41 |

40 |

||||||

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

15 |

16 |

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

25 |

26 |

SPISEL |

SPITXD |

SPIRXD |

SPICLK |

TXD1(IrDA) |

GND |

RXD1(IrDA) |

T2X |

T2 |

RXD0/P3.0 |

TXD0/P3.1 |

EXTINT0/TG0/P3.2 |

EXTINT1/TG1/P3.3 |

/PCACLK1/P4.7 |

(2) |

(2) |

(2) |

/PCACLK0/P4.3 |

|

(2) |

(2) |

(2) |

|

|

|

|

|

/TCM5/P4.6 |

/TCM4/P4.5 |

/TCM3/P4.4 |

|

|

/TCM2/P4.2 |

/TCM1/P4.1 |

/TCM0/P4.0 |

|

|

|

|

(2) |

|

|

|

(2) |

|

|

|

|

|

|

|

|

39 P1.5/SPIRXD(2)/ADC5

38 P1.4/SPICLK(2)/ADC4

37 P1.3/TXD1(IrDA)(2)/ADC3

36 P1.2/RXD1(IrDA)(2)/ADC2

35 P1.1/T2X(2)/ADC1

34 P1.0/T2(2)/ADC0

33 VDD(1)

32 XTAL2

31 XTAL1

30 P3.7/SCL

29 P3.6/SDA

28 P3.5/C1

27 P3.4/C0

AI07822

Note: 1. For 5V applications, VDD must be connected to a 5.0V source. For 3.3V applications, VDD must be connected to a 3.3V source.

2.These signals can be used on one of two different ports (Port 1 or Port 4) for flexibility. Default is Port1.

3.VREF and 3.3V AVCC are shared in the 52-pin package only. ADC channels must use AVCC as VREF for the 52-pin package.

8/231

uPSD33xx

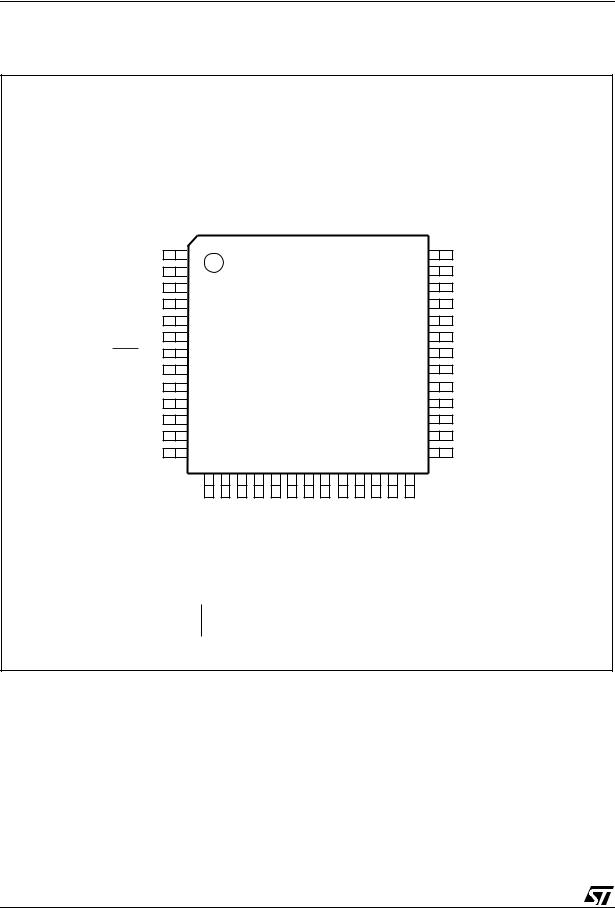

Figure 4. TQFP80 Connections

PD2/CSI 1

P3.3/TG1/EXINT1 2

PD1/CLKIN 3

ALE 4

PC7 5

JTAG TDO 6

JTAG TDI 7

DEBUG 8

PC4/TERR 9

3.3V VCC 10

NC 11

VDD(1) 12

GND 13

PC3/TSTAT 14

PC2/VSTBY 15

JTAG TCK 16

NC 17

SPISEL(2)/PCACLK1/P4.7 18

SPITXD(2)/TCM5/P4.6 19

JTAG TMS 20

PB0 |

P3.2/EXINT0/TG0 |

PB1 |

P3.1/TXD0 |

PB2 |

P3.0/RXD0 |

PB3 |

PB4 |

AV |

PB5 |

V |

GND |

RESETIN |

PB6 |

PB7 |

RD |

|

/ADC7 |

|

PSEN |

WR |

|

/ADC6 |

||||||||||||||||

|

P1.7/SPISEL |

|

|

P1.6/SPITXD |

||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(2) |

|

|

|

|

(2) |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CC |

|

|

REF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

80 |

79 |

78 |

77 |

76 |

75 |

74 |

73 |

72 |

|

71 |

70 |

69 |

68 |

67 |

|

66 |

|

65 |

64 |

63 |

|

62 |

61 |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

21 |

22 |

23 |

24 |

25 |

26 |

27 |

28 |

29 |

30 |

31 |

32 |

33 |

34 |

35 |

36 |

37 |

38 |

39 |

40 |

PA7 |

PA6 |

(2) |

PA5 |

(2) |

PA4 |

/PCACLK0/P4.3 |

PA3 |

GND |

(2) |

(2) |

PA2 |

(2) |

PA1 |

PA0 |

MCUAD0 |

MCUAD1 |

MCUAD2 |

MCUAD3 |

P3.4/C0 |

|

|

/TCM4/P4.5 |

|

/TCM3/P4.4 |

|

TXD1(IrDA) |

|

|

/TCM2/P4.2 |

/TCM1/P4.1 |

|

/TCM0/P4.0 |

|

|

|

|

|

|

|

|

|

SPIRXD |

|

SPICLK |

|

|

|

RXD1(IrDA) |

T2X |

|

T2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

60 |

P1.5/SPIRXD(2)/ADC5 |

59 |

P1.4/SPICLK(2)/ADC4 |

58 |

P1.3/TXD1(IrDA)(2)/ADC3 |

57 |

MCU A11 |

56 |

P1.2/RXD1(IrDA)(2)/ADC2 |

55 |

MCU A10 |

54 |

P1.1/T2X(2)/ADC1 |

53 |

MCU A9 |

52 |

P1.0/T2(2)/ADC0 |

51 |

MCU A8 |

50 |

(1) |

VDD |

|

49 |

XTAL2 |

48 |

XTAL1 |

47 |

MCU AD7 |

46 |

P3.7/SCL |

45 |

MCU AD6 |

44 |

P3.6/SDA |

43 |

MCU AD5 |

42 |

P3.5/C1 |

41 |

MCU AD4 |

AI07823

Note: NC = Not Connected

Note: 1. For 5V applications, VDD must be connected to a 5.0V source. For 3.3V applications, VDD must be connected to a 3.3V source. 2. These signals can be used on one of two different ports (Port 1 or Port 4) for flexibility. Default is Port1.

9/231

uPSD33xx

Table 2. Pin Definitions

Port Pin |

|

Signal |

80-Pin |

52-Pin |

In/Out |

|

Function |

|

|

|

Name |

No. |

No.(1) |

Basic |

Alternate 1 |

Alternate 2 |

|||

|

|

|

|||||||

|

|

|

|

|

|

|

External Bus |

|

|

MCUAD0 |

|

AD0 |

36 |

N/A |

I/O |

Multiplexed Address/ |

|

|

|

|

|

|

|

|

|

|

Data bus A0/D0 |

|

|

|

|

|

|

|

|

|

|

|

|

MCUAD1 |

|

AD1 |

37 |

N/A |

I/O |

Multiplexed Address/ |

|

|

|

|

Data bus A1/D1 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MCUAD2 |

|

AD2 |

38 |

N/A |

I/O |

Multiplexed Address/ |

|

|

|

|

Data bus A2/D2 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MCUAD3 |

|

AD3 |

39 |

N/A |

I/O |

Multiplexed Address/ |

|

|

|

|

Data bus A3/D3 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MCUAD4 |

|

AD4 |

41 |

N/A |

I/O |

Multiplexed Address/ |

|

|

|

|

Data bus A4/D4 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MCUAD5 |

|

AD5 |

43 |

N/A |

I/O |

Multiplexed Address/ |

|

|

|

|

Data bus A5/D5 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MCUAD6 |

|

AD6 |

45 |

N/A |

I/O |

Multiplexed Address/ |

|

|

|

|

Data bus A6/D6 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MCUAD7 |

|

AD7 |

47 |

N/A |

I/O |

Multiplexed Address/ |

|

|

|

|

Data bus A7/D7 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MCUA8 |

|

A8 |

51 |

N/A |

O |

External Bus, Addr |

|

|

|

|

A8 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MCUA9 |

|

A9 |

53 |

N/A |

O |

External Bus, Addr |

|

|

|

|

A9 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MCUA10 |

|

A10 |

55 |

N/A |

O |

External Bus, Addr |

|

|

|

|

A10 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MCUA11 |

|

A11 |

57 |

N/A |

O |

External Bus, Addr |

|

|

|

|

A11 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1.0 |

|

T2 |

52 |

34 |

I/O |

General I/O port pin |

Timer 2 Count input |

ADC Channel 0 |

|

|

ADC0 |

(T2) |

input (ADC0) |

||||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

P1.1 |

|

T2X |

54 |

35 |

I/O |

General I/O port pin |

Timer 2 Trigger input |

ADC Channel 1 |

|

|

ADC1 |

(T2X) |

input (ADC1) |

||||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

P1.2 |

|

RxD1 |

56 |

36 |

I/O |

General I/O port pin |

UART1 or IrDA |

ADC Channel 2 |

|

|

ADC2 |

Receive (RxD1) |

input (ADC2) |

||||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

P1.3 |

|

TXD1 |

58 |

37 |

I/O |

General I/O port pin |

UART or IrDA |

ADC Channel 3 |

|

|

ADC3 |

Transmit (TxD1) |

input (ADC3) |

||||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||

P1.4 |

SPICLK |

59 |

38 |

I/O |

General I/O port pin |

SPI Clock Out |

ADC Channel 4 |

||

|

ADC4 |

(SPICLK) |

input (ADC4) |

||||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||

P1.5 |

SPIRxD |

60 |

39 |

I/O |

General I/O port pin |

SPI Receive |

ADC Channel 5 |

||

|

ADC6 |

(SPIRxD) |

input (ADC5) |

||||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||

P1.6 |

SPITXD |

61 |

40 |

I/O |

General I/O port pin |

SPI Transmit |

ADC Channel 6 |

||

|

ADC6 |

(SPITxD) |

input (ADC6) |

||||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

P1.7 |

|

SPISEL |

|

64 |

41 |

I/O |

General I/O port pin |

SPI Slave Select |

ADC Channel 7 |

|

ADC7 |

(SPISEL) |

input (ADC7) |

||||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

P3.0 |

|

RxD0 |

75 |

23 |

I/O |

General I/O port pin |

UART0 Receive |

|

|

|

(RxD0) |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P3.1 |

|

TXD0 |

77 |

24 |

I/O |

General I/O port pin |

UART0 Transmit |

|

|

|

(TxD0) |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EXINT0 |

|

|

|

|

Interrupt 0 input |

|

||

P3.2 |

79 |

25 |

I/O |

General I/O port pin |

(EXTINT0)/Timer 0 |

|

|||

|

TGO |

|

|||||||

|

|

|

|

|

|

gate control (TG0) |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Interrupt 1 input |

|

P3.3 |

|

INT1 |

2 |

26 |

I/O |

General I/O port pin |

(EXTINT1)/Timer 1 |

|

|

|

|

|

|

|

|

|

|

gate control (TG1) |

|

|

|

|

|

|

|

|

|

|

|

P3.4 |

|

C0 |

40 |

27 |

I/O |

General I/O port pin |

Counter 0 input (C0) |

|

|

|

|

|

|

|

|

|

|

|

|

10/231

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

uPSD33xx |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Port Pin |

|

|

Signal |

80-Pin |

52-Pin |

In/Out |

|

Function |

|

|

|||||

|

|

|

Name |

No. |

No.(1) |

Basic |

Alternate 1 |

|

Alternate 2 |

|||||||

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

P3.5 |

|

|

C1 |

42 |

28 |

I/O |

General I/O port pin |

Counter 1 input (C1) |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P3.6 |

|

|

SDA |

44 |

29 |

I/O |

General I/O port pin |

I2C Bus serial data |

|

|

||||

|

|

|

|

(I2CSDA) |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P3.7 |

|

|

SCL |

46 |

30 |

I/O |

General I/O port pin |

I2C Bus clock |

|

|

||||

|

|

|

|

(I2CSCL) |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P4.0 |

|

|

T2 |

33 |

22 |

I/O |

General I/O port pin |

Program Counter |

Timer 2 Count input |

|||||

|

|

|

|

TCM0 |

Array0 PCA0-TCM0 |

(T2) |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

P4.1 |

|

|

T2X |

31 |

21 |

I/O |

General I/O port pin |

PCA0-TCM1 |

Timer 2 Trigger input |

|||||

|

|

|

|

TCM1 |

(T2X) |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

P4.2 |

|

|

RXD1 |

30 |

20 |

I/O |

General I/O port pin |

PCA0-TCM2 |

UART1 or IrDA |

|||||

|

|

|

|

TCM2 |

Receive (RxD1) |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

P4.3 |

|

|

TXD1 |

27 |

18 |

I/O |

General I/O port pin |

PCACLK0 |

UART1 or IrDA |

|||||

|

|

|

PCACLK0 |

Transmit (TxD1) |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

P4.4 |

|

SPICLK |

25 |

17 |

I/O |

General I/O port pin |

Program Counter |

SPI Clock Out |

||||||

|

|

|

|

TCM3 |

Array1 PCA1-TCM3 |

(SPICLK) |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

P4.5 |

|

SPIRXD |

23 |

16 |

I/O |

General I/O port pin |

PCA1-TCM4 |

SPI Receive |

||||||

|

|

|

|

TCM4 |

(SPIRxD) |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P4.6 |

|

SPITXD |

19 |

15 |

I/O |

General I/O port pin |

PCA1-TCM5 |

SPI Transmit |

||||||

|

|

|

(SPITxD) |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P4.7 |

|

|

SPISEL |

|

18 |

14 |

I/O |

General I/O port pin |

PCACLK1 |

SPI Slave Select |

||||

|

|

|

PCACLK1 |

(SPISEL) |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VREF |

|

|

|

|

70 |

N/A |

I |

Reference Voltage |

|

|

|

|||

|

|

|

|

|

|

input for ADC |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

65 |

N/A |

O |

READ Signal, |

|

|

|

|

|

|

RD |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

external bus |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

62 |

N/A |

O |

WRITE Signal, |

|

|

|

|

|

WR |

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

external bus |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

63 |

N/A |

O |

PSEN Signal, |

|

|

|

|

PSEN |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

external bus |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ALE |

|

|

|

|

4 |

N/A |

O |

Address Latch |

|

|

|

|||

|

|

|

|

|

|

signal, external bus |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

68 |

44 |

I |

Active low reset |

|

|

|

RESET_IN |

|

|

|

|

|

|

|

|||||||||

|

|

|

|

input |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XTAL1 |

|

|

|

|

48 |

31 |

I |

Oscillator input pin |

|

|

|

||||

|

|

|

|

|

for system clock |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XTAL2 |

|

|

|

|

49 |

32 |

O |

Oscillator output pin |

|

|

|

||||

|

|

|

|

|

for system clock |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DEBUG |

|

|

|

|

8 |

5 |

I/O |

I/O to the MCU |

|

|

|

||||

|

|

|

|

|

Debug Unit |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

PA0 |

|

|

|

|

35 |

N/A |

I/O |

General I/O port pin |

|

All Port A pins |

||||

|

|

PA1 |

|

|

|

|

34 |

N/A |

I/O |

General I/O port pin |

|

support: |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1. |

PLD Macro-cell |

|

|

PA2 |

|

|

|

|

32 |

N/A |

I/O |

General I/O port pin |

|

|||||

|

|

|

|

|

|

|

|

outputs, or |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PA3 |

|

|

|

|

28 |

N/A |

I/O |

General I/O port pin |

|

|

||||

|

|

|

|

|

|

|

2. |

PLD inputs, or |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

PA4 |

|

|

|

|

26 |

N/A |

I/O |

General I/O port pin |

|

3. |

Latched |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Address Out |

|

|

PA5 |

|

|

|

|

24 |

N/A |

I/O |

General I/O port pin |

|

|

||||

|

|

|

|

|

|

|

|

(A0-A7), or |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PA6 |

|

|

|

|

22 |

N/A |

I/O |

General I/O port pin |

|

|

||||

|

|

|

|

|

|

|

4. |

Peripheral I/O |

||||||||

|

|

PA7 |

|

|

|

|

21 |

N/A |

I/O |

General I/O port pin |

|

|

Mode |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11/231

uPSD33xx

Port Pin |

Signal |

80-Pin |

52-Pin |

In/Out |

|

Function |

|

|

|||

Name |

No. |

No.(1) |

Basic |

Alternate 1 |

|

Alternate 2 |

|||||

|

|

|

|||||||||

PB0 |

|

|

|

80 |

52 |

I/O |

General I/O port pin |

|

|

|

|

|

|

|

|

|

|

|

|

|

All Port B pins |

||

PB1 |

|

|

|

78 |

51 |

I/O |

General I/O port pin |

|

|||

|

|

|

|

|

|

|

|

|

support: |

||

PB2 |

|

|

|

76 |

50 |

I/O |

General I/O port pin |

|

|||

|

|

|

|

1. |

PLD Macro-cell |

||||||

|

|

|

|

|

|

|

|

|

|||

PB3 |

|

|

|

74 |

49 |

I/O |

General I/O port pin |

|

|||

|

|

|

|

|

outputs, or |

||||||

|

|

|

|

|

|

|

|

|

|

||

PB4 |

|

|

|

73 |

48 |

I/O |

General I/O port pin |

|

2. |

PLD inputs, or |

|

|

|

|

|

|

|

|

|

|

3. |

Latched |

|

PB5 |

|

|

|

71 |

46 |

I/O |

General I/O port pin |

|

|||

|

|

|

|

|

Address Out |

||||||

|

|

|

|

|

|

|

|

|

|

||

PB6 |

|

|

|

67 |

43 |

I/O |

General I/O port pin |

|

|

||

|

|

|

|

|

(A0-A7) |

||||||

PB7 |

|

|

|

66 |

42 |

I/O |

General I/O port pin |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

JTAGTMS |

|

TMS |

20 |

13 |

I |

JTAG pin (TMS) |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

JTAGTCK |

|

TCK |

16 |

12 |

I |

JTAG pin (TCK) |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SRAM Standby |

|

PLD Macrocell |

|

PC2 |

VSTBY |

15 |

11 |

I/O |

General I/O port pin |

voltage input |

|

||||

output, or PLD input |

|||||||||||

|

|

|

|

|

|

|

|

(VSTBY) |

|||

|

|

|

|

|

|

|

|

|

|

||

PC3 |

TSTAT |

14 |

10 |

I/O |

General I/O port pin |

Optional JTAG |

|

PLD, Macrocell |

|||

Status (TSTAT) |

output, or PLD input |

||||||||||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

7 |

I/O |

General I/O port pin |

Optional JTAG |

|

PLD, Macrocell |

|

PC4 |

TERR |

|

|||||||||

Status (TERR) |

output, or PLD input |

||||||||||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||

JTAGTDI |

|

TDI |

7 |

4 |

I |

JTAG pin (TDI) |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

JTAGTDO |

|

TDO |

6 |

3 |

O |

JTAG pin (TDO) |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

PC7 |

|

|

|

5 |

2 |

I/O |

General I/O port pin |

|

|

PLD, Macrocell |

|

|

|

|

|

output, or PLD input |

|||||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

PD1 |

CLKIN |

3 |

1 |

I/O |

General I/O port pin |

|

1. |

PLD I/O |

|||

|

2. |

Clock input to |

|||||||||

|

|

|

|

|

|

|

|

|

|

PLD and APD |

|

|

|

|

|

|

|

|

|

|

|

|

|

PD2 |

|

CSI |

1 |

N/A |

I/O |

General I/O port pin |

|

1. |

PLD I/O |

||

|

|

2. |

Chip select ot |

||||||||

|

|

|

|

|

|

|

|

|

|

PSD Module |

|

|

|

|

|

|

|

|

|

|

|

|

|

3.3V-VCC |

|

|

|

10 |

6 |

|

VCC - MCU Module |

|

|

|

|

AVCC |

|

|

|

72 |

47 |

|

Analog VCC Input |

|

|

|

|

VDD |

|

|

|

|

|

|

VDD - PSD Module |

|

|

|

|

|

|

|

12 |

8 |

|

VDD - 3.3V for 3V |

|

|

|

||

3.3V or 5V |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

VDD - 5V for 5V |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

VDD |

|

|

|

|

|

|

VDD - PSD Module |

|

|

|

|

|

|

|

50 |

33 |

|

VDD - 3.3V for 3V |

|

|

|

||

3.3V or 5V |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

VDD - 5V for 5V |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

GND |

|

|

|

13 |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

|

|

|

29 |

19 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

|

|

|

69 |

45 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC |

|

|

|

11 |

N/A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC |

|

|

|

17 |

N/A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note: 1. N/A = Signal Not Available on 52-pin package.

12/231

uPSD33xx

uPSD33xx HARDWARE DESCRIPTION

The uPSD33xx has a modular architecture built from a stacked die process. There are two die, one is designated “MCU Module” in this document, and the other is designated “PSD Module” (seeFigure 5., page 14). In all cases, the MCU Module die operates at 3.3V with 5V tolerant I/O. The PSD Module is either a 3.3V die or a 5V die, depending on the uPSD33xx device as described below.

The MCU Module consists of a fast 8032 core, that operates with 4 clocks per instruction cycle, and has many peripheral and system supervisor functions. The PSD Module provides the 8032 with multiple memories (two Flash and one SRAM) for program and data, programmable logic for address decoding and for general-purpose logic, and additional I/O. The MCU Module communicates with the PSD Module through internal address and data busses (A8 – A15, AD0 – AD7) and control signals (RD, WR, PSEN, ALE, RESET).

There are slightly different I/O characteristics for each module. I/Os for the MCU module are designated as Ports 1, 3, and 4. I/Os for the PSD Module are designated as Ports A, B, C, and D.

For all 5V uPSD33xx devices, a 3.3V MCU Module is stacked with a 5V PSD Module. In this case, a 5V uPSD33xx device must be supplied with 3.3VCC for the MCU Module and 5.0VDD for the PSD Module. Ports 3 and 4 of the MCU Module are 3.3V ports with tolerance to 5V devices (they can be directly driven by external 5V devices and they can directly drive external 5V devices while

producing a VOH of 2.4V min and VCC max). Ports A, B, C, and D of the PSD Module are true 5V ports.

For all 3.3V uPSD33xxV devices, a 3.3V MCU Module is stacked with a 3.3V PSD Module. In this case, a 3.3V uPSD33xx device needs to be supplied with a single 3.3V voltage source at both VCC and VDD. I/O pins on Ports 3 and 4 are 5V tolerant and can be connected to external 5V peripherals devices if desired. Ports A, B, C, and D of the PSD Module are 3.3V ports, which are not tolerant to external 5V devices.

Refer to Table 3 for port type and voltage source requirements.

80-pin uPSD33xx devices provide access to 8032 address, data, and control signals on external pins to connect external peripheral and memory devices. 52-pin uPSD33xx devices do not provide access to the 8032 system bus.

All non-volatile memory and configuration portions of the uPSD33xx device are programmed through the JTAG interface and no special programming voltage is needed. This same JTAG port is also used for debugging of the 8032 core at runtime providing breakpoint, single-step, display, and trace features. A non-volatile security bit may be programmed to block all access via JTAG interface for security. The security bit is defeated only by erasing the entire device, leaving the device blank and ready to use again.

Table 3. Port Type and Voltage Source Combinations

Device Type |

VCC for MCU |

VDD for PSD |

Ports 3 and 4 on |

Ports A, B, C, and D on |

|

Module |

Module |

MCU Module |

PSD Module |

||

|

|||||

|

|

|

|

|

|

5V: |

3.3V |

5.0V |

3.3V but 5V tolerant |

5V |

|

uPSD33xx |

|||||

|

|

|

|

||

|

|

|

|

|

|

3.3V: |

3.3V |

3.3V |

3.3V but 5V tolerant |

3.3V. NOT 5V tolerant |

|

uPSD33xxV |

|||||

|

|

|

|

||

|

|

|

|

|

13/231

uPSD33xx

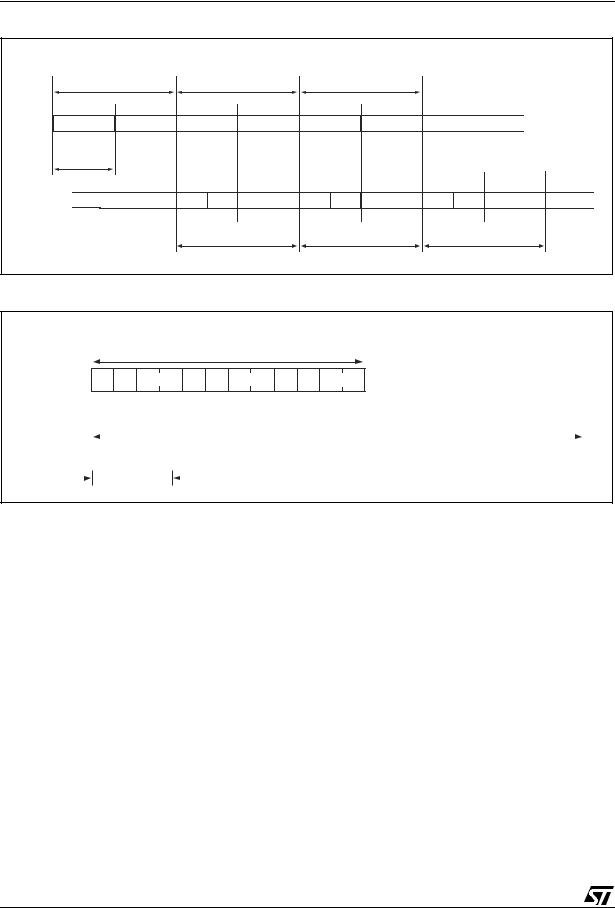

Figure 5. uPSD33xx Functional Modules

|

Port 3 - UART0, |

Port 1 - Timer, ADC, SPI |

|

|

Port 4 - PCA, |

Port 3 |

|

|

||||

|

Intr, Timers |

|

|

|

PWM, UART1 |

I2C |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

MCU Module |

|

|

Port 3 |

|

Port 1 |

|

|

|

|

|

|

|

|

|

XTAL |

Turbo 8032 Core |

|

|

|

|

PCA |

|

|

|

VCC Pins |

||

10-bit |

|

|

|

2 |

|

|

3.3V |

|||||

|

|

|

|

|

|

|

|

|||||

Clock Unit |

Dual |

|

3 Timer / |

|

SPI |

|

PWM |

I C |

|

|

||

|

ADC |

|

|

|

|

|||||||

|

UARTs |

|

Counters |

|

|

|

Counters |

Unit |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Interrupt |

256 Byte SRAM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8032 Internal |

Bus |

|

|

|

|

|

Ext. |

|

|

Dedicated Memory |

|

|

|

|

|

|

Bus |

||||

|

|

|

|

|

|

|

|

|

|

|||

|

Interface Prefetch, |

|

|

|

|

|

|

|

|

Reset Input |

Reset |

|

|

Branch Cache |

|

|

|

|

|

LVD |

|

||||

|

JTAG |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

Pin |

|||||

|

|

|

|

|

|

|

Internal |

Reset Logic |

|

|||

|

|

|

DEBUG |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

Reset |

|

WDT |

|

|

|

8-Bit Die-to-Die Bus |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||

|

Enhanced MCU Interface |

|

|

|

|

|

|

PSD |

|

|

||

|

|

Secondary |

|

|

Reset |

PSD Module |

||||||

|

PSD Page Register |

|

Main Flash |

SRAM |

|

|

||||||

|

|

|

Flash |

|

|

|

|

|

||||

|

Decode PLD |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

PSD Internal Bus |

|

|

|

|

|

|

||

|

|

JTAG ISP |

CPLD - 16 MACROCELLS |

|

|

|

VDD Pins |

|||||

|

|

|

|

|

3.3V or 5V |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

uPSD33XX |

Port C |

Port A,B,C PLD |

|

Port D |

|

|

|

|

||||

JTAG and |

|

|

|

|

|

|||||||

|

|

I/O and GPIO |

|

GPIO |

|

|

|

|

||||

|

|

GPIO |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

AI07842 |

14/231

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

uPSD33xx |

||

MEMORY ORGANIZATION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

The 8032 MCU core views memory on the MCU |

|

dress space is for data memory. Program memory |

||||||||||||||||

module as “internal” memory and it views memory |