Samsung K4D263238M-QC45, K4D263238M-QC55, K4D263238M-QC50, K4D263238M-QC60 Datasheet

K4D263238M |

128M DDR SDRAM |

128Mbit DDR SDRAM

1M x 32Bit x 4 Banks

Double Data Rate Synchronous RAM with Bi-directional Data Strobe and DLL

Revision 1.3

August 2001

Samsung Electronics reserves the right to change products or specification without notice.

- 1 - |

Rev. 1.3 (Aug. 2001) |

|

|

|

|

K4D263238M |

128M DDR SDRAM |

Revision History

Revision 1.3 (August 2, 2001)

•Removed K4D263238M-QC40 with VDD&VDDQ=2.8V

•Changed VDD&VDDQ of K4D263238M-QC45 from 2.8V to 2.5V.

•Changed tCK(max) from 7ns to 10ns.

Revision 1.2 (July 12, 2001)

•Corrected CAS latency of K4D263238M-QC45 from CL3 to CL4

•The specification for the 222MHz/250MHz is preliminary one.

Revision 1.1 (March 5, 2000)

•Added K4D263238M-QC40 with VDD&VDDQ=2.8V

•Changed VDD/VDDQ of K4D263238M-QC45 from 2.5V to 2.8V. Accordingly, DC current characteristics values have been changed. - Changed CAS latency of K4D263238M-QC45 from CL4 to CL3.

•Changed tWPREH of K4D263238M-QC50 from 0.3tCK to 0.25tCK

- 2 - |

Rev. 1.3 (Aug. 2001) |

|

|

|

|

K4D263238M |

128M DDR SDRAM |

Revision 1.0 (December 13, 2000)

•Defined capacitance values

•Chagned tRCDWR of K4D263238M-QC60 from 1tCK to 2tCK

Revision 0.5 (December 8, 2000)

•Changed AC input level from Vref + 0.31V to Vref + 0.35V

•Changed tRC/tRFC/tRAS/tRP/tRCDRD/tRCDWR from ns unit based from clock unit based.

•Changed VIN /VOUT/VDDQ in absolute maximum ratings from -1.0V ~3.6V to -0.5V ~ 3.6V.

Revision 0.4 (November 29, 2000) - Preliminary

•Removed K4D263238M-QC40

•Several AC parameters of K4D263238M-QC45 have been changed

-Changed tDQSQ from 0.4ns to 0.45ns. Changed tQH from tHP-0.6ns to tHP-0.45ns.

-Changed tDQSCK & tAC from 0.6ns to 0.7ns

-Changed tDQSS from 0.75tCK/1.25tCK to 0.8tCK/1.2tCK. Accordingly, changed tWPREH from 0.25tCK to 0.3tCK.

-Changed tDS/tDH from 0.4ns to 0.45ns. Changed tIS/tIH from 0.9ns to 1.0ns

-Corrected tDAL from 5tCK to 6tCK

•Several AC parameters of K4D263238M-QC50 have been changed

-Changed tQH from tHP-0.6ns to tHP-0.45ns.

-Changed tDQSCK & tAC from 0.6ns to 0.7ns

-Changed tDQSS from 0.75tCK/1.25tCK to 0.8tCK/1.2tCK. Accordingly, changed tWPREH from 0.25tCK to 0.3tCK.

-Corrected tDAL from 5tCK to 6tCK

•Several AC parameters of K4D263238M-QC55 have been changed

-Changed tDQSQ from 0.45ns to 0.5ns. Changed tOH from tHP-0.6ns to tHP-0.5ns.

-Changed tDQSCK & tAC from 0.6ns to 0.75ns

-Changed tDS/tDH from 0.45ns to 0.5ns. Changed tIS/tIH from 1.0ns to 1.1ns

-Changed tRC/tRFC from 60.5ns/71.5ns to 66ns/77ns. Changed tRP from 16.5ns to 22ns.

-Corrected tRCDWR from 5.5ns to 11ns. Corrected tDAL from 5tCK to 6tCK

•Changed tQH of K4D263238M-QC60 from tHP-0.75ns to tHP-0.5ns

•Add DC Characteristics value

•Define VIH(max) / VIL(min) as a note in Power & DC operating Condition table

•Changed refresh cycle time from 16ms to 32ms.Accordingly, tREF has been changed from 3.9us to 7.8us.

•Changed IIL,IOL test condition from 0V< VIN <VDD+0.3V to 0V< VIN <VDD.

Revision 0.3 (June 8, 2000)

• Removed Block Write function

Revision 0.2 (April 10, 2000)

•Separated tRCD into tRCDRD and tRCDWR

-tRCDRD: Row to Column delay for READ

-tRCDWR: Row to Column delay at WRITE

Revision 0.1 (March 16, 2000)

•Define the spec based on Vdd&Vddq=2.5V

•Maximum target frequency upto 250MHz@CL4

•Removed Write Interrupt by Read function

Revision 0.0 (December 27, 1999) - Target Spec

• Defined Target Specification

- 3 - |

Rev. 1.3 (Aug. 2001) |

|

|

|

|

K4D263238M |

128M DDR SDRAM |

1M x 32Bit x 4 Banks Double Data Rate Synchronous RAM with Bi-directional Data Strobe and DLL

FEATURES

• |

2.5V ± 5% power supply |

• |

Data I/O transactions on both edges of Data strobe |

• |

SSTL_2 compatible inputs/outputs |

• |

DLL aligns DQ and DQS transitions with Clock transition |

• |

4 banks operation |

• |

Edge aligned data & data strobe output |

• MRS cycle with address key programs |

• |

Center aligned data & data strobe input |

|

|

-. Read latency 3,4 (clock) |

• |

DM for write masking only |

|

-. Burst length (2, 4, 8 and Full page) |

• |

Auto & Self refresh |

|

-. Burst type (sequential & interleave) |

• |

32ms refresh period (4K cycle) |

• |

Full page burst length for sequential burst type only |

• |

100pin TQFP package |

• |

Start address of the full page burst should be even |

• |

Maximum clock frequency up to 222MHz |

• All inputs except data & DM are sampled at the positive |

• |

Maximum data rate up to 444Mbps/pin |

|

|

going edge of the system clock |

|

|

•Differential clock input

•No Write Interrupted by Read function

ORDERING INFORMATION

Part NO. |

Max Freq. |

Max Data Rate |

Interface |

Package |

|

K4D263238M-QC45 |

222MHz |

444Mbps/pin |

|

|

|

|

|

|

|

|

|

K4D263238M-QC50 |

200MHz |

400Mbps/pin |

SSTL_2 |

100 TQFP |

|

|

|

|

|||

K4D263238M-QC55 |

183MHz |

366Mbps/pin |

|||

|

|

||||

|

|

|

|

|

|

K4D263238M-QC60 |

166MHz |

333Mbps/pin |

|

|

|

|

|

|

|

|

GENERAL DESCRIPTION

FOR 1M x 32Bit x 4 Bank DDR SDRAM

The K4D263238 is 134,217,728 bits of hyper synchronous data rate Dynamic RAM organized as 4 x 1,048,576 words by 32 bits, fabricated with SAMSUNG′s high performance CMOS technology. Synchronous features with Data Strobe allow extremely high performance up to 1.8GB/s/chip. I/O transactions are possible on both edges of the clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the device to be useful for a variety of high performance memory system applications.

- 4 - |

Rev. 1.3 (Aug. 2001) |

|

|

|

|

K4D263238M |

128M DDR SDRAM |

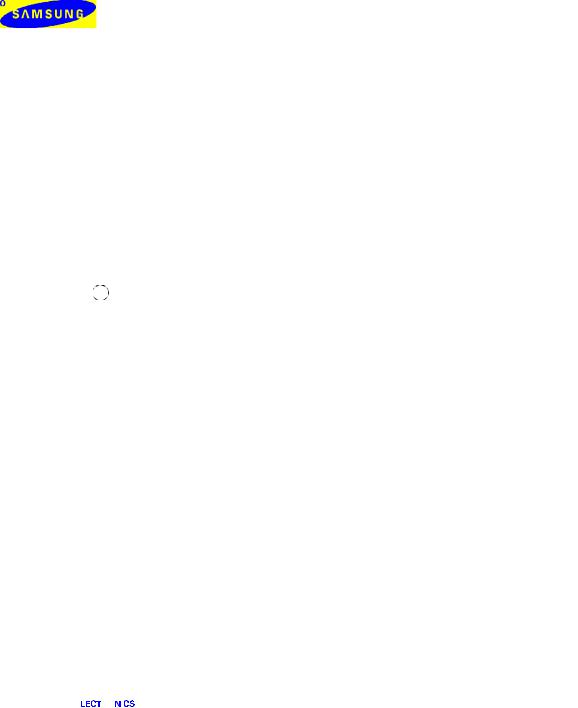

PIN CONFIGURATION (Top View)

|

|

|

|

DQ28 |

VDDQ |

DQ27 |

DQ26 |

VSSQ |

DQ25 |

DQ24 |

VDDQ |

DQ15 |

DQ14 |

VSSQ |

DQ13 |

DQ12 |

VDDQ |

VSS |

VDD |

DQ11 |

DQ10 |

VSSQ |

DQ9 |

DQ8 |

VDDQ |

VREF |

DM3 |

|

DM1 |

|

CK |

|

|

CK |

|

CKE |

MCL |

|

A8(AP) |

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

80 |

|

79 |

|

78 |

|

77 |

|

76 |

|

75 |

|

74 |

|

73 |

|

72 |

|

71 |

|

70 |

|

69 |

|

68 |

|

67 |

|

66 |

|

65 |

|

64 |

|

63 |

|

62 |

|

61 |

|

60 |

|

59 |

|

58 |

|

57 |

|

56 |

|

55 |

|

|

54 |

|

53 |

|

52 |

51 |

|

|

|

||||||

DQ29 |

|

|

81 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

50 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VSSQ |

|

|

82 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

49 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

DQ30 |

|

|

83 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

DQ31 |

|

|

84 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

47 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VSS |

|

|

85 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

46 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VDDQ |

|

|

86 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

45 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

N.C |

|

|

87 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

N.C |

|

|

88 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

100 Pin TQFP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

43 |

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

N.C |

|

|

89 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

42 |

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

N.C |

|

|

90 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

41 |

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

20 x 14 mm2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

N.C |

|

|

91 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

40 |

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

VSSQ |

|

|

92 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.65mm pin Pitch |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

39 |

|

|

|||||||||||||||||

RFU |

|

|

93 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

38 |

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

DQS |

|

|

94 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VDDQ |

|

|

95 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VDD |

|

|

96 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

35 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

DQ0 |

|

|

97 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

34 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

DQ1 |

|

|

98 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VSSQ |

|

|

99 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

DQ2 |

|

|

100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

8 |

|

9 |

|

10 |

|

11 |

|

12 |

|

13 |

|

14 |

|

15 |

|

16 |

|

17 |

|

18 |

|

19 |

|

20 |

|

21 |

|

22 |

|

23 |

|

24 |

|

25 |

|

26 |

|

|

27 |

|

28 |

|

29 |

30 |

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DQ3 |

VDDQ |

DQ4 |

DQ5 |

VSSQ |

DQ6 |

DQ7 |

VDDQ |

DQ16 |

DQ17 |

VSSQ |

DQ18 |

DQ19 |

VDDQ |

VDD |

VSS |

DQ20 |

DQ21 |

VSSQ |

DQ22 |

DQ23 |

VDDQ |

DM0 |

DM2 |

|

WE |

|

CAS |

|

RAS |

|

CS |

BA0 |

|

BA1 |

|

|

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

A7

A6

A5

A4

VSS

A9

N.C

N.C

N.C

N.C

N.C

N.C

N.C

A11

A10 VDD A3 A2 A1 A0

PIN DESCRIPTION

|

|

|

|

|

|

|

|

|

|

|

|

|

CK,CK |

Differential Clock Input |

|

BA0, BA1 |

Bank Select Address |

||||

|

|

|

|

|

|

|

|

|

||

|

|

CKE |

Clock Enable |

|

A0 ~A11 |

Address Input |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CS |

Chip Select |

|

DQ0 ~ DQ31 |

Data Input/Output |

||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

RAS |

Row Address Strobe |

|

VDD |

Power |

||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

CAS |

Column Address Strobe |

|

VSS |

Ground |

||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

WE |

Write Enable |

|

VDDQ |

Power for DQ′s |

||||

|

|

|

|

|

|

|

|

|

||

|

|

DQS |

Data Strobe |

|

VSSQ |

Ground for DQ′s |

||||

|

|

|

|

|

|

|

|

|

||

|

|

DMi |

Data Mask |

|

MCL |

Must Connect Low |

||||

|

|

|

|

|

|

|

|

|

||

|

|

RFU |

Reserved for Future Use |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- 5 - |

Rev. 1.3 (Aug. 2001) |

|

|

|

|

K4D263238M |

|

|

|

|

|

|

|

|

|

128M DDR SDRAM |

||||||||

INPUT/OUTPUT FUNCTIONAL DESCRIPTION |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

|

Type |

|

|

|

|

|

|

Function |

|||||||

|

|

|

|

|

|

|

|

|

|

The differential system clock Input. |

||||||||

CK, |

|

|

|

*1 |

|

Input |

|

All of the inputs are sampled on the rising edge of the clock except |

||||||||||

CK |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

DQ′s and DM′s that are sampled on both edges of the DQS. |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

Activates the CK signal when high and deactivates the CK signal |

||||||||

|

CKE |

|

Input |

|

when low. By deactivating the clock, CKE low indicates the Power |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

down mode or Self refresh mode. |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CS enables the command decoder when low and disabled the com- |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

CS |

|

Input |

|

mand decoder when high. When the command decoder is disabled, |

||||||||||||

|

|

|

|

|

|

|

|

|

|

new commands are ignored but previous operations continue. |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

Latches row addresses on the positive going edge of the CK with |

||||||||

|

RAS |

|

Input |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

RAS low. Enables row access & precharge. |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

Latches column addresses on the positive going edge of the CK with |

||||||||

|

CAS |

|

Input |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

CAS low. Enables column access. |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

Enables write operation and row precharge. |

||||||||

|

|

WE |

|

Input |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

Latches data in starting from CAS, WE active. |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

||||||||||||

DQS |

|

Input/Output |

|

Data input and output are synchronized with both edge of DQS. |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

Data In mask. Data In is masked by DM Latency=0 when DM is high |

||||||||

DM0 ~ DM3 |

|

Input |

|

in burst write. DM0 for DQ0 ~ DQ7, DM1 for DQ8 ~ DQ15, DM2 for |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

DQ16 ~ DQ23, DM3 for DQ24 ~ DQ31. |

||||||||

|

|

|

|

|

|

|

||||||||||||

DQ0 ~ DQ31 |

|

Input/Output |

|

Data inputs/Outputs are multiplexed on the same pins. |

||||||||||||||

|

|

|

|

|

|

|

||||||||||||

BA0, BA1 |

|

Input |

|

Selects which bank is to be active. |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

Row/Column addresses are multiplexed on the same pins. |

||||||||

A0 ~ A11 |

|

Input |

|

Row addresses : RA0 ~ RA11, Column addresses : CA0 ~ CA7. |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

Column address CA8 is used for auto precharge. |

||||||||

|

|

|

|

|

|

|

||||||||||||

VDD/VSS |

|

Power Supply |

|

Power and ground for the input buffers and core logic. |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

VDDQ/VSSQ |

|

Power Supply |

|

Isolated power supply and ground for the output buffers to provide |

||||||||||||||

|

|

improved noise immunity. |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

||||||||||||

VREF |

|

Power Supply |

|

Reference voltage for inputs, used for SSTL interface. |

||||||||||||||

|

|

|

|

|

|

|

||||||||||||

MCL |

|

Must Connect Low |

|

Must connect Low |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

*1 : The timing reference point for the differential clocking is the cross point of CK and CK. For any applications using the single ended clocking, apply VREF to CK pin.

- 6 - |

Rev. 1.3 (Aug. 2001) |

|

|

|

|

Loading...

Loading...