Samsung KS0713UM-L4CC, KS0713UM-L0CC, KS0713UM-H4CC, KS0713UM-H0CC, KS0713TB-XX-L4TF Datasheet

...

KS0713

65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD

January.2000

Ver. 4.0

Prepared by: Jae-Su, Ko

Ko1942@samsung.co.kr

Contents in this document are subject to change without notice. No part of this document may be reproduced

or transmitted in any form or by any means, electronic or mechanical, for any purpose, without the express

written permission of LCD Driver IC Team.

65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD KS0713

2

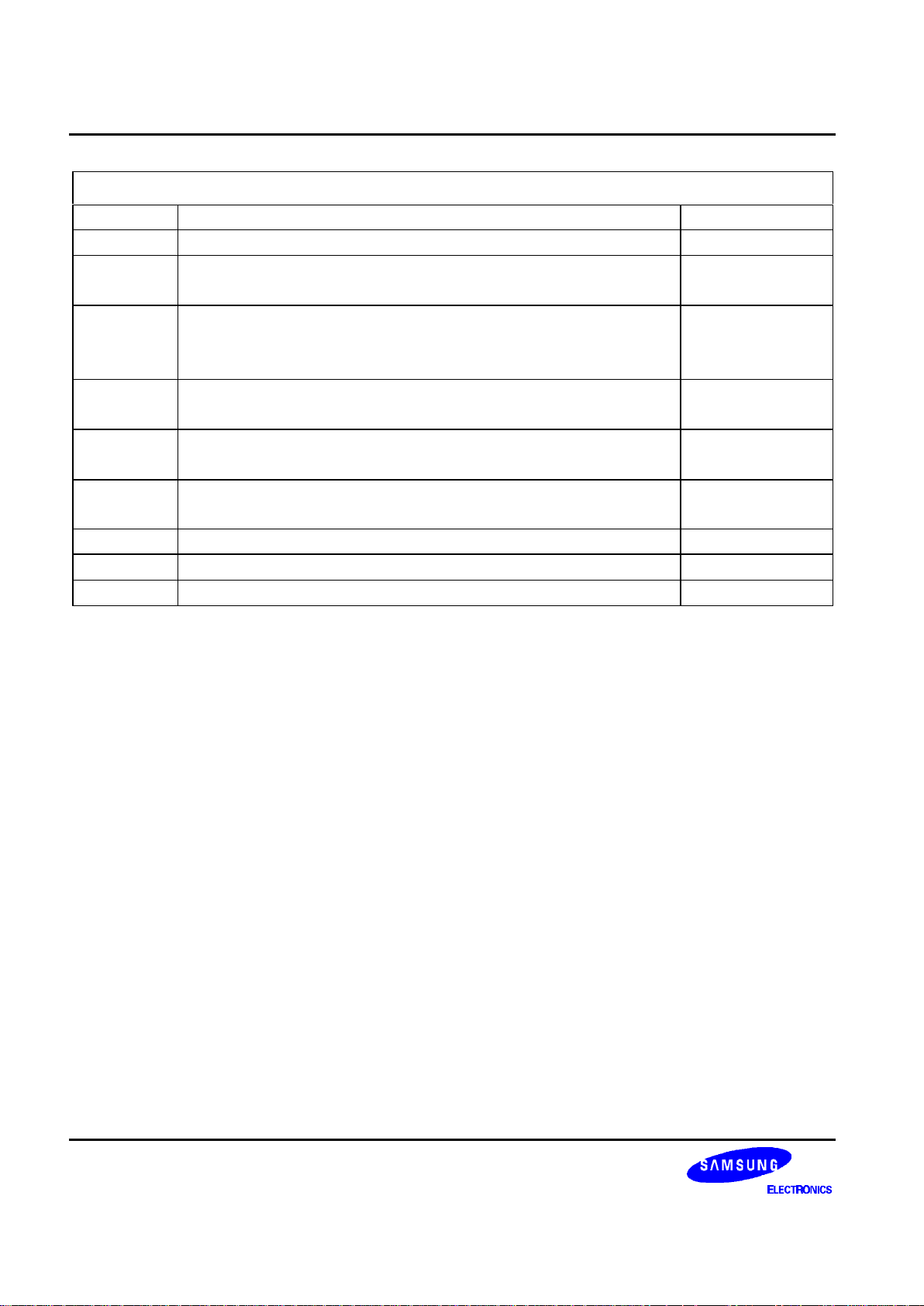

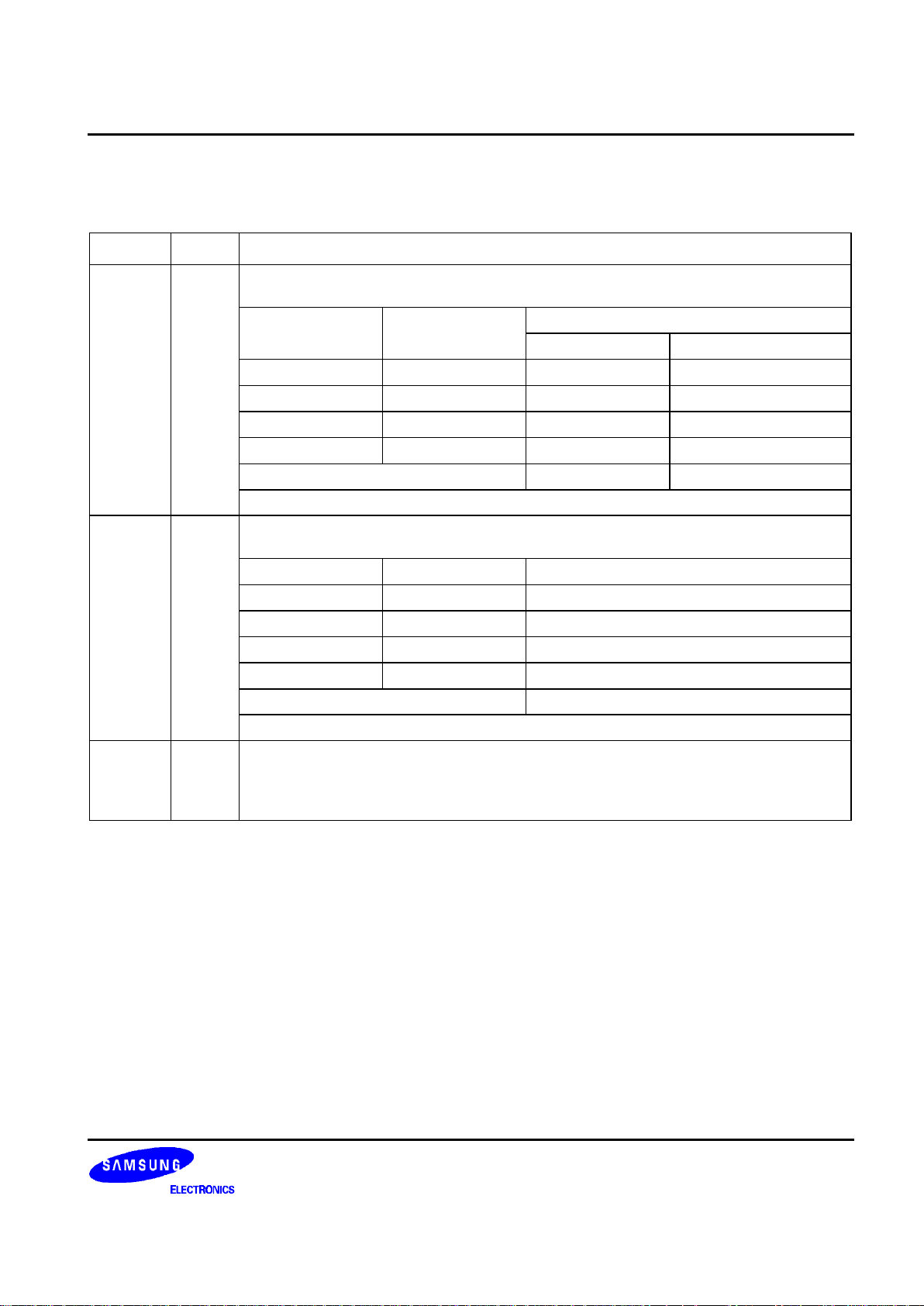

KS0713 Specification Revision History

Version Content Date

2.0 Neglect the more past version than version 2.0 Nov.1998

2.1

fOSC = 16kHz (Typ.) → 22kHz (Typ.): For removing flicker phenomenon

Temperature coefficient (when TEMPS = L): -0.0%/°C → -0.05%/°C

Nov.1998

3.0

Modified some syntax errors

Voltage regulator reference voltage [VREF]: TBD → 2.0

Modified voltage regulator block of “Functional Description”

Nov.1998

3.1

VLCD absolute maximum rating: 15.0V → 17.0V

Power consumption: 100µA → 80µA

3.2

Oscillator frequency (1): 19 (Min.) →17 (Min.), 25 (Max.) →27 (Max.)

Oscillator frequency (2): 22 (Min.) →20 (Min.), 28 (Max.) →30 (Max.)

3.3

Modified Y-axis values of “Pad Center Coordinates”

Modified the contents of “Referential Instruction Setup Flow”

3.4 Word-processor version change Apr.1999

3.5

Modified error: pad No.113 (COMS) Y Coordinate: -1210 → -1140 (after)

Oct.1999

4.0

Change VDD Range : 2.4V to 5.5V → 2.4V to 3.6V

Jan.2000

KS0713 65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD

3

CO

NTENTS

INTRODUCTION ..................................................................................................................................................1

FEATURES..........................................................................................................................................................1

BLOCK DIAGRAM...............................................................................................................................................3

PAD CONFIGURATION .......................................................................................................................................4

PAD CENTER COORDINATES ............................................................................................................................5

PIN DESCRIPTION ..............................................................................................................................................8

POWER SUPPLY ..........................................................................................................................................8

LCD DRIVER SUPPLY..................................................................................................................................8

SYSTEM CONTROL .....................................................................................................................................9

MICROPROCESSOR INTERFACE.............................................................................................................11

LCD DRIVER OUTPUTS.............................................................................................................................13

FUNCTIONAL DESCRIPTION............................................................................................................................ 14

MICROPROCESSOR INTERFACE.............................................................................................................14

DISPLAY DATA RAM (DDRAM)..................................................................................................................18

LCD DISPLAY CIRCUITS............................................................................................................................21

LCD DRIVER CIRCUIT ...............................................................................................................................23

POWER SUPPLY CIRCUITS ......................................................................................................................24

REFERECE CIRCUIT EXAMPLES..............................................................................................................31

RESET CIRCUIT.........................................................................................................................................33

INSTRUCTION DESCRIPTION...........................................................................................................................34

SPECIFICATIONS..............................................................................................................................................48

ABSOLUTE MAXIMUM RATINGS...............................................................................................................48

DC CHARACTERISTICS .............................................................................................................................49

REFERENCE DATA....................................................................................................................................52

AC CHARACTERISTICS.............................................................................................................................54

REFERENCE APPLICATIONS........................................................................................................................... 58

MICROPROCESSOR INTERFACE.............................................................................................................58

CONNECTIONS BETWEEN KS0713 AND LCD PANEL..............................................................................59

TCP PIN LAYOUT (SAMPLE)......................................................................................................................64

KS0713 65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD

1

INTRODUCTION

The KS0713 is a driver & controller LSI for graphic dot-matrix liquid crystal display systems. It contains 65

commons and 132 segments driver circuits. This chip is connected directly to a microprocessor, accepts serial or

8-bit parallel display data and stores in an on-chip Display Data RAM of 65 x 132 bits. It provides a high-flexible

display section due to 1-to-1 correspondence between on-chip display data RAM bits and LCD panel pixels. And it

performs display data RAM read/write operation with no externally operating clock to minimize power

consumption. In addition, because it contains power supply circuits necessary to drive liquid crystal, it is possible

to make a display system with the fewest components.

FEATURES

Driver Output Circuits

− 65 common outputs / 132 segment outputs

On-chip Display Data RAM

− Capacity: 65 x 132 = 8,580 bits

Applicable Duty Ratios

Duty ratio Applicable LCD bias Maximum display area

1/65 1/7 or 1/9

65 × 132

1/49 1/6 or 1/8

49 × 132

1/33 1/5 or 1/6

33 × 132

Microprocessor Interface

− 8-bit parallel bi-directional interface with 6800-series or 8080-series

− Serial interface (only write operation) available

Function Set

− Various instructions sets

− H/W, S/W reset capable

Built-in Analog Circuit

− On-chip oscillator circuit

− Voltage converter (x2, x3, x4, x5)

− Voltage regulator (temperature coefficient: -0.05%/°C, -0.2%/°C)

− Voltage follower

− Electronic contrast control function (64 steps)

Operating Voltage Range

− Supply voltage (VDD): 2.4 to 3.6 V

− LCD driving voltage (VLCD = V0 - VSS): 4.0 to 15.0 V

Low Power Consumption

− 70 µΑ Typ. (VDD = 3V, x4 boosting, V0 = 11V, internal power supply ON)

− 10 µΑ Max. (during power save [standby] mode)

Package Type

− Gold bumped chip or TCP

65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD KS0713

2

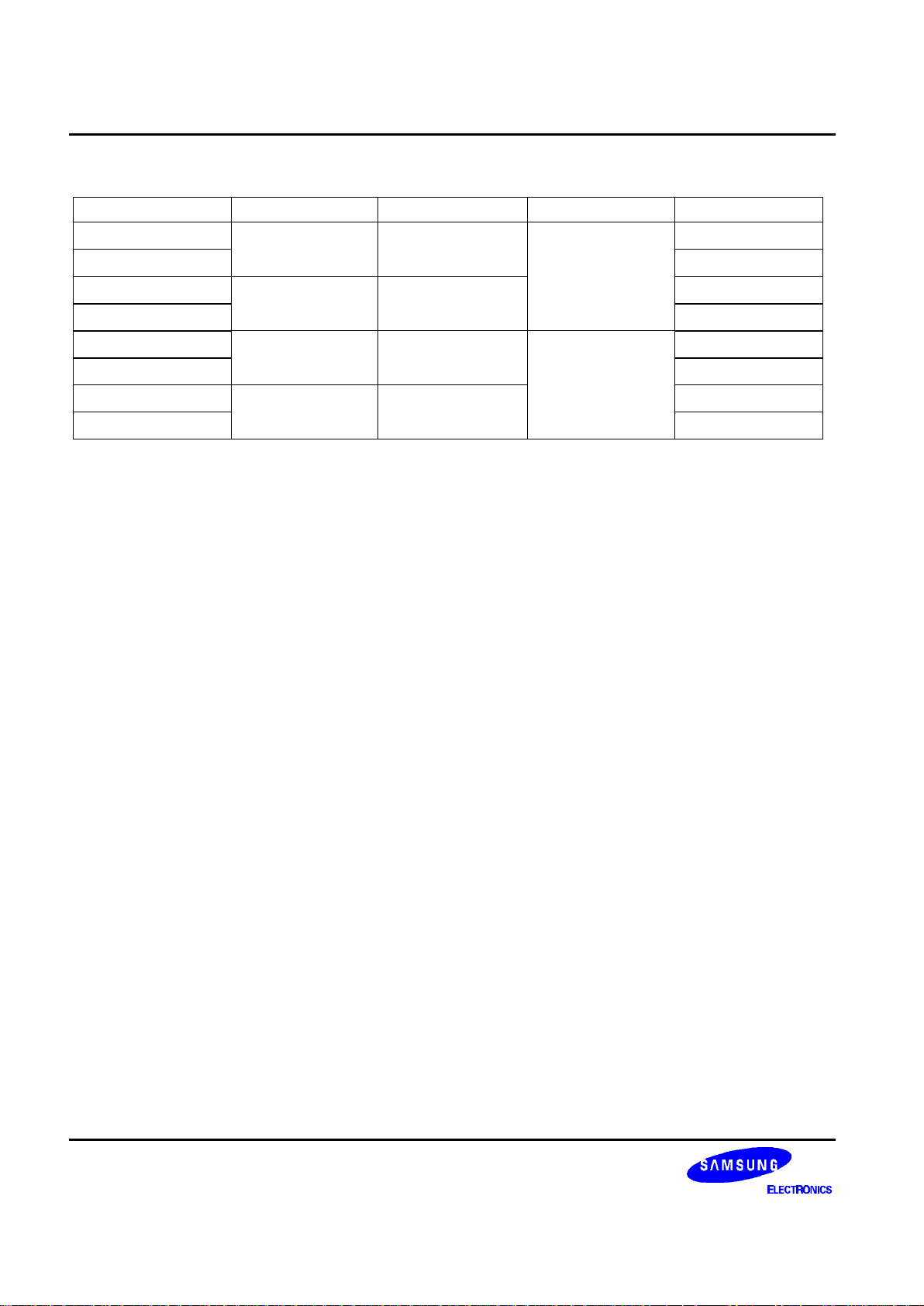

Series Specifications

Product code TEMPS pin Temp. coefficient Package Chip thickness

KS0713UM-L0CC

670 µm

KS0713UM-L4CC

0

(VSS connected)

-0.05%/°C

470 µm

KS0713UM-H0CC

670 µm

KS0713UM-H4CC

1

(VDD connected)

-0.2%/°C

COG

470 µm

KS0713TB-XX-L0TF

670 µm

KS0713TB-XX-L4TF

0

(VSS connected)

-0.05%/°C

470 µm

KS0713TB-XX-H0TF

670 µm

KS0713TB-XX-H4TF

1

(VDD connected)

-0.2%/°C

TCP

470 µm

* XX: TCP ordering number

KS0713 65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD

3

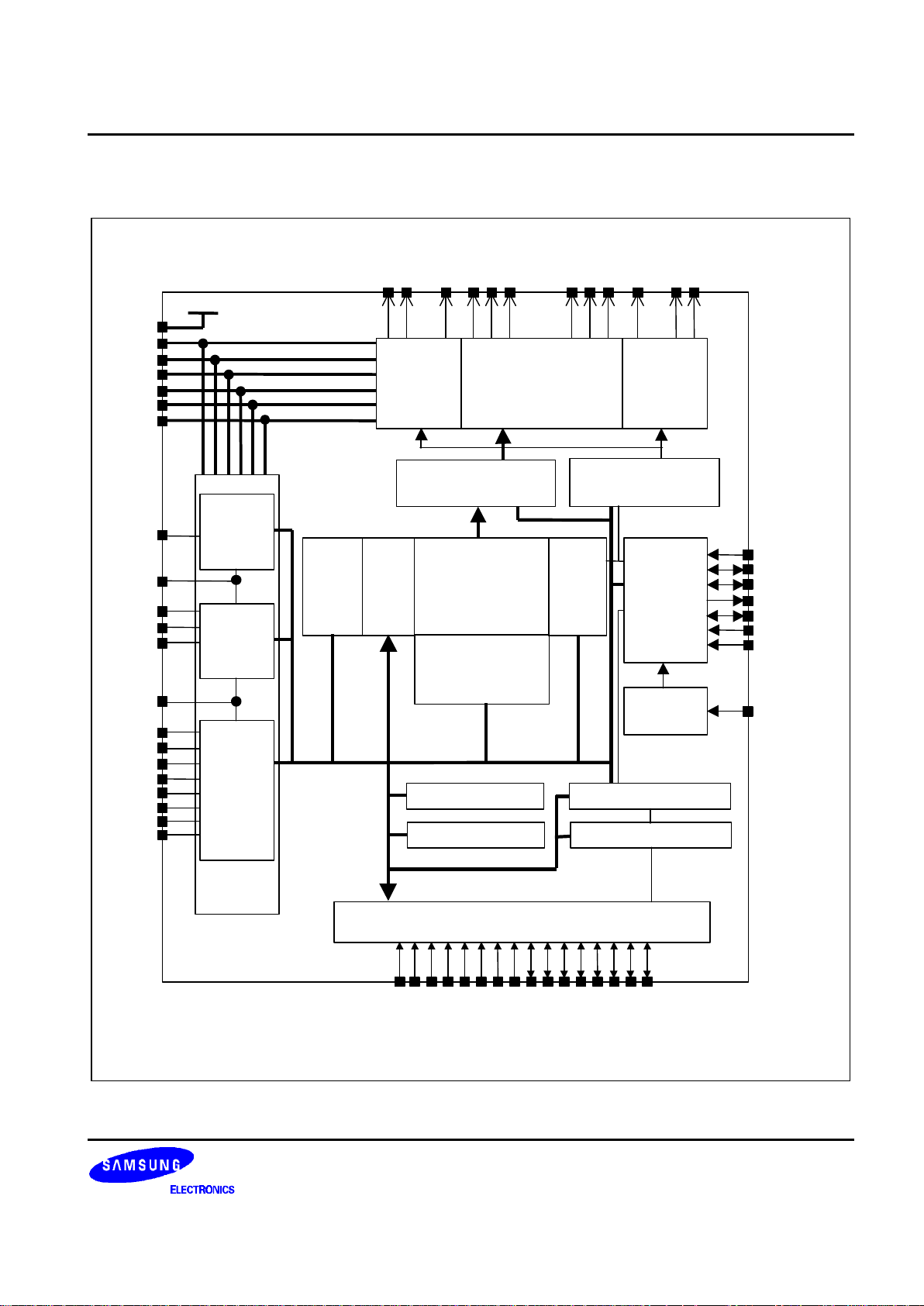

BLOCK DIAGRAM

MS

CL

M

FRS

DISP

DUTY0

DUTY1

VDD

V0

V1

V2

V3

V4

VSS

HPMB

V0

VR

INTRS

TEMPS

VOUT

C1-

C1+

C2-

C2+

C3-

C3+

DCDC5B

BSTS

V / C

CIRCUIT

V / R

CIRCUIT

V / F

CIRCUIT

33 COMMON

DRIVER

CIRCUITS

MPU INTERFACE (PARALLEL & SERIAL)

INSTRUCTION DECODERBUS HOLDER

COLUMN ADDRESS

CIRCUIT

LINE

ADDRESS

CIRCUIT

PAGE

ADDRESS

CIRCUIT

DISPLAY DATA RAM

65 X 132 = 8,580 Bits

SEGMENT CONTROLLER

DISPLAY

TIMING

GENERATOR

CIRCUIT

COMMON CONTROLLER

DB0

DB1

DB2

DB3

DB4

DB5

DB6(SCLK)

DB7(SID)

MI

RESETB

PS

RW_WR

E_RD

RS

CS2

CS1B

COMS

COM64

:

COM33

SEG132

SEG131

SEG130

:

:

SEG3

SEG2

SEG1

COM32

:

COM1

COMS

OSCILLATOR

132 SEGMENT

DRIVER CIRCUITS

33 COMMON

DRIVER

CIRCUITS

I/O

BUFFER

STATUS REGISTER INSTRUCTION REGISTER

CLS

Figure 1. Block Diagram

65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD KS0713

4

PAD CONFIGURATION

ррр ррррррррррррррррррр

- - - - - - - - - -

ррррррррррррррррррр

ððð

Y

148

287

147

288

111

324

110

1

KS0713

(TOP VIEW)

(0,0)

X

рррррррррррррррррррррр

- - - - - - - - - -

ррррррррррррррррррррррр

ðððð ððð

ðððð

- - - -

ððð

Figure 2. KS0713 Chip Configuration

Table 1. KS0713 Pad Dimensions

Size

Items Pad No.

X Y

Unit

Chip size - 10860 2920

1 to 110 90

Pad pitch

111 to 324 70

1 to 110 56 114

111 to 147 108 50

148 to 287 50 108

Bumped

pad size

288 to 324 108 50

Bumped pad height 1 to 324 17 (Typ.)

µm

COG Align Key Coordinate ILB Align Key Coordinate

30µm 30µm 30µm

(-5065, +1302)

30µm 30µm 30µm

(+5065, +1317)

30

µ

m

30

µ

m

30

µ

m

60

µ

m

30

µ

m

42µm 108µm

42

µ

m

108

µ

m

42

µ

m

108

µ

m

(-5060, -1180)

(+5060, -1180)

42µm108µm

KS0713 65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD

5

PAD CENTER COORDINATES

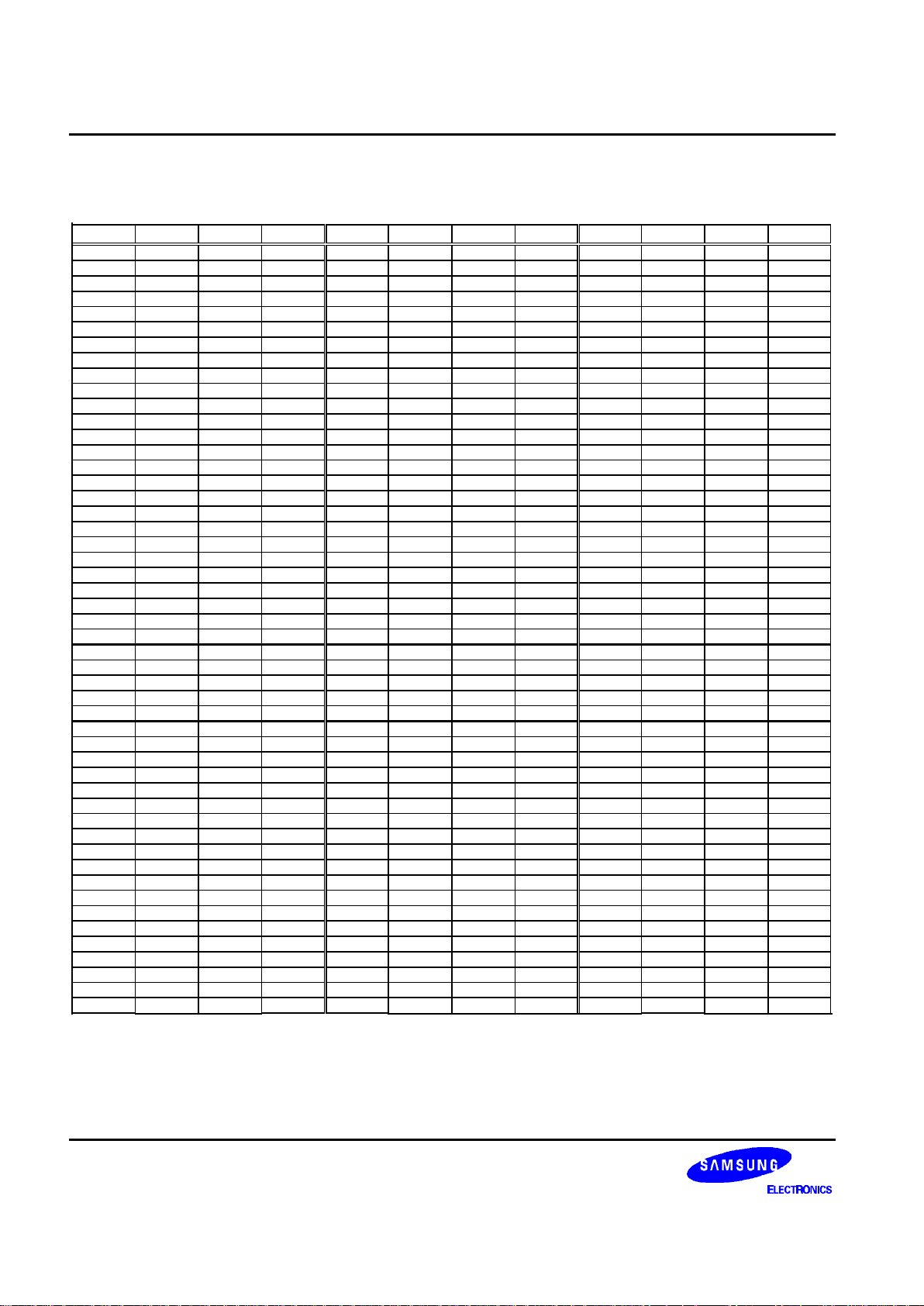

Table 2. Pad Center Coordinates

[Unit: µm]

No.

Name

XYNo.

Name

XYNo.

Name

X

Y

1

DUMMY

-4905

-133651VDD

-405

-1336

101

BSTS

4095

-13362DUMMY

-4815

-133652VDD

-315

-1336

102

DCDC5B

4185

-13363FRS

-4725

-133653VDD

-225

-1336

103

VDD

4275

-13364M

-4635

-133654VDD

-135

-1336

104

HPM

4365

-13365CL

-4545

-133655VDD

-45

-1336

105

INTRS

4455

-13366DISP

-4455

-133656VDD45-1336

106

VSS

4545

-13367VSS

-4365

-133657VOUT

135

-1336

107

TEMPS

4635

-13368CS1B

-4275

-133658VOUT

225

-1336

108

VDD

4725

-13369CS2

-4185

-133659VOUT

315

-1336

109

DUMMY

4815

-133610VDD

-4095

-133660VOUT

405

-1336

110

DUMMY

4905

-133611RESETB

-4005

-133661C3+

495

-1336

111

DUMMY

5271

-128012RS

-3915

-133662C3+

585

-1336

112

DUMMY

5271

-121013VSS

-3825

-133663C3+

675

-1336

113

COMS

5271

-114014RW_WR

-3735

-133664C3+

765

-1336

114

COM1

5271

-107015E_RD

-3645

-133665C3-

855

-1336

115

COM2

5271

-100016VDD

-3555

-133666C3-

945

-1336

116

COM3

5271

-93017DB0

-3465

-133667C3-

1035

-1336

117

COM4

5271

-86018DB1

-3375

-133668C3-

1125

-1336

118

COM5

5271

-79019DB2

-3285

-133669C1+

1215

-1336

119

COM6

5271

-72020DB3

-3195

-133670C1+

1305

-1336

120

COM7

5271

-65021DB4

-3105

-133671C1+

1395

-1336

121

COM8

5271

-58022DB5

-3015

-133672C1+

1485

-1336

122

COM9

5271

-51023DB6

-2925

-133673C1-

1575

-1336

123

COM10

5271

-44024DB7

-2835

-133674C1-

1665

-1336

124

COM11

5271

-37025VSS

-2745

-133675C1-

1755

-1336

125

COM12

5271

-30026VDD

-2655

-133676C1-

1845

-1336

126

COM13

5271

-23027VDD

-2565

-133677C2+

1935

-1336

127

COM14

5271

-16028VDD

-2475

-133678C2+

2025

-1336

128

COM15

5271

-9029DUTY0

-2385

-133679C2+

2115

-1336

129

COM16

5271

-2030DUTY1

-2295

-133680C2+

2205

-1336

130

COM17

52715031

VSS

-2205

-133681C2-

2295

-1336

131

COM18

5271

12032MS

-2115

-133682C2-

2385

-1336

132

COM19

5271

19033CLS

-2025

-133683C2-

2475

-1336

133

COM20

5271

26034VDD

-1935

-133684C2-

2565

-1336

134

COM21

5271

33035MI

-1845

-133685VSS

2655

-1336

135

COM22

5271

40036PS

-1755

-133686VSS

2745

-1336

136

COM23

5271

47037VSS

-1665

-133687VR

2835

-1336

137

COM24

5271

54038VSS

-1575

-133688VR

2925

-1336

138

COM25

5271

61039VSS

-1485

-133689V0

3015

-1336

139

COM26

5271

68040VSS

-1395

-133690V0

3105

-1336

140

COM27

5271

75041VSS

-1305

-133691V1

3195

-1336

141

COM28

5271

82042VSS

-1215

-133692V1

3285

-1336

142

COM29

5271

89043VSS

-1125

-133693V2

3375

-1336

143

COM30

5271

96044VSS

-1035

-133694V2

3465

-1336

144

COM31

5271

103045VSS

-945

-133695V3

3555

-1336

145

COM32

5271

110046VSS

-855

-133696V3

3645

-1336

146

DUMMY

5271

117047VDD

-765

-133697V4

3735

-1336

147

DUMMY

5271

124048VDD

-675

-133698V4

3825

-1336

148

DUMMY

4865

130149VDD

-585

-133699VSS

3915

-1336

149

DUMMY

4795

130150VDD

-495

-1336

100

VSS

4005

-1336

150

DUMMY

4725

1301

65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD KS0713

6

Table 2. Pad Center Coordinates (Continued)

[Unit: µm]

No. Name X Y No. Name X Y No. Name X Y

151 DUMMY 4655 1301 201 SEG50 1155 1301 251 SEG100 -2345 1301

152 SEG1 4585 1301 202 SEG51 1085 1301 252 SEG101 -2415 1301

153 SEG2 4515 1301 203 SEG52 1015 1301 253 SEG102 -2485 1301

154 SEG3 4445 1301 204 SEG53 945 1301 254 SEG103 -2555 1301

155 SEG4 4375 1301 205 SEG54 875 1301 255 SEG104 -2625 1301

156 SEG5 4305 1301 206 SEG55 805 1301 256 SEG105 -2695 1301

157 SEG6 4235 1301 207 SEG56 735 1301 257 SEG106 -2765 1301

158 SEG7 4165 1301 208 SEG57 665 1301 258 SEG107 -2835 1301

159 SEG8 4095 1301 209 SEG58 595 1301 259 SEG108 -2905 1301

160 SEG9 4025 1301 210 SEG59 525 1301 260 SEG109 -2975 1301

161 SEG10 3955 1301 211 SEG60 455 1301 261 SEG110 -3045 1301

162 SEG11 3885 1301 212 SEG61 385 1301 262 SEG111 -3115 1301

163 SEG12 3815 1301 213 SEG62 315 1301 263 SEG112 -3185 1301

164 SEG13 3745 1301 214 SEG63 245 1301 264 SEG113 -3255 1301

165 SEG14 3675 1301 215 SEG64 175 1301 265 SEG114 -3325 1301

166 SEG15 3605 1301 216 SEG65 105 1301 266 SEG115 -3395 1301

167 SEG16 3535 1301 217 SEG66 35 1301 267 SEG116 -3465 1301

168 SEG17 3465 1301 218 SEG67 -35 1301 268 SEG117 -3535 1301

169 SEG18 3395 1301 219 SEG68 -105 1301 269 SEG118 -3605 1301

170 SEG19 3325 1301 220 SEG69 -175 1301 270 SEG119 -3675 1301

171 SEG20 3255 1301 221 SEG70 -245 1301 271 SEG120 -3745 1301

172 SEG21 3185 1301 222 SEG71 -315 1301 272 SEG121 -3815 1301

173 SEG22 3115 1301 223 SEG72 -385 1301 273 SEG122 -3885 1301

174 SEG23 3045 1301 224 SEG73 -455 1301 274 SEG123 -3955 1301

175 SEG24 2975 1301 225 SEG74 -525 1301 275 SEG124 -4025 1301

176 SEG25 2905 1301 226 SEG75 -595 1301 276 SEG125 -4095 1301

177 SEG26 2835 1301 227 SEG76 -665 1301 277 SEG126 -4165 1301

178 SEG27 2765 1301 228 SEG77 -735 1301 278 SEG127 -4235 1301

179 SEG28 2695 1301 229 SEG78 -805 1301 279 SEG128 -4305 1301

180 SEG29 2625 1301 230 SEG79 -875 1301 280 SEG129 -4375 1301

181 SEG30 2555 1301 231 SEG80 -945 1301 281 SEG130 -4445 1301

182 SEG31 2485 1301 232 SEG81 -1015 1301 282 SEG131 -4515 1301

183 SEG32 2415 1301 233 SEG82 -1085 1301 283 SEG132 -4585 1301

184 SEG33 2345 1301 234 SEG83 -1155 1301 284 DUMMY -4655 1301

185 SEG34 2275 1301 235 SEG84 -1225 1301 285 DUMMY -4725 1301

186 SEG35 2205 1301 236 SEG85 -1295 1301 286 DUMMY -4795 1301

187 SEG36 2135 1301 237 SEG86 -1365 1301 287 DUMMY -4865 1301

188 SEG37 2065 1301 238 SEG87 -1435 1301 288 DUMMY -5271 1240

189 SEG38 1995 1301 239 SEG88 -1505 1301 289 DUMMY -5271 1170

190 SEG39 1925 1301 240 SEG89 -1575 1301 290 COMS -5271 1100

191 SEG40 1855 1301 241 SEG90 -1645 1301 291 COM64 -5271 1030

192 SEG41 1785 1301 242 SEG91 -1715 1301 292 COM63 -5271 960

193 SEG42 1715 1301 243 SEG92 -1785 1301 293 COM62 -5271 890

194 SEG43 1645 1301 244 SEG93 -1855 1301 294 COM61 -5271 820

195 SEG44 1575 1301 245 SEG94 -1925 1301 295 COM60 -5271 750

196 SEG45 1505 1301 246 SEG95 -1995 1301 296 COM59 -5271 680

197 SEG46 1435 1301 247 SEG96 -2065 1301 297 COM58 -5271 610

198 SEG47 1365 1301 248 SEG97 -2135 1301 298 COM57 -5271 540

199 SEG48 1295 1301 249 SEG98 -2205 1301 299 COM56 -5271 470

200

SEG49

1225

1301

250

SEG99

-2275

1301

300

COM55

-5271

400

KS0713 65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD

7

Table 2. Pad Center Coordinates (Continued)

[Unit: µm]

No. Name X Y No. Name X Y No. Name X Y

301 COM54 -5271 330

302 COM53 -5271 260

303 COM52 -5271 190

304 COM51 -5271 120

305 COM50 -5271 50

306 COM49 -5271 -20

307 COM48 -5271 -90

308 COM47 -5271 -160

309 COM46 -5271 -230

310 COM45 -5271 -300

311 COM44 -5271 -370

312 COM43 -5271 -440

313 COM42 -5271 -510

314 COM41 -5271 -580

315 COM40 -5271 -650

316 COM39 -5271 -720

317 COM38 -5271 -790

318 COM37 -5271 -860

319 COM36 -5271 -930

320 COM35 -5271 -1000

321 COM34 -5271 -1070

322 COM33 -5271 -1140

323 DUMMY -5271 -1210

324 DUMMY -5271 -1280

65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD KS0713

8

PIN DESCRIPTION

POWER SUPPLY

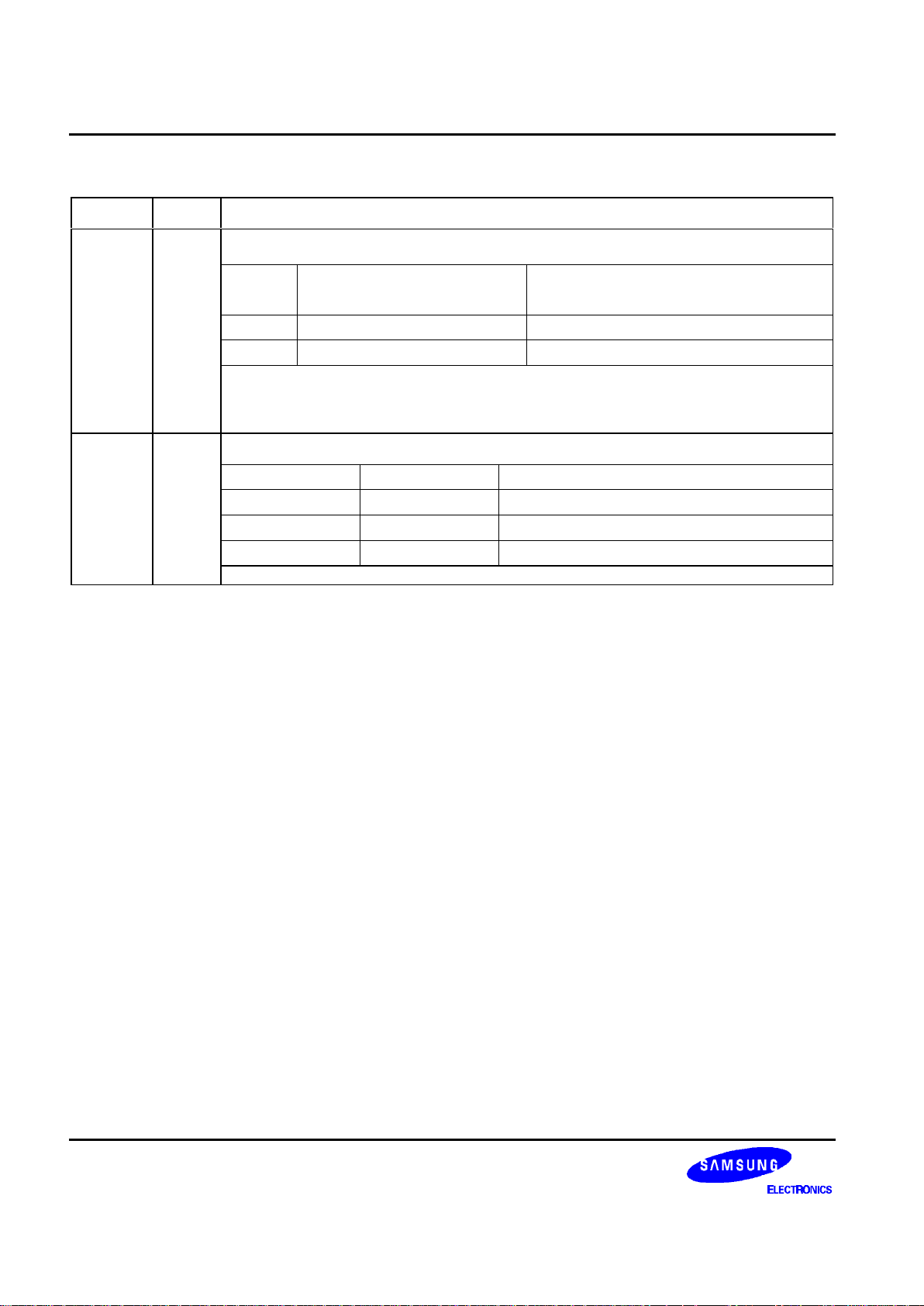

Table 3. Power Supply Pin Description

Name I/O Description

VDD Supply Power supply

VSS Supply Ground

LCD driver supply voltages

The voltage determined by LCD pixel is impedance-converted by an operational amplifier

for application.

Voltages should have the following relationship;

V0 ≥ V1 ≥ V2 ≥ V3 ≥ V4 ≥ VSS

When the internal power circuit is active, these voltages are generated as following table

according to the state of LCD Bias.

LCD bias V1 V2 V3 V4

1/9 bias (8/9) x V0 (7/9) x V0 (2/9) x V0 (1/9) x V0

1/8 bias (7/8) x V0 (6/8) x V0 (2/8) x V0 (1/8) x V0

1/7 bias (6/7) x V0 (5/7) x V0 (2/7) x V0 (1/7) x V0

1/6 bias (5/6) x V0 (4/6) x V0 (2/6) x V0 (1/6) x V0

1/5 bias (4/5) x V0 (3/5) x V0 (2/5) x V0 (1/5) x V0

V0

V1

V2

V3

V4

I/O

LCD DRIVER SUPPLY

Table 4. LCD Driver Supply Pin Description

Name I/O Description

C1- O Capacitor 1 negative connection pin for voltage converter

C1+ O Capacitor 1 positive connection pin for voltage converter

C2- O Capacitor 2 negative connection pin for voltage converter

C2+ O Capacitor 2 positive connection pin for voltage converter

C3- O Capacitor 3 negative connection pin for voltage converter

C3+ O Capacitor 3 positive connection pin for voltage converter

VOUT I/O Voltage converter input / output pin

DCDC5B I

5 times boosting circuit enable input pin

When this pin is low in 4 times boosting circuit, the 5-times boosting voltage appears at

VOUT.

VR I

V0 voltage adjustment pin

It is valid only when on-chip resistors are not used (INTRS = “L”).

KS0713 65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD

9

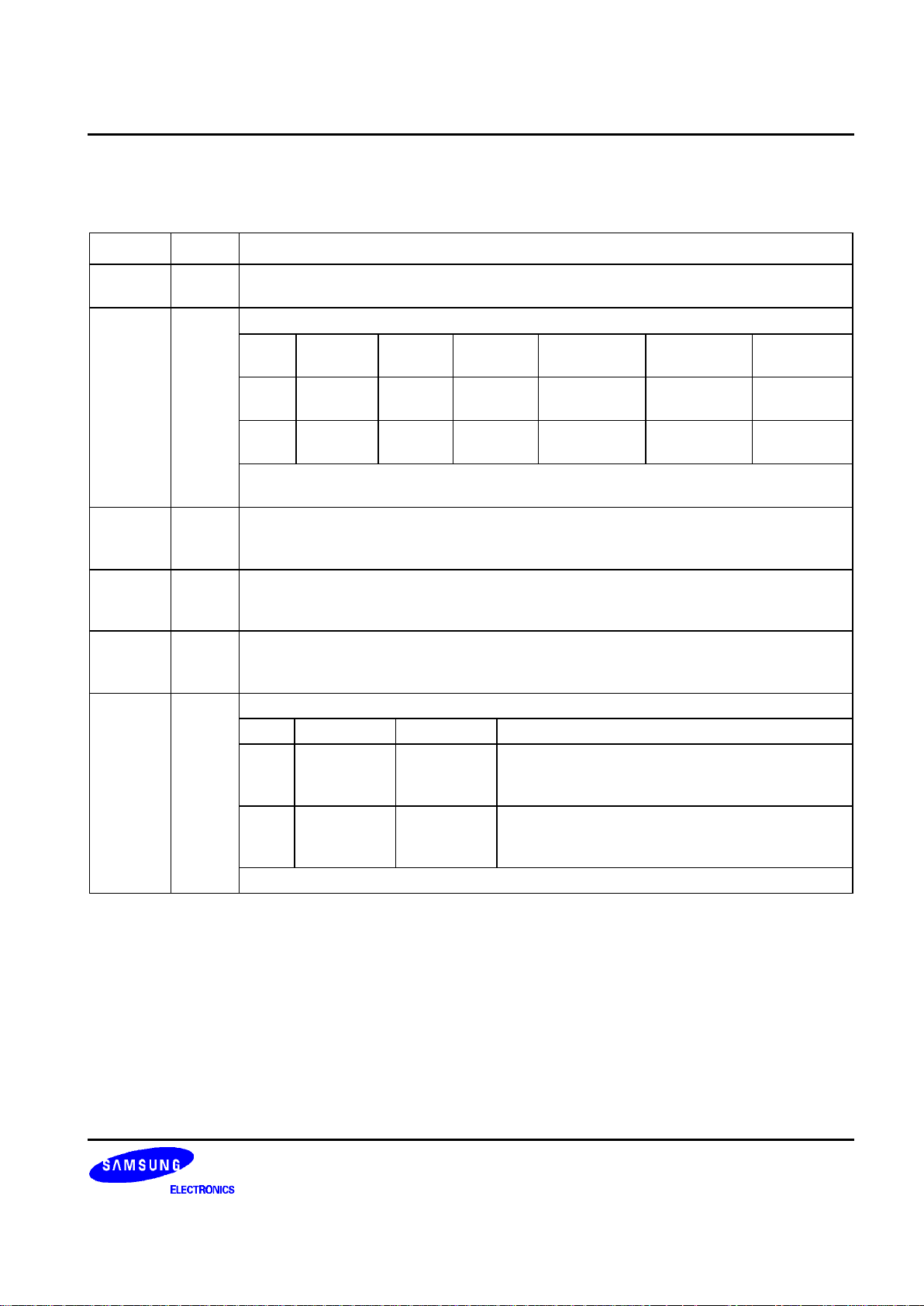

SYSTEM CONTROL

Table 5. System Control Pin Description

Name I/O Description

Master / Slave operation select pin

− MS = "H": master operation

− MS = "L": slave operation

The following table depends on the MS status.

MS CLS

OSC

circuit

Power

supply

circuit

CL M FRS DISP

H Enabled Enabled Output Output Output Output

H

L Disabled Enabled Input Output Output Output

L - Disabled Disabled Input Input Output Input

MS I

CLS I

Built-in oscillator circuit enable / disable select pin

− CLS = “H”: enable

− CLS = “L”: disable (external display clock input to CL pin)

CL I/O

Display clock input / output pin

When the KS0713 is used in master/slave mode (multi-chip), the CL pins must be

connected each other.

M I/O

LCD AC signal input / output pin

When the KS0713 is used in master/slave mode (multi-chip), the M pins must be

connected each other.

− MS = “H”: output

− MS = “L”: input

FRS O

Static driver segment output pin

This pin is used together with the M pin.

DISP I/O

LCD display blanking control input / output

When KS0713 is used in master/slave mode (multi-chip), the DISP pins must be

connected each other.

− MS = “H”: output

− MS = “L”: input

INTRS I

Internal resistors select pin

This pin selects the resistors for adjusting V0 voltage level.

− INTRS = "H": use the internal resistors.

− INTRS = "L": use the external resistors.

V0 voltage is controlled with VR pin and external resistive divider.

HPM I

Power control pin of the power supply circuit for LCD driver

− HPM = "H": high power mode

− HPM = "L": normal mode

This pin is valid in master operation.

TEMPS I

Selects temperature coefficient of the reference voltage

− TEMPS = "L": -0.05%/°C

− TEMPS = "H": -0.2%/°C

65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD KS0713

10

Table 5. System Control Pin Description (Continued)

Name I/O Description

Selects input voltages of the built-in voltage converter

BSTS

Voltage converter

input voltage

Remarks

L 4V VDD > 4V

H VDD

2.4V ≤ VDD ≤ 3.6V

BSTS I

When BSTS pin is “L”, VDD must be higher than 4V in four times boosting.

NOTE: Because the maximum voltage of VDD has been changed to 3.6V, we strongly

recommend that BSTS pin should be fixed to “H”.

The LCD driver duty ratio depends on the following table

DUTY1 DUTY0 Duty ratio

L L 1/33

L H 1/49

H L/H 1/65

DUTY0

DUTY1

I

KS0713 65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD

11

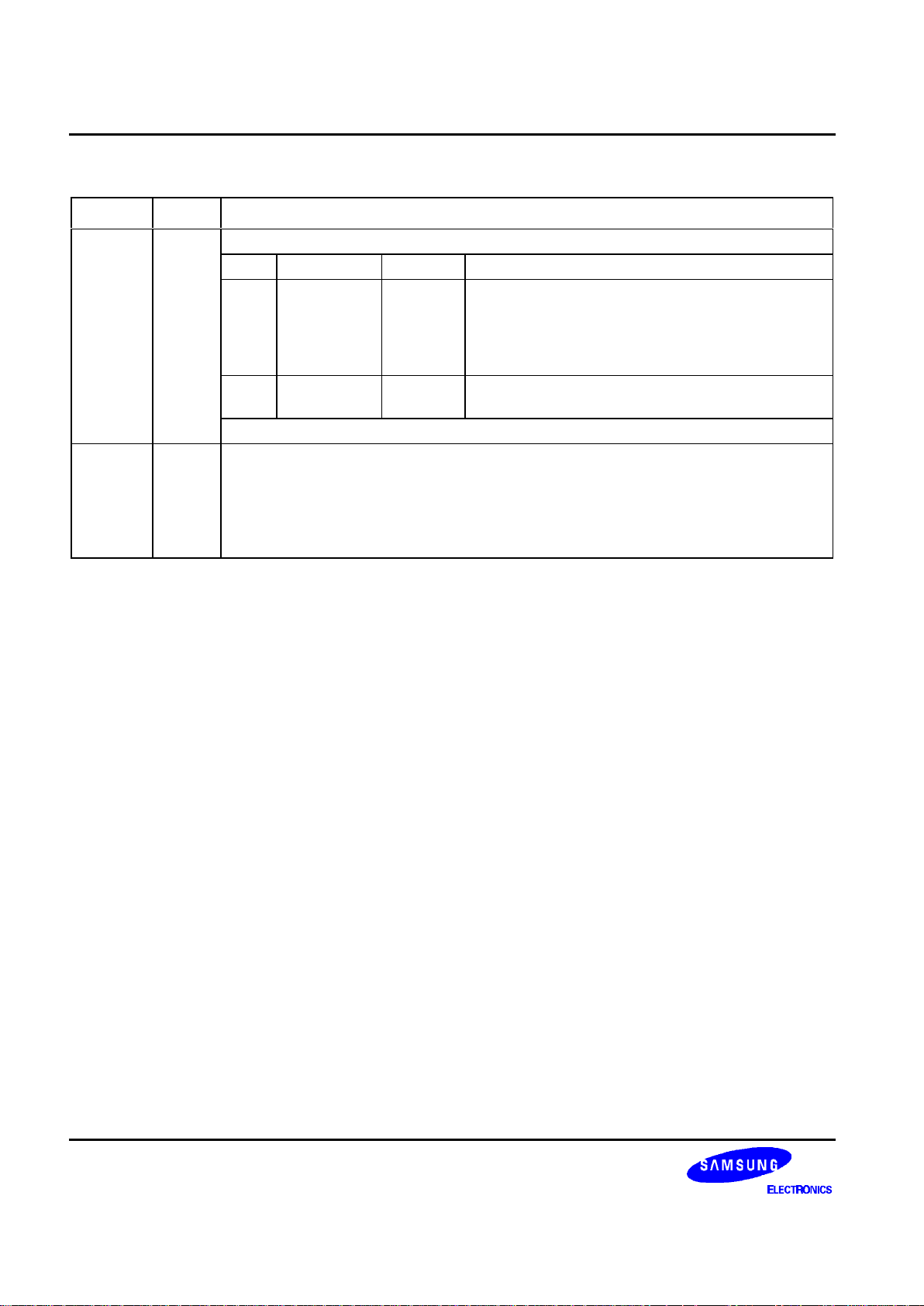

MICROPROCESSOR INTERFACE

Table 6. Microprocessor Interface Pin Description

Name I/O Description

RESETB I

Reset input pin

When RESETB is “L”, initialization is executed.

Parallel / Serial data input select input

PS

Interface

mode

Chip

select

Data /

instruction

Data Read / Write Serial clock

H Parallel

CS1B,

CS2

RS DB0 to DB7

E_RD

RW_WR

-

L Serial

CS1B,

CS2

RS SID(DB7) Write only SCLK(DB6)

PS I

*NOTE: In serial mode, it is impossible to read data from the on-chip RAM. And DB0 to

DB5 are high impedance and E_RD and RW_WR must be fixed to either “H” or “L”.

MI I

Microprocessor interface selects input pin

− MI = "H": 6800-series MPU interface

− MI = "L": 8080-series MPU interface

CS1B

CS2

I

Chip select input pins

Data / instruction I/O is enabled only when CS1B is “L” and CS2 is “H”.

When chip select is non-active, DB0 to DB7 may be high impedance.

RS I

Register select input pin

− RS = "H": DB0 to DB7 are display data

− RS = "L": DB0 to DB7 are control data

Read / Write execution control pin

MI MPU type RW_WR Description

H 6800-series RW

Read / Write control input pin

− RW = “H”: read

− RW = “L”: write

L 8080-series /WR

Write enable clock input pin

The data ON DB0 to DB7 are latched at the rising

edge of the /WR signal.

RW_WR I

65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD KS0713

12

Table 6. Microprocessor Interface Pin Description (Continued)

Name I/O Description

Read / Write execution control pin

MI MPU type E_RD Description

H 6800-series E

Read / Write control input pin

− RW = “H”: When E is “H”, DB0 to DB7 are in an

output status.

− RW = “L”: The data on DB0 to DB7 are latched at

the falling edge of the E signal.

L 8080-series /RD

Read enable clock input pin

When /RD is “L”, DB0 to DB7 are in an output status.

E_RD I

DB0

to

DB7

I/O

8-bit bi-directional data bus that is connected to the standard 8-bit microprocessor data

bus. When the serial interface selected (PS = "L");

− DB0 to DB5: high impedance

− DB6: serial input clock (SCLK)

− DB7: serial input data (SID)

When chip select is not active, DB0 to DB7 may be high impedance.

KS0713 65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD

13

LCD DRIVER OUTPUTS

Table 7. LCD Driver Outputs Pin Description

Name I/O Description

LCD segment driver outputs

The display data and the M signal control the output voltage of segment driver.

Segment driver output voltage

Display data M

Normal display Reverse display

H H V0 V2

H L VSS V3

L H V2 V0

L L V3 VSS

Power save mode VSS VSS

SEG1

to

SEG132

O

LCD common driver outputs

The internal scanning data and M signal control the output voltage of common driver.

Scan data M Common driver output voltage

H H VSS

H L V0

L H V1

L L V4

Power save mode VSS

COM1

to

COM64

O

COMS O

Common output for the icons

The output signals of two pins are same. When not used, these pins should be left open.

In multi-chip (master / slave) mode, all COMS pins on both master and slave units are the

same signal.

NOTE: DUMMY - These pins should be opened (floated).

65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD KS0713

14

FUNCTIONAL DESCRIPTION

MICROPROCESSOR INTERFACE

Chip Select Input

There are CS1B and CS2 pins for Chip Selection. The KS0713 can interface with an MPU only when CS1B is “L”

and CS2 is “H”. When these pins are set to any other combination, RS, E_RD, and RW_WR inputs are disabled

and DB0 to DB7 are to be high impedance. And, in case of serial interface, the internal shift register and the

counter are reset.

Parallel / Serial Interface

KS0713 has three types of interface with an MPU, which are one serial and two parallel interfaces. This parallel or

serial interface is determined by PS pin as shown in table 8.

Table 8. Parallel / Serial Interface Mode

PS Type CS1B CS2 MI Interface mode

H 6800-series MPU mode

H Parallel CS1B CS2

L 8080-series MPU mode

L Serial CS1B CS2

*×

Serial-mode

*× : Don't care

Parallel Interface (PS = "H")

The 8-bit bi-directional data bus is used in parallel interface and the type of MPU is selected by MI as shown in

table 9. The type of data transfer is determined by signals at RS, E_RD and RW_WR as shown in table10.

Table 9. Microprocessor Selection for Parallel Interface

MI CS1B CS2 RS E_RD RW_WR DB0 to DB7 MPU bus

H CS1B CS2 RS E RW DB0 to DB7 6800-series

L CS1B CS2 RS /RD /WR DB0 to DB7 8080-series

Table 10. Parallel Data Transfer

Common 6800-series 8080-series

RS

E_RD

(E)

RW_WR

(RW)

E_RD

(/RD)

RW_WR

(/WR)

Description

H H H L H Display data read out

H H L H L Display data write

L H H L H Register status read

L H L H L Writes to internal register (instruction)

KS0713 65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD

15

Serial Interface (PS = "L")

When the KS0713 is active, serial data (DB7) and serial clock (DB6) inputs are enabled. And not active, the

internal 8-bit shift register and the 3-bit counter are reset. Serial data can be read on the rising edge of serial clock

going into DB6 and processed as 8-bit parallel data on the eighth serial clock. Serial data input is display data

when RS is high and control data when RS is low. Since the clock signal (DB6) is easy to be affected by the

external noise caused by the line length, the operation check on the actual machine is recommended.

CS1B

CS2

SID

SCLK

RS

DB6DB7DB0DB1DB2DB3DB4DB5DB6DB7

Figure 3. Serial Interface Timing

Busy Flag

The Busy Flag indicates whether the KS0713 is operating or not. When DB7 is “H” in read status operation, this

device is in busy status and will accept only read status instruction. If the cycle time is correct, the microprocessor

needs not to check this flag before each instruction, which improves the MPU performance.

65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD KS0713

16

Data Transfer

The KS0713 uses bus holder and internal data bus for Data Transfer with the MPU. When writing data from the

MPU to on-chip RAM, data is automatically transferred from the bus holder to the RAM as shown in figure 4. And

when reading data from on-chip RAM to the MPU, the data for the initial read cycle is stored in the bus holder

(dummy read) and the MPU reads this stored data from bus holder for the next data read cycle as shown in figure

5. This means that a dummy read cycle must be inserted between each pair of address sets when a sequence of

address sets is executed. Therefore, the data of the specified address cannot be output with the read display data

instruction right after the address sets, but can be output at the second read of data.

RS

/WR

DB0 to DB7

N D(N) D(N+1) D(N+2) D(N+3)

Internal signals

MPU signals

/WR

BUS HOLDER

COLUMN ADDRESS

N N+1 N+2 N+3

N D(N) D(N+1) D(N+2) D(N+3)

Figure 4. Write Timing

KS0713 65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD

17

RS

/WR

/RD

DB0 to DB7

N

MPU signals

Dummy D(N) D(N+1)

Internal signals

/WR

/RD

BUS HOLDER

COLUMN ADDRESS

N

D(N)

D(N+1)

D(N+2)

N

N+1

N+2

N+3

Figure 5. Read Timing

65 COM / 132 SEG DRIVER & CONTROLLER FOR STN LCD KS0713

18

DISPLAY DATA RAM (DDRAM)

The Display Data RAM stores pixel data for the LCD. It is 65-row by 132-column addressable array. Each pixel

can be selected when the page and column addresses are specified. The 65 rows are divided into 8 pages of 8

lines and the 9th page with a single line (DB0 only). Data is read from or written to the 8 lines of each page

directly through DB0 to DB7. The display data of DB0 to DB7 from the microprocessor correspond to the LCD

common lines as shown in Figure 6. The microprocessor can read from and write to RAM through the I/O buffer.

Since the LCD controller operates independently, data can be written into RAM at the same time as data is being

displayed without causing the LCD flicker.

COM1 - -

COM2 - COM3 - COM4 - COM5 - -

DB0 0 0 1 - - 0

DB1 1 0 0 - - 1

DB2 0 1 1 - - 0

DB3 1 0 1 - - 0

DB4 0 0 0 - - 1

Display Data RAM LCD Display

Figure 6. RAM-to-LCD Data Transfer

Page Address Circuit

This circuit is for providing a Page Address to Display Data RAM shown in figure 8. It incorporates 4-bit Page

Address register changed by only the “Set Page” instruction. Page Address 8 (DB3 is “H”, but DB2, DB1 and DB0

are “L”) is a special RAM area for the icons and display data DB0 is only valid. When Page Address is above 8, it

is impossible to access to on-chip RAM.

Line Address Circuit

This circuit assigns DDRAM a Line Address corresponding to the first line (COM1) of the display. Therefore, by

setting line address repeatedly, it is possible to realize the screen scrolling and page switching without changing

the contents of on-chip RAM as shown in figure 8. It incorporates 6-bit line address register changed by only the

initial display line instruction and 6-bit counter circuit. At the beginning of each LCD frame, the contents of register

are copied to the line counter which is increased by CL signal and generates the Line Address for transferring the

132-bit RAM data to the display data latch circuit. However, display data of icons are not scrolled because the

MPU can not access Line Address of icons.

Loading...

Loading...