ON Semiconductor MC34152, MC33152, NCV33152 Technical data

MC33152DR2

MC34152, MC33152,

NCV33152

High Speed Dual

MOSFET Drivers

The MC34152/MC33152 are dual noninverting high speed drivers specifically designed for applications that require low current digital signals to drive large capacitive loads with high slew rates. These devices feature low input current making them CMOS/LSTTL logic compatible, input hysteresis for fast output switching that is independent of input transition time, and two high current totem pole outputs ideally suited for driving power MOSFETs. Also included is an undervoltage lockout with hysteresis to prevent system erratic operation at low supply voltages.

Typical applications include switching power supplies, dc−to−dc converters, capacitor charge pump voltage doublers/inverters, and motor controllers.

This device is available in dual−in−line and surface mount packages.

Features

•Pb−Free Packages are Available

•Two Independent Channels with 1.5 A Totem Pole Outputs

•Output Rise and Fall Times of 15 ns with 1000 pF Load

•CMOS/LSTTL Compatible Inputs with Hysteresis

•Undervoltage Lockout with Hysteresis

•Low Standby Current

•Efficient High Frequency Operation

•Enhanced System Performance with Common Switching Regulator Control ICs

•NCV Prefix for Automotive and Other Applications Requiring Site and Control Changes

|

|

VCC 6 |

|

|

|

+ |

|

|

|

- |

|

|

|

5.7V |

|

|

|

Drive Output A |

|

Logic |

|

7 |

|

Input A |

2 |

||

100k |

|||

|

|

|

|

Drive Output B |

|

Logic |

|

5 |

|

Input B |

4 |

||

100k |

|||

|

|

||

|

|

GND 3 |

http://onsemi.com

|

|

MARKING |

|

|

|

DIAGRAMS |

|

|

8 |

|

|

|

PDIP−8 |

MC3x152P |

|

|

P SUFFIX |

AWL |

|

8 |

CASE 626 |

YYWW |

|

1 |

1 |

|

|

|

|

||

|

|

8 |

|

8 |

SOIC−8 |

3x152 |

|

D SUFFIX |

ALYW |

||

|

|||

1 |

CASE 751 |

|

|

|

|

1 |

|

x |

= 3 or 4 |

|

|

A |

= Assembly Location |

||

WL, L = Wafer Lot |

|

||

YY, Y |

= Year |

WW, W |

= Work Week |

|

|

PIN CONNECTIONS

N.C. |

1 |

8 |

N.C. |

|

Logic Input A |

2 |

7 |

Drive Output A |

|

GND |

3 |

6 |

VCC |

|

Logic Input B |

4 |

|

5 |

Drive Output B |

|

||||

(Top View)

ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.

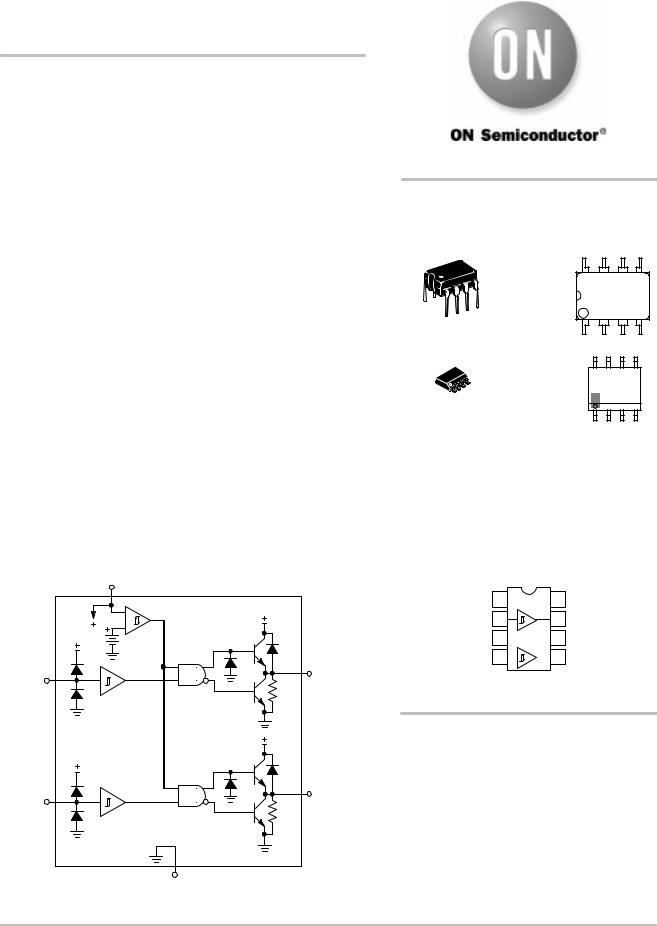

Figure 1. Representative Diagram

Semiconductor Components Industries, LLC, 2004 |

1 |

Publication Order Number: |

October, 2004 − Rev. 7 |

|

MC34152/D |

MC34152, MC33152, NCV33152

MAXIMUM RATINGS

|

Rating |

Symbol |

Value |

Unit |

|

|

|

|

|

Power Supply Voltage |

|

VCC |

20 |

V |

Logic Inputs (Note 1) |

|

Vin |

−0.3 to +V CC |

V |

Drive Outputs (Note 2) |

|

|

|

A |

Totem Pole Sink or Source Current |

|

IO |

1.5 |

|

Diode Clamp Current (Drive Output to VCC) |

IO(clamp) |

1.0 |

|

|

Power Dissipation and Thermal Characteristics |

|

|

|

|

D Suffix, Plastic Package Case 751 |

|

|

|

|

Maximum Power Dissipation @ TA = 50°C |

PD |

0.56 |

W |

|

Thermal Resistance, Junction−to−Air |

R JA |

180 |

°C/W |

|

P Suffix, Plastic Package, Case 626 |

|

|

|

|

Maximum Power Dissipation @ TA = 50°C |

PD |

1.0 |

W |

|

Thermal Resistance, Junction−to−Air |

R JA |

100 |

°C/W |

|

Operating Junction Temperature |

|

TJ |

+150 |

°C |

Operating Ambient Temperature |

MC34152 |

TA |

0 to +70 |

°C |

|

MC33152 |

|

−40 to +85 |

|

|

MC33152V, NCV33152 |

|

−40 to +125 |

|

|

|

|

|

|

Storage Temperature Range |

|

Tstg |

−65 to +150 |

°C |

Electrostatic Discharge Sensitivity (ESD) |

ESD |

|

V |

|

Human Body Model (HBM) |

|

|

2000 |

|

Machine Model (MM) |

|

|

200 |

|

|

|

|

|

|

Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values

(not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.

1.For optimum switching speed, the maximum input voltage should be limited to 10 V or VCC, whichever is less.

2.Maximum package power dissipation limits must be observed.

ORDERING INFORMATION

Device |

Package |

Shipping² |

|

MC34152D |

SOIC−8 |

98 Units / Rail |

|

|

|

|

|

MC34152DG |

SOIC−8 |

98 Units / Rail |

|

(Pb−Free) |

|||

|

|

||

|

|

|

|

MC34152DR2 |

SOIC−8 |

2500 Tape & Reel |

|

|

|

|

|

MC34152DR2G |

SOIC−8 |

2500 Tape & Reel |

|

(Pb−Free) |

|||

|

|

||

|

|

|

|

MC34152P |

PDIP−8 |

50 Units / Rail |

|

|

|

|

|

MC33152D |

SOIC−8 |

98 Units / Rail |

|

|

|

|

|

MC33152DR2 |

SOIC−8 |

2500 Tape & Reel |

|

|

|

|

|

MC33152P |

PDIP−8 |

50 Units / Rail |

|

|

|

|

|

MC33152PG |

PDIP−8 |

50 Units / Rail |

|

(Pb−Free) |

|||

|

|

||

|

|

|

|

MC33152VDR2 |

SOIC−8 |

2500 Tape & Reel |

|

|

|

|

|

NCV33152DR2* |

SOIC−8 |

2500 Tape & Reel |

|

|

|

|

|

NCV33152DR2G* |

SOIC−8 |

2500 Tape & Reel |

|

(Pb−Free) |

|||

|

|

||

|

|

|

²For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

*NCV prefix is for automotive and other applications requiring site and change control.

http://onsemi.com

2

MC34152, MC33152, NCV33152

ELECTRICAL CHARACTERISTICS (VCC = 12 V, for typical values TA = 25°C, for min/max values TA is the operating ambient temperature range that applies [Note 3], unless otherwise noted.)

Characteristics |

Symbol |

Min |

Typ |

Max |

Unit |

|

LOGIC INPUTS |

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Threshold Voltage |

|

|

|

|

|

V |

|

Output Transition High−to−Low State |

VIH |

− |

1.75 |

2.6 |

|

|

Output Transition Low−to−High State |

VIL |

0.8 |

1.58 |

− |

|

Input Current |

|

|

|

|

|

A |

High State (VIH = 2.6 V) |

|

IIH |

− |

100 |

300 |

|

Low State (VIL = 0.8 V) |

|

IIL |

− |

20 |

100 |

|

DRIVE OUTPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Voltage |

|

|

|

|

|

V |

Low State (Isink = 10 mA) |

|

VOL |

− |

0.8 |

1.2 |

|

(Isink = 50 mA) |

|

|

− |

1.1 |

1.5 |

|

(Isink = 400 mA) |

|

|

− |

1.8 |

2.5 |

|

High State (Isource = 10 mA) |

|

VOH |

10.5 |

11.2 |

− |

|

(Isource = 50 mA) |

|

|

10.4 |

11.1 |

− |

|

(Isource = 400 mA) |

|

|

10 |

10.8 |

− |

|

Output Pull−Down Resistor |

|

RPD |

− |

100 |

− |

k |

SWITCHING CHARACTERISTICS (TA = 25°C) |

|

|

|

|

|

|

Propagation Delay (CL = 1.0 nF) |

|

|

|

|

|

ns |

Logic Input to: Drive Output Rise (10% Input to 10% Output) |

tPLH (IN/OUT) |

− |

55 |

120 |

|

|

Drive Output Fall (90% Input to 90% Output) |

tPHL (IN/OUT) |

− |

40 |

120 |

|

|

Drive Output Rise Time (10% to 90%) |

CL = 1.0 nF |

tr |

− |

14 |

30 |

ns |

|

CL = 2.5 nF |

|

− |

36 |

− |

|

Drive Output Fall Time (90% to 10%) |

CL = 1.0 nF |

tf |

− |

15 |

30 |

ns |

|

CL = 2.5 nF |

|

− |

32 |

− |

|

TOTAL DEVICE |

|

|

|

|

|

|

|

|

|

|

|

|

|

Power Supply Current |

|

ICC |

|

|

|

mA |

Standby (Logic Inputs Grounded) |

|

|

− |

6.0 |

8.0 |

|

Operating (CL = 1.0 nF Drive Outputs 1 and 2, f = 100 kHz) |

|

− |

10.5 |

15 |

|

|

Operating Voltage |

|

VCC |

6.5 |

− |

18 |

V |

3. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

Tlow = 0°C for MC34152, −40 °C for MC33152, −40 °C for MC33152V

Thigh = +70°C for MC34152, +85°C for MC33152, +125°C for MC33152V

NCV33152: Tlow = −40 °C, Thigh = +125°C. Guaranteed by design.

http://onsemi.com

3

|

MC34152, MC33152, NCV33152 |

|

|

||

12V |

|

|

|

|

|

4.7 |

0.1 |

|

|

|

|

+ |

|

|

|

|

|

|

6 |

|

|

|

|

|

+ |

|

|

|

|

+ |

- |

|

|

|

|

|

|

|

|

|

|

|

5.7V |

Drive Output |

|

|

|

|

|

|

|

|

|

Logic Input |

|

7 |

|

|

|

2 |

|

|

|

|

|

100k |

|

|

|

90% |

|

50 |

CL |

5 V |

|

||

|

|

|

|||

|

Logic Input |

|

|

||

|

|

|

tr, tf ≤ 10 ns |

|

|

|

|

|

0 V |

10% |

|

|

|

|

|

|

|

|

|

5 |

|

tPLH |

tPHL |

4 |

|

|

|

||

100k |

|

|

|

||

|

|

|

|

10% |

|

|

|

|

|

|

|

|

|

|

Drive Output |

|

|

|

3 |

|

|

|

90% |

|

|

|

tr |

tf |

|

|

|

|

|

||

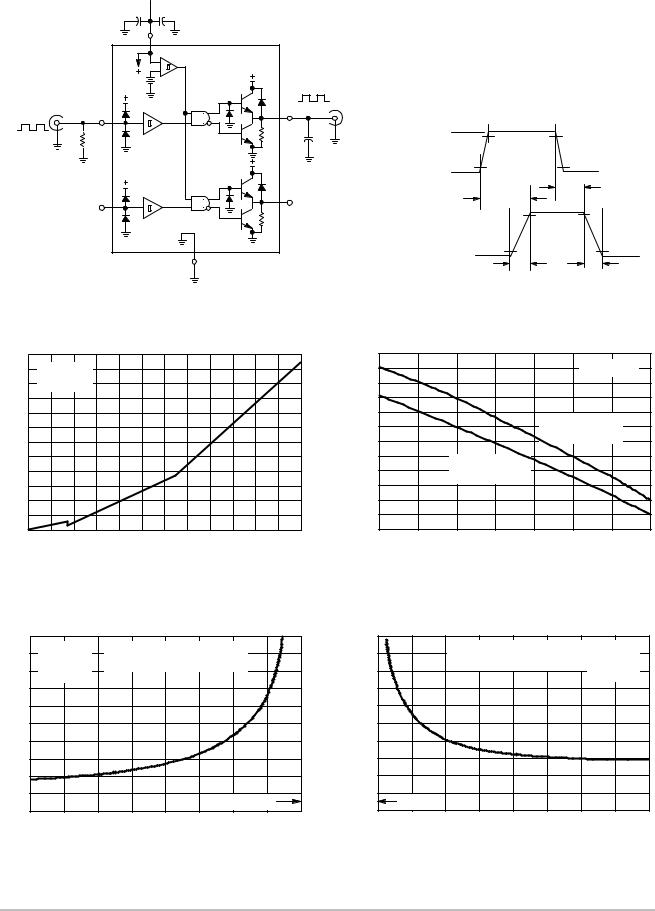

Figure 2. Switching Characteristics Test CIrcuit |

Figure 3. Switching Waveform Definitions |

|

2.4 |

|

|

|

|

|

|

|

|

VCC = 12 V |

|

|

|

|

|

|

2.0 |

TA = 25°C |

|

|

|

|

|

(mA) |

1.6 |

|

|

|

|

|

|

CURRENT |

|

|

|

|

|

|

|

1.2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

, INPUT |

0.8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

in |

0.4 |

|

|

|

|

|

|

I |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

0 |

2.0 |

4.0 |

6.0 |

8.0 |

10 |

12 |

Vin, INPUT VOLTAGE (V)

Figure 4. Logic Input Current versus Input Voltage

(ns) |

|

|

|

|

|

|

|

|

DELAY |

200 |

|

|

|

|

|

||

|

|

VCC = 12 V |

|

Overdrive Voltage is with Respect |

|

|||

PROPAGATION |

|

|

CL = 1.0 nF |

to the Logic Input Lower Threshold |

|

|||

160 |

TA = 25°C |

|

|

|

|

|||

120 |

|

|

|

|

|

|||

|

|

|

|

|

|

|

||

OUTPUT |

|

80 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

, DRIVE |

|

40 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

PLH(In/Out) |

0 |

|

|

|

Vth(lower) |

|

||

-1.6 |

-1.2 |

-0.8 |

-0.4 |

0 |

||||

|

||||||||

Vin, INPUT OVERDRIVE VOLTAGE BELOW LOWER THRESHOLD (V) |

||||||||

|

|

|

|

|

|

|||

t |

|

|

|

|

|

|

|

|

Figure 6. Drive Output High to Low Propagation Delay versus Logic Input Overdrive Voltage

|

2.2 |

|

|

|

|

|

|

|

(V) |

|

|

|

|

|

|

VCC = 12 V |

|

2.0 |

|

|

|

|

|

|

|

|

VOLTAGE |

|

|

|

|

|

|

|

|

1.8 |

|

|

|

|

Upper Threshold |

|

||

|

|

|

|

|

|

|||

THRESHOLD |

1.6 |

|

|

|

|

Low State Output |

|

|

|

|

|

|

|

|

|

||

1.4 |

|

Lower Threshold |

|

|

|

|

||

|

High State Output |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

, INPUT |

1.2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

th |

|

|

|

|

|

|

|

|

V |

1.0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-55 |

-25 |

0 |

25 |

50 |

75 |

100 |

125 |

|

|

|

TA, AMBIENT TEMPERATURE (°C) |

|

|

|||

Figure 5. Logic Input Threshold Voltage

versus Temperature

(ns) |

|

|

|

|

|

|

DELAY |

200 |

|

|

|

|

|

|

|

Overdrive Voltage is with Respect |

|

VCC = 12 V |

||

|

|

to the Logic Input Upper Threshold |

CL = 1.0 nF |

|||

PROPAGATION |

|

|

||||

160 |

|

|

|

° |

||

|

|

|

|

TA = 25 C |

||

120 |

|

|

|

|

||

|

|

|

|

|

||

OUTPUT |

80 |

|

|

|

|

|

|

|

|

|

|

||

, DRIVE |

40 |

|

|

|

|

|

|

|

|

|

|

||

PHL(In/Out) |

0 |

Vth(upper) |

|

|

|

|

1 |

2 |

3 |

4 |

|||

0 |

||||||

Vin, INPUT OVERDRIVE VOLTAGE ABOVE UPPER THRESHOLD (V) |

||||||

|

|

|

|

|

||

t |

|

|

|

|

|

|

Figure 7. Drive Output Low to High Propagation Delay versus Logic Input Overdrive Voltage

http://onsemi.com

4

Loading...

Loading...