Oki Microline 3320, Microline 3321 User Manual

¡

MICROLINE 3320/3321 PRINTER

Maintenance Manual

All specifications are subject to change without notice.

PREFACE

This maintenance manual describes how to maintain the Microline 3320/3321 printer in the field. This manual is for customer engineers.

For further information, refer to the Users Manual for handling or operating the equipment.

iii

TABLE OF CONTENTS

1.CONFIGURATION

1.1Standard Printer Configuration

1.2Options

2.THEORY OF OPERATION

2.1Electrical Operation

2.1.1Summary

2.1.2Microprocessor and the Peripheral Circuit

2.1.3Initialization

2.1.4Parallel Interface Control

2.1.5Print Control

2.1.6SP/LF Motor Control

2.1.7Operation Panel

2.1.8Alarm Circuit

2.1.9Power Supply Circuit

2.2Mechanical Operation

2.2.1Printhead Mechanism and Operation

2.2.2Spacing Operation

2.2.3Head Gap Adjusting

2.2.4Ribbon Drive

2.2.5Paper Feed Operation

2.2.6Paper Detection Mechanism

2.2.7Automatic Sheet Feed

2.2.8Paper Park Function

3.ASSEMBLY/DISASSEMBLY

3.1Precautions for Parts Replacement

3.2Service Tools

3.3Disassembly/Reassembly Procedure

3.3.1Printhead

3.3.2Ribbon Protector

3.3.3Pull-up Roller Assy

3.3.4Upper Cover Assy, Access Cover Assy and Sheet Guide Assy

3.3.5Gear Case Assy

3.3.6PC Connector

3.3.7Space Motor, Guide Roller Assy

3.3.8Space Rack

i

3.3.9Carriage Cable

3.3.10Backup Roller Holder Assy

3.3.11Platen Assy

3.3.12Driver Board (SDDV)

3.3.13LF Motor

3.3.14Operation Panel PCB (LEOP)

3.3.15Control/Power Supply Board (SDCT)

3.3.16Transformer Assy

3.3.17Change Lever and Gears

3.3.18Carriage Shaft

3.3.19Paper Pan

3.3.20Rear Tractor Assy

3.3.21Rear Pressure Assy

3.3.22Switch Lever

4.ADJUSTMENT

5.CLEANING AND LUBRICATION

5.1Cleaning

5.2Lubrication

6.TROUBLESHOOTING AND REPAIR

6.1Items to Check Before Repair

6.2Troubleshooting Table

6.3Lamp Display

6.4Connection Circuit Check for Printhead and SP/LF Motor

6.5Troubleshooting Flow Chart

APPENDIX

A.PCB LAYOUT

B.SPARE PARTS LIST

C.RS-232C Serial Interface Board (OPTION)

ii

1. CONFIGURATION

1.CONFIGURATION

1.1. Standard Printer Configuration

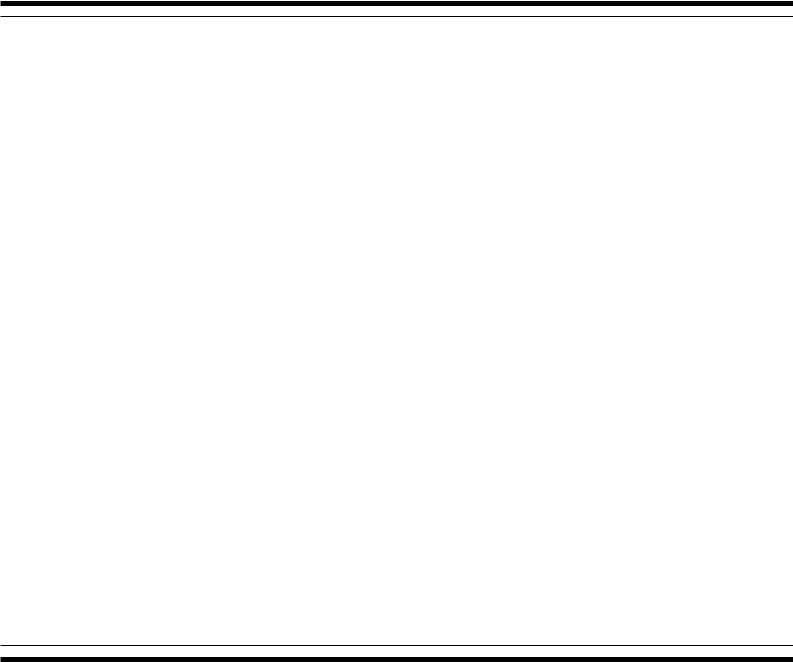

This printer consists of the following assemblies:

Sheet guide assy

Platen knob

Access cover assy

Upper cover

Transformer assy

Pull-up roller assy

Control/Power supply assy

Driver board

Operation panel assy

Main chassis assy

Figure 1-1 Configuration

1 – 1

1.2Options

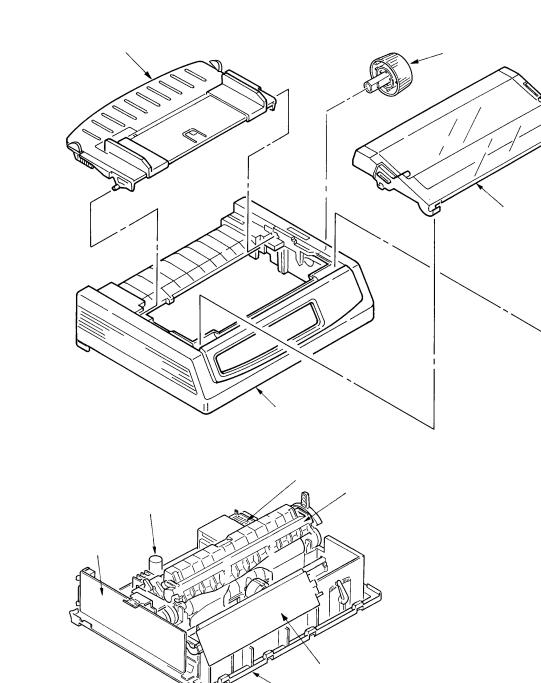

(1)Cut sheet feeder unit (CSF)

(Narrow and wide versions available)

Dual-bin CSF |

Single-bin CSF |

Attachment assy

(2)Pull-tractor assy

1 – 2

(3)Bottom push tractor unit

(4)Roll paper stand (Narrow only)

(5)Serial I/F

•RS232C

•RS422A

•Current Loop

1 – 3

2. THEORY OF OPERATION

2.THEORY OF OPERATION

2.1Electrical Operation

The electrical operation of the printer circuit is described in this section.

2.1.1Summary

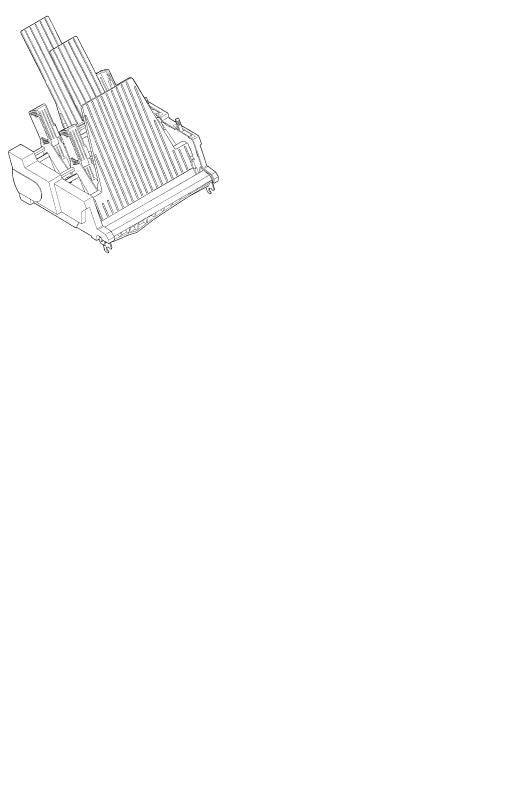

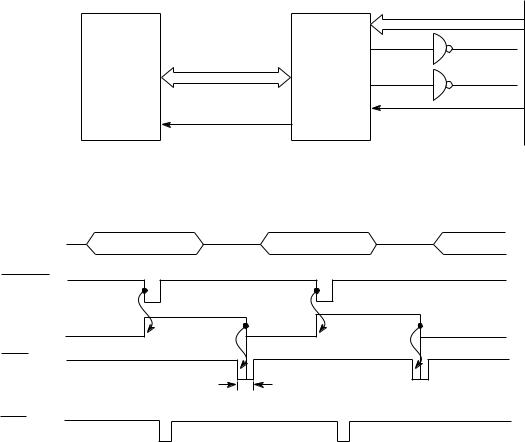

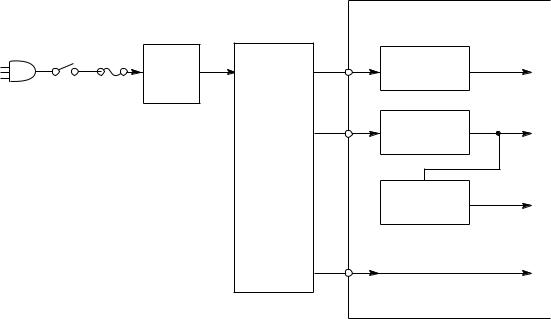

Fig. 2-1 shows the block diagram of the printer.

The control board is made up of the microprocessors, peripheral circuits, drive circuits, sensors and interface connectors.

The power to the control board is supplied by the power board through the connector cord.

The power to other electrical parts is also distributed through the connectors within the control board.

2.1.2Microprocessor and the Peripheral Circuit

(1)Microprocessor (Q7: 67X640)

This processor is a CMOS single-chip computer with integrated peripheral device functions and a 16 bit MPU core, all OKI original architecture.

The processor has a 20 bit address bus and a 16 bit data bus.

It is capable of accessing up to 1M word program memory and 1M bytes of data memory. The following characteristics are also provided:

•Built-in type data memory of 512 bytes

•8-bit 4-channel A/D converter × 1

•16-bit automatic reload timer × 2

•8-bit serial port × 2

•8-bit parallel port × 3 (bitwise I/O specification available)

And others.

The function of this microprocessor is to provide a central mechanism for the entire printer by executing the control program through the LSI and driver circuits.

2 – 1

|

67 x 640 |

AD-BUS |

|

|

|

|

|

|

LSI |

|

ADDRESS |

|

|

|

12.288 |

ROM |

Kbits |

DRAM |

|

MHz |

|

4*64 |

|

|

|

|

|

||

|

1M |

256 |

|

|

|

max |

Kbit*2 |

|

|

|

4M |

* |

|

|

4 |

16 |

|

|

|

|

|

|

|

|

|

AI |

|

|

|

Vcc-Level |

|

EEPROM |

|

|

TSD |

|

|

|

|

|

1 Kbits |

|

|

|

AUTO-LF |

|

|

|

|

|

|

|

|

|

|

|

I/F-IPT |

|

|

|

|

Print-IPT |

|

|

2 |

INT |

Release-SW |

|

|

2 – |

|

|

||

|

Bottom-Sensor |

|

|

|

|

|

PE-SENSOR |

|

|

|

|

|

|

|

|

|

|

OPERATION |

Serial |

|

|

|

|

|

|

|

|

PANEL |

|

|

|

Power-off |

|

|

|

Rectifier |

40 volt |

|

Alarm |

|

circuit |

8 volt |

|

circuit |

|

|

5 volt |

RESET |

|

|

|

Reset |

|

|

|

|

5VD |

|

|

|

|

circuit |

|

|

|

|

Divider |

Vcc-Level |

|

AC-input |

Transformer |

|

|

|

Figure 2-1

|

(opt.) |

|

|

|

CSF |

|

|

|

Roll paper |

|

|

|

Stand |

|

|

Para |

(opt.) |

|

|

RS232C |

|

||

-I/F |

|

||

-I/F |

|

||

|

|

||

TSD |

|

|

|

Head |

|

|

|

driver |

|

|

|

HD-Alarm |

|

|

|

|

2P Encoder |

|

|

SP |

M |

SP |

|

driver |

|

|

|

SP alarm |

|

|

|

LF |

M |

LF |

|

driver |

|||

|

|

||

Fuse |

|

|

HD-Alarm |

40 V |

SP-Alarm |

|

(2)Program ROM

This is a 256 × 16 bits (4M bit) [MAX] EPROM with the control program for the printer stored. The MPU executes instructions under this program.

The program ROM is assigned to the program memory area of the MPU and is fetched by the PSEN signal of the MPU.

The following shows the operation of the memory access.

MPU CLOCK

A0~A17

PG-N

PSEN-N

D0~D15

MPU |

ROM |

|

A0~A17 |

|

D0~D15 |

|

PG-N |

CSO |

CE |

PSEN |

OE |

Program |

Program |

Program |

IN |

IN |

IN |

2 – 3

(3)RAM (MSM51C464A-80RS)

The RAM is CMOS dynamic RAM with (64K × 4-bit) × 2 configuration, and used as buffers (such as receiving buffer, printing buffer, DLL buffer and working buffer).

The following shows the examples of the memory access operation.

MPU |

|

A0~A7 |

RAM 1 (Q3) |

|

|

RAM 2 (Q4) |

|

|

|

|

|

P03 |

|

|

RAS |

CS1 |

|

D0~D3 |

CAS |

|

|

|

|

|

|

|

D4~D7 |

RD |

|

|

OE |

Clockout* |

T1 |

T2 |

T3 |

A0~A7

CS1~CS4

RD

D0~D7

(Read)

WRH

WRL

D0~D7

(Write)

8-bit bus, byte instruction

* Clockout is provided when the original excitation is selected.

2 – 4

(4)EEPROM

The EEPROM is a CMOS serial I/O type memory which is capable of electrically erasing and writing 1,024 bits.

The EEPROM contains menu data.

The following shows the memory access operation.

MPU |

EEPROM |

EEDIN-P

P24  D1

D1

EECS-P

P27  CS

CS

EEDOUT-P

P25  DO

DO

EECLK-P

P26

PRE = O

PE = X

EECS-P

tCS

EECLK-P

|

Start |

Operation |

Address |

|

|

|

|

|

|

|

|

code |

|

|

|

|

|

|

|

||

|

code |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

EEDIN-P |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

A5 |

|

A0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

EEDOUT-P |

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D15 |

D0 |

D15 |

D0 |

D15 |

|

|

|

|

Read cycle timing (READ) |

|

|

||||

PRE = O |

|

|

|

|

|

|

|

|

|

|

PE |

|

|

|

|

|

|

|

|

|

|

EECS-P |

|

|

|

|

|

|

tCS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EECLK-P |

|

|

|

|

|

|

|

|

|

|

|

Start |

Operation |

Address |

|

Data |

|

|

|

|

|

|

code |

|

|

|

|

|

|

|||

|

code |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EEDIN-P |

1 |

0 |

1 |

A5 |

A0 |

D15 |

D0 |

|

|

|

|

|

|

|

|

|

|

|

|||

EEDOUT-P |

|

|

|

|

|

|

|

|

Bus |

Ready |

twp

Write cycle timing (WRITE)

2 – 5

(5)LSI

This LSI detects and controls the SP motor speeds by monitoring the two phase sensor signals obtained from the DC motors and modifying the excitation phases as appropriate.

This LSI is connected in multiplex to the MPU.

MPU |

LSI |

|

A/D bus |

P07 |

ALE |

RD |

RDN |

WRL |

WRL |

P01 |

LSIC |

Clockout*

A0~A19

LSICS

ALE |

|

|

|

D0~D15 |

Address |

Data |

|

(Read) |

|||

|

|

||

RD |

|

|

D0~D15

Address Data

(Write)

WRL

* Clockout is provided when the original excitation is selected.

2 – 6

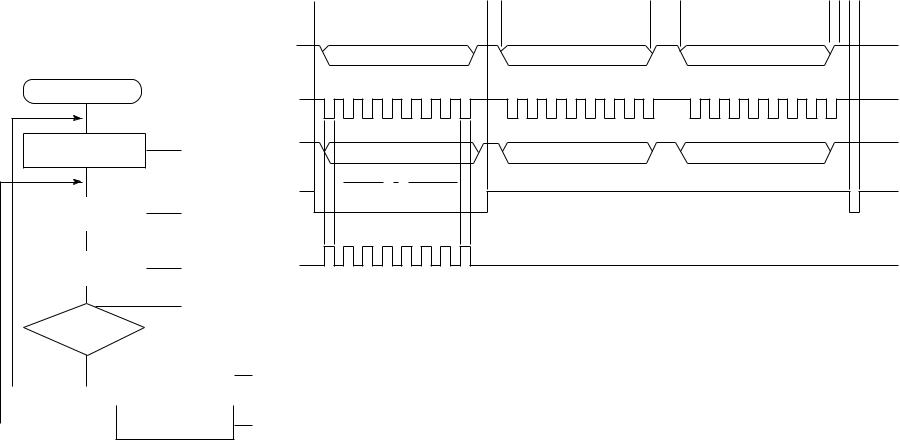

2.1.3Initialization

This printer is initialized when the power is turned on or when the I-PRIME-N signal is input from the host side via the parallel interface.

For the initialize operation, the RST-N signal is first output from the reset circuit to reset the MPUs and LSIs. When resetting ends, the program starts and the LSIs are reset by MPU via LSIRST-N. Reset operation by I-PRIME starts program to initialize, but does not reset the MPU.

The program here sets the mode of the LSI including the MPU, checks the memories (ROMs and RAMs), then carries out carriage homing, and determines the LF motor phase.

Finally, the program establishes the interface signals (P-I/F: ACK-P signal sending, and S-I/F: BUSY-N signal off) and lights the SELECT lamp to inform the ready state for receiving to the host side and ends the initialize operation.

|

|

|

Start |

||||

|

|

|

|

|

|

|

|

|

|

|

MPU |

RESET |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MPU |

|

|

||

|

|

|

Initial Setting |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Internal RAM |

|

|

||

|

|

|

CHECK |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

ROM CHECK |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

LSI RESET |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

External RAM |

|

|

||

|

|

|

CHECK |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

LSI Initial Setting |

|

|

|||

|

|

and I/F Busy ON |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

RAM Clear |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Carriage Homing |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LF Motor Phase |

|

|

||

|

|

|

Initialization |

|

|

||

Serial |

|

|

|

|

|

|

Parallel |

|

|

|

|

|

|

||

|

|

|

|

|

|

||

I/F |

|

|

|

|

|

|

I/F |

I/F BUSY OFF |

|

|

|

|

I/F ACK |

Send |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

End

2 – 7

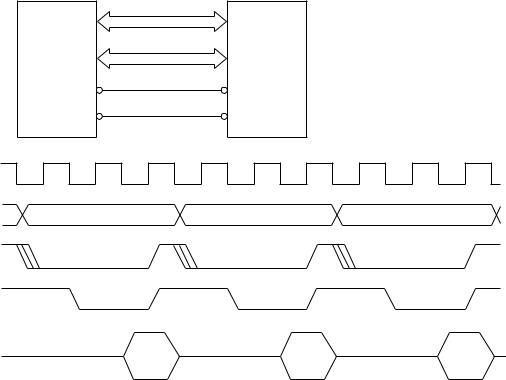

2.1.4Parallel Interface Control

The parallel data input from the host to the interfaced LSI is latched to its internal register at the falling edge of the STROBE-N signal.

At the same time, the LSI sets the BUSY signal to the high level to inform the host that the data is being processed, and outputs the RXD signal to inform the MPU of data reception. The data is read upon receiving the RD-N signal from the MPU.

When the data processing ends, the BUSY signal is set to off and the ACK-N signal in sent to request the next data. When reception is impossible because the buffer is full, the BUSY signal is sent to request stopping of data transmission.

MPU |

LSI |

|

NBSY |

|

A/D bus |

|

ACK |

|

NSTB |

|

RXD |

P16 |

NRXD |

CN1

Receive Data

BUSY

BUSY

ACK-N

ACK-N

STB-N

Data 1 to 8

STROBE

500ns max.

BUSY

ACK

2~8µs

RXD

2 – 8

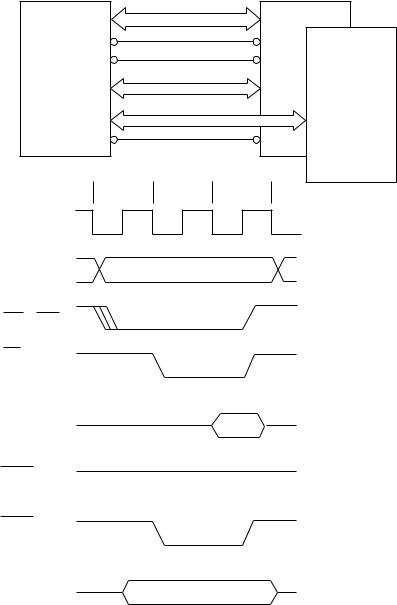

2.1.5Print Control

Print data is transmitted as parallel data (HEAD1~HEAD9) from LSI to print head. LSI generates print timing and drive time.

Control/Power Supply Board |

|

Driver Board |

|

|

|||

|

MPU |

LSI |

|

|

|||

|

|

A/D bus |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Print Data |

DRIVER |

Print Data |

Print Head |

|

|

|

|

|

|

||

|

|

|

|

HEAD1-N~ |

|

HEAD1~ |

|

|

|

|

|

|

|

||

|

|

|

|

HEAD9-N |

|

HEAD9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HEAD DRIVE TIMING CHART

DT1

DT2

HEAD

DRIVE CURRENT

2 – 9

Print Compensation Control

The print compensation can be made as shown below:

(a)Voltage compensation (See 2.1.8 “Alarm Circuit.”)

(b)Temperature compensation (See 2.1.8 “Alarm Circuit.”)

(c)Pin stroke compensation

Platen

Print Head

Pin 1, 2

3~6

8, 9

Pin coil current

Pin 1, 2, 8, 9

As shown in the drawing left, the stroke length up to the platen is different for each pin.

Pin 3~6

Time

Time

(d)Simultaneous Compensation of the number of impact pins

The MPU is provided with the compensation table for each pin to make necessary compensation.

Number of impact pins |

Few |

|

Many |

|

|||

|

|

|

|

Drive time |

Short |

|

Long |

|

|||

|

|

|

|

2 – 10

(e)Print mode compensation

According to the thickness of the printing medium, the print mode is compensated as shown in the table below:

Head Gap Range |

1 |

|

2 |

|

3 |

|

4 |

|

5 |

|

|

|

|

|

|

|

|

|

|

Print speed |

100% |

|

95% |

|

85% |

|

85% |

|

80% |

|

|

|

|

|

|

|

|

|

|

Drive time |

|

Short |

|

|

|

Long |

|

||

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

(Drive time lengthens at each step.)

2 – 11

2.1.6SP/LF Motor Control

(1)Space motor control

The SP motor driver (HA13412) drives the three-phase brushless motor based on the phase signal (SPU, SPV and SPW) and the speed instruction data from the LSI. The MPU can identify the current speed of the space motor by measuring through the LSI the pulse length of the output (øA, øB) of the slit encoder included in the space motor.

By comparing the target speed for each print mode with the actual current speed to change the speed instruction data, the motor speed is accelerated or decelerated to maintain the specified speed for each print mode.

SPU

SPV

SPW

SP truth table

HALL |

|

AMP |

INPUT |

|

OUTPUT |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SPU |

|

SPV |

SPW |

U |

V |

W |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

H |

|

L |

OPEN |

L |

H |

|||

|

H |

|

L |

|

L |

L |

OPEN |

H |

|||

|

H |

|

L |

|

H |

L |

H |

OPEN |

|||

|

L |

|

L |

|

H |

OPEN |

H |

L |

|||

|

L |

|

H |

|

H |

H |

OPEN |

L |

|||

|

L |

|

H |

|

L |

H |

L |

OPEN |

|||

|

|

|

|

|

|

|

|

|

|

|

|

2 – 12

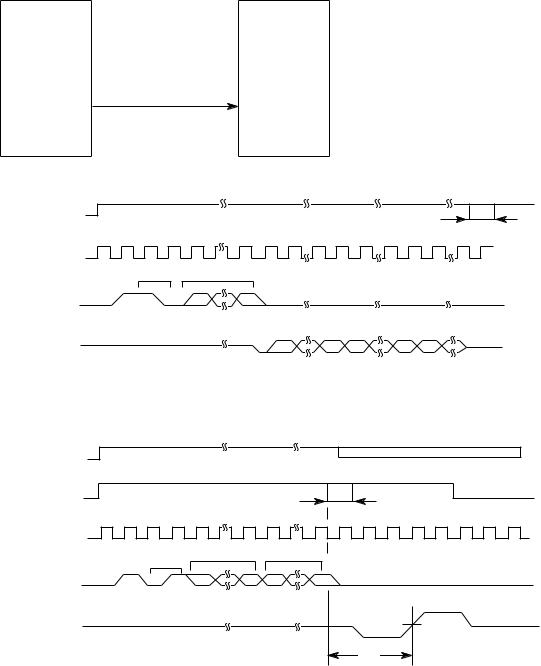

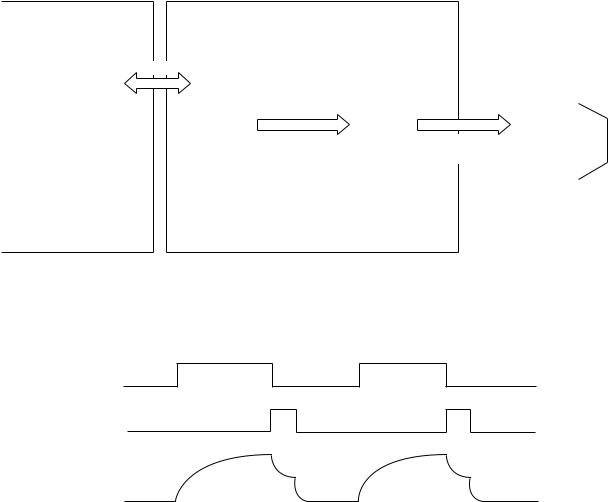

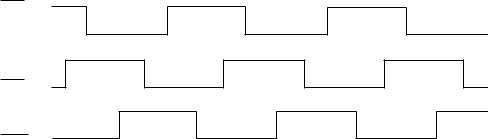

(2)Encoder disk

In the operation of the spacing motor, the PHASE-A and PHASE-B signals are generated when the encoder disk interrupts the photo sensor.

The LSI divides these edge pulse signals in accordance with the print pitch, and sends the IPT signal to provide dot-on timing and carriage position detection timing.

SPU

SPV

SPW

PHASE-A

PHASE-B

1/720"

• UTILITY MODE

IPT 10 CPI

1/120"

IPT 12 CPI

1/144"

IPT 15 CPI

1/180"

IPT 17 CPI

1/206"

IPT 20 CPI

1/240"

2 – 13

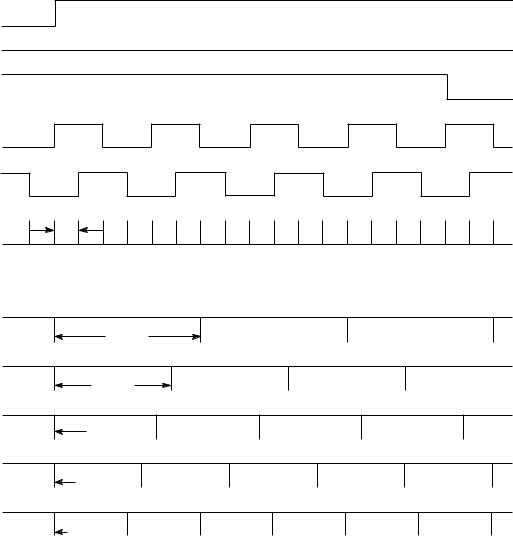

(3)LF motor control

The LF motor driver (MTD2005F) drives the LF motor in two-phase or 1-2 phase bipolar, based on the phase changeover data and the output current data from the LSI.

The data from the LSI is processed by a specific register contained in the LF motor driver to measure the overdrive time and to change the phase.

PHASE-A

PHASE-B

[FORWARD] |

[REVERSE] |

2 – 14

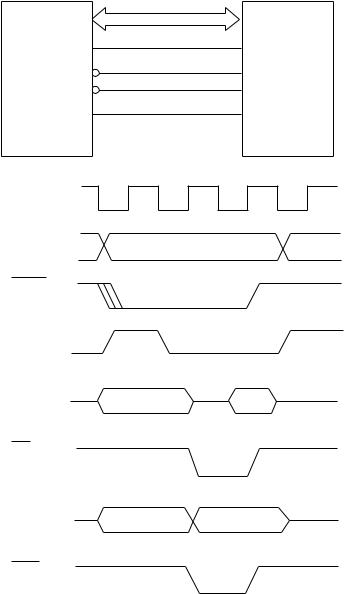

2.1.7Operation Panel

The clock synchronization OPCLK of LSI is used to input the switch data and output the LED data through the operation panel control LSI (IC1: BU5148S).

LSI |

|

|

|

|

OPTD |

OPTXD |

|

|

|

77 |

|

|

||

|

|

|

||

OPCK |

OPCLK |

Command |

|

|

78 |

LED driver |

|||

|

and Data |

|||

|

OPCLR-N |

|

||

NPA2 |

latch |

|

||

80 |

|

|||

|

|

|||

OPRD |

OPRXD |

|

|

|

79 |

|

|

||

|

|

|

||

|

|

|

+5V |

|

|

|

|

Switch |

|

|

|

|

controller |

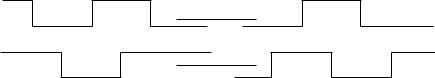

A 2-byte (15 bits + 1 even parity bit) command (OPTXD) is transmitted to the LSI (BU5148S) in synchronization with the OPCLK signal. The LSI decodes this command and when it is found to be legal, returns a 2-byte command response back to the LSI which includes data on Switch information, LED status, receive command ACK/NAK and 1 odd parity bit.

Any transmission errors found cause the command to be reissued after the transmission of the OPCLR-N signal.

2 – 15

16 – 2

Power ON

Write instruction for LSI

1

reset

|

LSI write for LED data, |

|

|

2 |

|||

|

etc. |

|

|||||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Read instruction for |

|

|

3 |

|||

|

data read |

|

|||||

|

|

|

|

|

|||

|

|

|

|

|

|

||

|

|

|

|

4 |

|||

|

Response check |

|

|

NO |

|||

|

|

|

|

|

|||

|

for OK or NG |

|

|

|

|

||

|

|

YES |

|

|

|

|

|

|

|

|

Error |

notification |

|||

|

|

|

|

||||

|

|

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Instruction for |

6 |

retransmission |

1 |

2 |

3 |

2 |

6 |

31 5 or 8 |

||||

bit0 |

bit7 |

|

|

7 |

|

|

|

||

OPTXD |

Command (first) |

|

Command (second) |

|

|

|

|

||

OPCLK |

|

|

|

|

bit0 |

|

bit7 |

|

|

OPRXD |

|

|

Command response (second) |

|

Command response (first) |

|

|

||

|

Note |

|

|

|

OPCLR-N |

|

|

|

|

Reset within BU5148S

7

8

Note: From the illustration above, you can see that the command and the command response are output at the same time. This is because the bit 0 to bit 3 of OPRXD are fixed so that the response can be returned before decoding the command.

2.1.8Alarm Circuit

(1)Head drive time alarm circuit

This circuit monitors the drive time using the HDALM signal interlocked with the overdrive signal of each drive circuit.

If the drive time of any drive circuit exceeds the specified time, the drive fault alarm circuit sends an ALARM-N signal to turn on the SCR (SO).

This cause the secondary coil (40V) of the transformer to be short-circuited, causing an overcurrent to flow through the primary coil and making the AC fuse (transformer assy) open.

(2)Alarm processing when DC power is low.

+ 40V is converted into the POWLEV signal (0V to +5V) by R28 and R29 and input into the A/D port of the MPU to control the drive time and the print speed (pass number) of the head.

+40V

R28

POWLEV

R29

(a)Head drive time

The head drive time is lengthened to compensate for the amount of voltage drop by monitoring the POWLEV signal once every 500 μ sec. to control and maintain the impact necessary for each printing pin at the fixed value.

(b)Print speed

Voltage, +40V |

Pass number |

Print speed |

|

|

|

38V or more |

1 Pass |

100% |

25V to 37V |

1 Pass |

100~30% |

25V or less |

1 Pass |

30% |

|

|

|

2 – 17

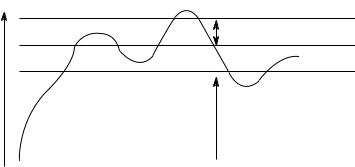

(3)Head overheat alarm

The voltage of the output TSD signal of the thermistors, one of which is contained in the print head and the other in the print head driver, is monitored by the CPU/AD port to control the voltage

Temp |

Stop |

|

119°C |

|

Mode up |

|

α°C |

|

ß°C |

|

Mode down |

Mode and print control

Mode |

Speed |

Pass |

Direction |

|

|

|

|

|

|

1 |

100% |

1 |

Bi |

|

|

|

|

|

|

2 |

85% |

1 |

Bi |

|

|

|

|

|

|

3 |

70% |

1 |

Bi |

|

|

|

|

|

|

4 |

55% |

1 |

Bi |

|

|

|

|

|

|

5 |

40% |

1 |

Bi |

|

|

|

|

|

|

6 |

30% |

1 |

Bi |

1.5 Sec Stop |

|

|

|

|

|

(7) |

Stop |

|

|

|

|

|

|

|

|

|

|

|

|

|

•When the temperature is between α°C and 119°C, the mode switches sequentially to higher level. When the temperature falls below ß°C, the mode switches to lower level.

•When the temperature exceeds 119°C, printing will stop.

•When temperature gradient is steep, higher mode shall be specified directly.

2 – 18

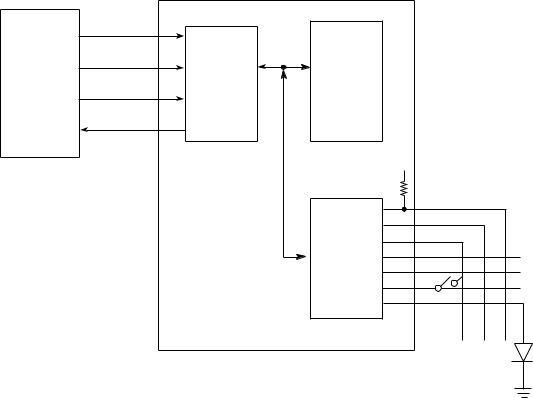

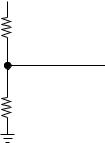

2.1.9Power Supply Circuit

This power supply circuit supplies the +5VDC, +8VDC, +40VDC, 10VAC.

|

|

|

Control Board |

|

SW |

|

Noise |

Rectifier |

|

|

|

+40V |

||

|

|

filter |

||

|

Fuse |

|

|

|

|

circuit |

|

|

|

|

|

|

|

|

|

|

Trans- |

|

|

|

|

former |

Rectifier |

+8V |

|

|

|

Regulation |

+5V |

|

|

|

Circuit |

|

|

|

|

|

|

|

|

|

|

AC10V |

The uses of output voltages and signals are described below.

Voltage/signal |

Use |

|

|

+5V |

Logic IC/LED drive voltage |

|

|

+8V |

Serial interface line voltage and SP motor driver |

|

|

+ 40V |

Printhead, LF motor drive voltage, SP motor drive voltage |

|

|

AC 10V |

Option board |

|

|

2 – 19

2.2Mechanical Operation

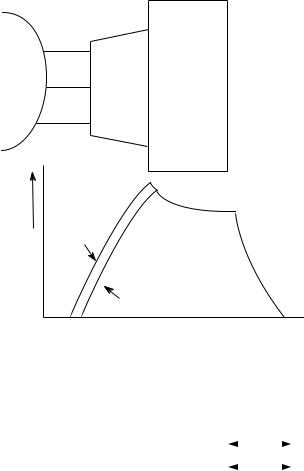

2.2.1Printhead Mechanism and Operation (See Figure 2-2.)

The printhead is a spring charged 9-pin driving head using a permanent magnet. It is attached to the carriage, which moves in parallel with the platen. Electrically, this unit is connected to the control circuits through the control board.

Figure 2-2 Arrangement of the head pins

View from the tip of the printhead

(1)The printhead configuration:

The printhead is composed of the following parts:

(a)Wire guide

(b)Spring assembly (Wire, Armature, Spring, Yoke, Spacer)

(c)Magnet assembly (Magnet, core, coil, Yoke)

(d)Printed circuit board

(e)Fin

2 – 20

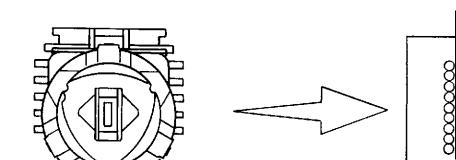

(2)Operation of printhead (See Figure 2-3.)

(a)When the printhead is idle, the armature is attracted by a permanent magnet and the spring fixing the armature is compressed. The print wires fixed to each armature are thus concealed under the wire guide.

(b)When a signal for a character to be printed is detected, a current flows through the coil. When the coil is activated, the magnetic flux (caused by the permanent magnet between the armature and the core) is canceled to eliminate the attraction force. The armature is driven in the direction of the platen by the force of the armature spring. The print wire fixed to the armature protrudes from the tip of the wire guide, strikes the paper through the ribbon and prints a dot on the paper.

(c)After the character has been printed, the armature is magnetically attracted again and the print wires are again concealed under the wire guide.

A thermistor in the printhead prevents burning caused by over-heating of the coil

during extended continuous bi-directional printing. When the temperature of the coil exceeds a pre-determined limit (about 119°C) the control circuit detects a thermistor signal. Printing will then be intermittent or stop completely until the coil temperature falls below the limit value.

2 – 21

Loading...

Loading...