National Semiconductor DS90C363 Technical data

DS90C363

September 1999

DS90C363/DS90CF364

+3.3V Programmable LVDS Transmitter 18-Bit Flat Panel Display (FPD) LinkÐ 65 MHz, +3.3V LVDS Receiver 18-Bit Flat Panel Display (FPD) LinkÐ 65 MHz

General Description

The DS90C363 transmitter converts 21 bits of CMOS/TTL data into three LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fourth LVDS link. Every cycle of the transmit clock 21 bits of input data are sampled and transmitted. The DS90CF364 receiver converts the LVDS data streams back into 21 bits of CMOS/TTL data. At a transmit clock frequency of 65 MHz, 18 bits of RGB data and 3 bits of LCD timing and control data (FPLINE, FPFRAME, DRDY) are transmitted at a rate of 455 Mbps per LVDS data channel. Using a 65 MHz clock, the data throughputs is 170 Mbytes/sec. The Transmitter is offered with programmable edge data strobes for convenient interface with a variety of graphics controllers. The Transmitter can be programmed for Rising edge strobe or Falling edge strobe through a dedicated pin. A Rising edge Transmitter will interoperate with a Falling edge Receiver (DS90CF364) without any translation logic.

This chipset is an ideal means to solve EMI and cable size problems associated with wide, high speed TTL interfaces.

Features

n20 to 65 MHz shift clock support

nProgrammable Transmitter (DS90C363) strobe select (Rising or Falling edge strobe)

nSingle 3.3V supply

nChipset (Tx + Rx) power consumption < 250 mW (typ)

nPower-down mode (< 0.5 mW total)

nSingle pixel per clock XGA (1024x768) ready

nSupports VGA, SVGA, XGA and higher addressability.

nUp to 170 Megabyte/sec bandwidth

nUp to 1.3 Gbps throughput

nNarrow bus reduces cable size and cost

n290 mV swing LVDS devices for low EMI

nPLL requires no external components

nLow profile 48-lead TSSOP package

nFalling edge data strobe Receiver

nCompatible with TIA/EIA-644 LVDS standard

nESD rating > 7 kV

nOperating Temperature: −40ÊC to +85ÊC

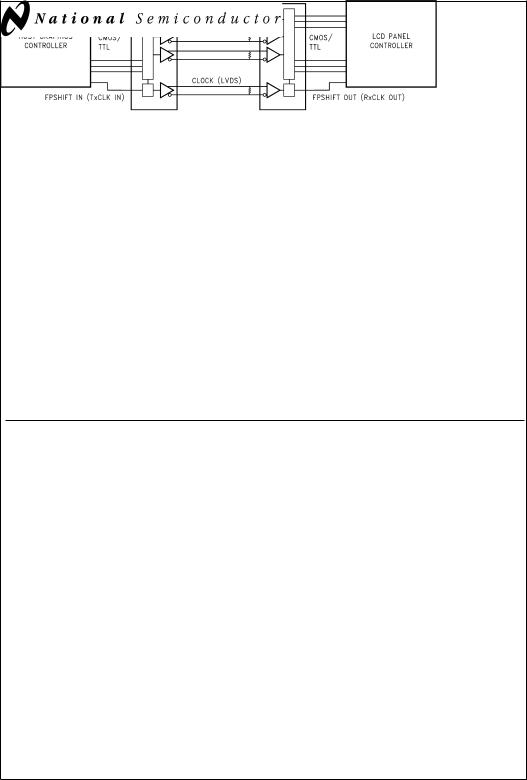

Block Diagrams

Application

DS012886-14

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

(FPD) Display Panel Flat Color-Bit-18 LVDS Programmable 3V.+3 DS90C363/DS90CF364

MHz 65 Ð Link

© 1999 National Semiconductor Corporation |

DS012886 |

www.national.com |

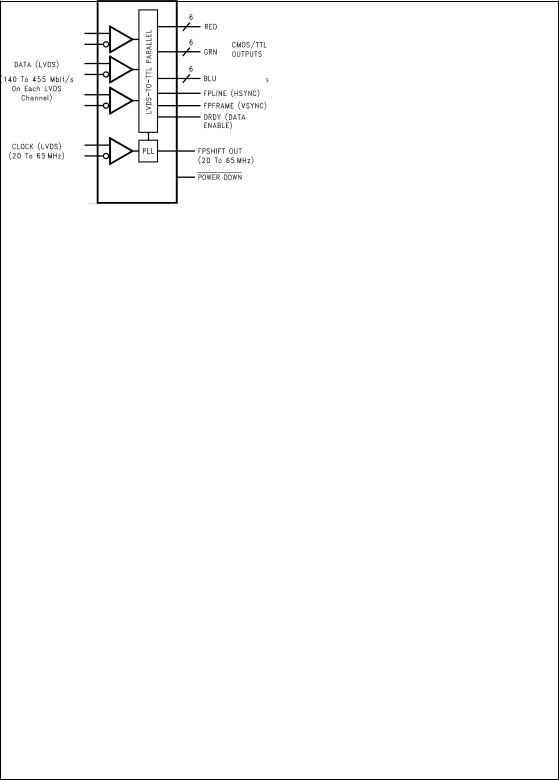

Block Diagrams (Continued)

DS90C363

DS012886-1

Order Number DS90C363MTD

See NS Package Number MTD48

DS90CF364

DS012886-24

Order Number DS90CF364MTD

See NS Package Number MTD48

www.national.com |

2 |

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage (VCC) |

−0.3V to +4V |

CMOS/TTL Input Voltage |

−0.3V to (V CC + 0.3V) |

CMOS/TTL Output Voltage |

−0.3V to (V CC + 0.3V) |

LVDS Receiver Input Voltage |

−0.3V to (V CC + 0.3V) |

LVDS Driver Output Voltage |

−0.3V to (V CC + 0.3V) |

LVDS Output Short Circuit |

|

Duration |

Continuous |

Junction Temperature |

+150ÊC |

Storage Temperature |

−65ÊC to +150ÊC |

Lead Temperature |

|

(Soldering, 4 sec) |

+260ÊC |

Maximum Package Power Dissipation Capacity 25ÊC

MTD48 (TSSOP) Package:

DS90C363 |

1.98 W |

DS90CF364 |

1.89 W |

Package Derating: |

|

DS90C363 |

16 mW/ÊC above +25ÊC |

DS90CF364 |

15 mW/ÊC above +25ÊC |

ESD Rating |

> 7 kV |

(HBM, 1.5 kΩ, 100 pF) |

Recommended Operating

Conditions

|

Min |

Nom |

Max |

Units |

Supply Voltage (VCC) |

3.0 |

3.3 |

3.6 |

V |

Operating Free Air |

|

|

|

|

Temperature (TA) |

−40 |

+25 |

+85 |

ÊC |

Receiver Input Range |

0 |

|

2.4 |

V |

Supply Noise Voltage (VCC) |

|

|

100 |

mVPP |

Electrical Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified.

Symbol |

Parameter |

|

|

Conditions |

|

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

|

|

|

|

|

CMOS/TTL DC SPECIFICATIONS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VIH |

High Level Input Voltage |

|

|

|

|

|

2.0 |

|

VCC |

V |

VIL |

Low Level Input Voltage |

|

|

|

|

|

GND |

|

0.8 |

V |

VOH |

High Level Output Voltage |

|

IOH = −0.4 mA |

|

2.7 |

3.3 |

|

V |

||

VOL |

Low Level Output Voltage |

|

IOL = 2 mA |

|

|

0.06 |

0.3 |

V |

||

VCL |

Input Clamp Voltage |

|

ICL = −18 mA |

|

|

−0.79 |

−1.5 |

V |

||

IIN |

Input Current |

|

VIN = VCC, GND, 2.5V or 0.4V |

|

±5.1 |

±10 |

µA |

|||

IOS |

Output Short Circuit Current |

|

VOUT = 0V |

|

|

−60 |

−120 |

mA |

||

LVDS DC SPECIFICATIONS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VOD |

Differential Output Voltage |

RL = 100Ω |

|

250 |

345 |

450 |

mV |

|||

VOD |

Change in VOD between |

|

|

|

|

|

|

|

35 |

mV |

|

complimentary output states |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VOS |

Offset Voltage (Note 4) |

|

|

|

|

|

1.125 |

1.25 |

1.375 |

V |

VOS |

Change in V OS between |

|

|

|

|

|

|

|

35 |

mV |

|

complimentary output states |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IOS |

Output Short Circuit Current |

|

VOUT = 0V, RL = 100Ω |

|

|

−3.5 |

−5 |

mA |

||

IOZ |

Output TRI-STATE® Current |

|

|

|

|

±1 |

±10 |

µA |

||

|

PWR DWN |

= 0V, |

|

|

||||||

|

|

VOUT = 0V or VCC |

|

|

|

|

|

|||

VTH |

Differential Input High Threshold |

VCM = +1.2V |

|

|

|

+100 |

mV |

|||

VTL |

Differential Input Low Threshold |

|

|

|

|

|

−100 |

|

|

mV |

IIN |

Input Current |

|

VIN = +2.4V, VCC = 3.6V |

|

|

|

±10 |

µA |

||

|

|

VIN = 0V, VCC = 3.6V |

|

|

|

±10 |

µA |

|||

TRANSMITTER SUPPLY CURRENT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ICCTW |

Transmitter Supply Current, Worst |

RL = 100Ω, |

|

f = 32.5 MHz |

|

31 |

45 |

mA |

||

|

Case |

CL = 5 pF, Worst |

|

|

|

|

|

|

||

|

|

Case Pattern (Figures |

|

|

|

|

|

|

||

|

|

|

f = 37.5 MHz |

|

32 |

50 |

mA |

|||

|

|

1, 3 ), TA = −40ÊC to |

|

|

||||||

|

|

|

|

|

|

|

|

|||

|

|

|

f = 65 MHz |

|

42 |

55 |

mA |

|||

|

|

+85ÊC |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

ICCTG |

Transmitter Supply Current, 16 |

RL = 100Ω, |

|

f = 32.5 MHz |

|

23 |

35 |

mA |

||

|

Grayscale |

CL = 5 pF, 16 |

|

|

|

|

|

|

||

|

|

Grayscale Pattern |

|

|

|

|

|

|

||

|

|

|

f = 37.5 MHz |

|

28 |

40 |

mA |

|||

|

|

(Figures 2, 3 ), TA = |

|

|

||||||

|

|

|

|

|

|

|

|

|||

|

|

|

f = 65 MHz |

|

31 |

45 |

mA |

|||

|

|

−40ÊC to +85ÊC |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

3 |

www.national.com |

Electrical Characteristics (Continued)

Over recommended operating supply and temperature ranges unless otherwise specified.

Symbol |

Parameter |

|

|

Conditions |

|

|

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

|

|

|

|

|

|

TRANSMITTER SUPPLY CURRENT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ICCTZ |

Transmitter Supply Current |

|

PWR DWN |

= Low |

|

|

|

10 |

55 |

µA |

|

|

Power Down |

Driver Outputs in TRI-STATE® under |

|

|

|

|

|||||

|

|

Power Down Mode |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

RECEIVER SUPPLY CURRENT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ICCRW |

Receiver Supply Current, Worst |

CL = 8 pF, Worst |

|

f = 32.5 MHz |

|

49 |

65 |

mA |

|||

|

Case |

Case Pattern (Figures |

|

|

|

|

|

|

|

||

|

|

1, 4 ), TA = −40ÊC to |

|

|

|

|

|

|

|

||

|

|

|

f = 37.5 |

MHz |

|

53 |

70 |

mA |

|||

|

|

+85ÊC |

|

|

|

|

|

|

|

||

|

|

|

f = 65 MHz |

|

78 |

105 |

mA |

||||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

ICCRG |

Receiver Supply Current, 16 |

CL = 8 pF, 16 |

|

f = 32.5 |

MHz |

|

28 |

45 |

mA |

||

|

Grayscale |

Grayscale Pattern |

|

|

|

|

|

|

|

||

|

|

|

(Figures 2, 4 ), TA = |

|

|

|

|

|

|

|

|

|

|

|

f = 37.5 |

MHz |

|

30 |

47 |

mA |

|||

|

|

−40ÊC to +85ÊC |

|

|

|

|

|

|

|

||

|

|

|

f = 65 MHz |

|

43 |

60 |

mA |

||||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

ICCRZ |

Receiver Supply Current |

|

|

|

|

10 |

55 |

µA |

|||

|

PWR DWN |

= Low |

|

|

|

||||||

|

Power Down |

Receiver Outputs Stay Low during |

|

|

|

|

|

||||

|

|

Power Down Mode |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

Note 1: ªAbsolute Maximum Ratingsº are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of ªElectrical Characteristicsº specify conditions for device operation.

Note 2: Typical values are given for VCC = 3.3V and T A = +25C.

Note 3: Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground unless otherwise specified (except VOD and V OD).

Note 4: VOS previously referred as VCM.

www.national.com |

4 |

Transmitter Switching Characteristics

Over recommended operating supply and −40ÊC to +85ÊC ranges unless otherwise specified

Symbol |

Parameter |

|

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

LLHT |

LVDS Low-to-High Transition Time (Figure 3 ) |

|

|

0.75 |

1.5 |

ns |

|

|

|

|

|

|

|

LHLT |

LVDS High-to-Low Transition Time (Figure 3 ) |

|

|

0.75 |

1.5 |

ns |

|

|

|

|

|

|

|

TCIT |

TxCLK IN Transition Time (Figure 5 ) |

|

|

|

5 |

ns |

|

|

|

|

|

|

|

TCCS |

TxOUT Channel-to-Channel Skew (Figure 6 ) |

|

|

250 |

|

ps |

|

|

|

|

|

|

|

TPPos0 |

Transmitter Output Pulse Position for Bit 0 |

f = 65 MHz |

−0.4 |

0 |

0.3 |

ns |

|

(Figure 17 ) |

|

|

|

|

|

|

|

|

|

|

|

|

TPPos1 |

Transmitter Output Pulse Position for Bit 1 |

|

1.8 |

2.2 |

2.5 |

ns |

|

|

|

|

|

|

|

TPPos2 |

Transmitter Output Pulse Position for Bit 2 |

|

4.0 |

4.4 |

4.7 |

ns |

|

|

|

|

|

|

|

TPPos3 |

Transmitter Output Pulse Position for Bit 3 |

|

6.2 |

6.6 |

6.9 |

ns |

|

|

|

|

|

|

|

TPPos4 |

Transmitter Output Pulse Position for Bit 4 |

|

8.4 |

8.8 |

9.1 |

ns |

|

|

|

|

|

|

|

TPPos5 |

Transmitter Output Pulse Position for Bit 5 |

|

10.6 |

11.0 |

11.3 |

ns |

|

|

|

|

|

|

|

TPPos6 |

Transmitter Output Pulse Position for Bit 6 |

|

12.8 |

13.2 |

13.5 |

ns |

|

|

|

|

|

|

|

TCIP |

TxCLK IN Period (Figure 7) |

|

15 |

T |

50 |

ns |

|

|

|

|

|

|

|

TCIH |

TxCLK IN High Time (Figure 7) |

|

0.35T |

0.5T |

0.65T |

ns |

|

|

|

|

|

|

|

TCIL |

TxCLK IN Low Time (Figure 7) |

|

0.35T |

0.5T |

0.65T |

ns |

|

|

|

|

|

|

|

TSTC |

TxIN Setup to TxCLK IN (Figure 7 ) |

f = 65 MHz |

2.5 |

|

|

ns |

|

|

|

|

|

|

|

THTC |

TxIN Hold to TxCLK IN (Figure 7 ) |

|

0 |

|

|

ns |

|

|

|

|

|

|

|

TCCD |

TxCLK IN to TxCLK OUT Delay 25ÊC, VCC = 3.3V (Figure 9 ) |

3.0 |

3.7 |

5.5 |

ns |

|

TPLLS |

Transmitter Phase Lock Loop Set (Figure 11 ) |

|

|

|

10 |

ms |

|

|

|

|

|

|

|

TPDD |

Transmitter Power Down Delay (Figure 15 ) |

|

|

|

100 |

ns |

|

|

|

|

|

|

|

5 |

www.national.com |

Loading...

Loading...