MXIC MX23C1611PC-10, MX23C1611PC-12, MX23C1611MC-12, MX23C1611MC-10, MX23C1611TC-12 Datasheet

...

MX23C1611

FEATURES

•Bit organization

-2M x 8 (byte mode)

-1M x 16 (word mode)

•Fast access time

-Random access: 100ns (max.)

-Page access: 50ns (max.)

•Page Size

-8 double words per page

•Current

-Operating: 60mA

-Standby: 100uA

•Supply voltage

-5V±10%

•Package

-44 pin SOP (500mil)

-42 pin PDIP (600mm)

-48 pin TSOP (20mm x 12mm)

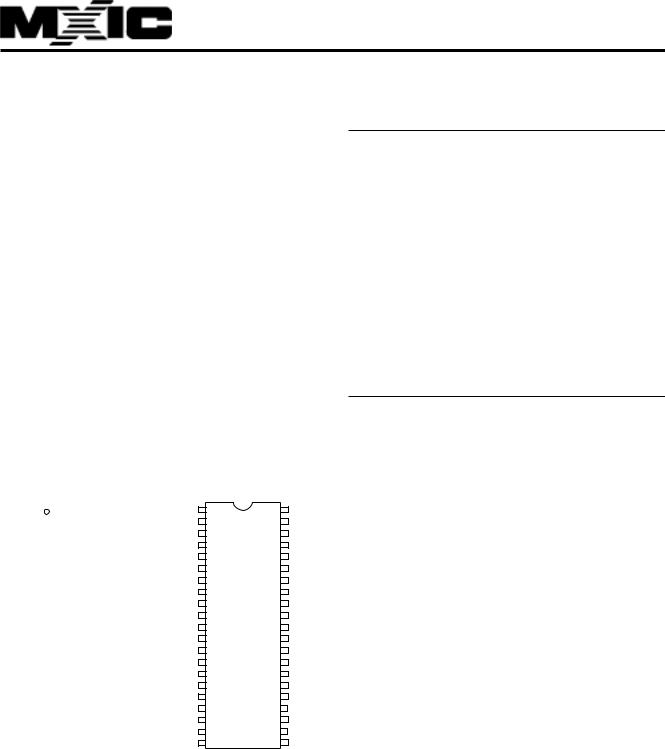

PIN CONFIGURATION

44 SOP |

|

|

|

|

|

|

|

42 PDIP |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

NC |

A18 |

1 |

||||

NC |

|

|

|

|

44 |

|

|

||||||||||

|

|

|

|

|

|||||||||||||

A18 |

|

|

2 |

|

43 |

|

|

A19 |

A17 |

2 |

|||||||

|

|

|

|

||||||||||||||

A17 |

|

|

3 |

|

42 |

|

|

A8 |

|

A7 |

3 |

||||||

|

|

|

|

||||||||||||||

A7 |

|

|

4 |

|

41 |

|

|

A9 |

|

A6 |

4 |

||||||

|

|

|

|

||||||||||||||

A6 |

|

|

5 |

|

40 |

|

|

A10 |

|

A5 |

5 |

||||||

|

|

|

|

|

|||||||||||||

A5 |

|

|

6 |

|

39 |

|

|

A11 |

|

A4 |

6 |

||||||

|

|

|

|

|

|||||||||||||

A4 |

|

|

7 |

|

38 |

|

|

A12 |

|

A3 |

7 |

||||||

A3 |

|

|

8 |

|

37 |

|

|

A13 |

|

||||||||

|

|

MX23C1611 |

|

|

|

A2 |

8 |

||||||||||

A2 |

|

|

9 |

36 |

|

|

A14 |

|

|||||||||

|

|

|

|

|

|

A1 |

9 |

||||||||||

A1 |

|

|

10 |

|

35 |

|

|

A15 |

|

||||||||

|

|

|

|

|

|

A0 |

10 |

||||||||||

A0 |

|

|

11 |

|

34 |

|

|

A16 |

|

||||||||

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

CE |

11 |

|||||||||||

|

|

|

|

|

|

|

|

33 |

|

|

|

|

|

||||

|

|

|

|

|

|

12 |

|

|

|

BYTE |

|||||||

CE |

|

|

|

|

|

||||||||||||

|

|

|

|

|

VSS |

12 |

|||||||||||

VSS |

|

|

13 |

|

32 |

|

|

VSS |

|||||||||

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

OE |

13 |

|||||||||||

|

OE |

|

|

|

14 |

|

31 |

|

|

D15/A-1 |

|||||||

|

|

|

|

|

D0 |

||||||||||||

D0 |

|

|

15 |

|

30 |

|

|

D7 |

|

14 |

|||||||

|

|

|

|

||||||||||||||

D8 |

|

|

16 |

|

29 |

|

|

D14 |

|

D8 |

15 |

||||||

|

|

|

|

||||||||||||||

D1 |

|

|

17 |

|

28 |

|

|

D6 |

|

D1 |

16 |

||||||

|

|

|

|

|

|||||||||||||

|

|

|

|

|

18 |

|

27 |

|

|

D13 |

|

D9 |

17 |

||||

D9 |

|

|

|

|

|

||||||||||||

|

|

|

|

|

|||||||||||||

|

|

|

|

|

19 |

|

26 |

|

|

D5 |

|

D2 |

18 |

||||

D2 |

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|||||||||||||

D10 |

|

|

20 |

|

25 |

|

|

D12 |

D10 |

19 |

|||||||

|

|

|

|

|

|||||||||||||

D3 |

|

|

21 |

|

24 |

|

|

D4 |

|

D3 |

20 |

||||||

|

|

|

|

|

|||||||||||||

D11 |

|

|

22 |

|

23 |

|

|

VCC |

D11 |

21 |

|||||||

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||

5 Volt 16-Mbit (2M x 8 / 1M x 16) Mask ROM with Page Mode

ORDER INFORMATION

Part No. |

Access Page Access Package |

||

|

Time |

Time |

|

|

|

|

|

MX23C1611MC-10 |

100ns |

50ns |

44 pin SOP |

|

|

|

|

MX23C1611MC-12 |

120ns |

60ns |

44 pin SOP |

|

|

|

|

MX23C1611PC-10 |

100ns |

50ns |

42 pin PDIP |

|

|

|

|

MX23C1611PC-12 |

120ns |

60ns |

42 pin PDIP |

|

|

|

|

MX23C1611TC-10 |

100ns |

50ns |

48 pin TSOP |

|

|

|

|

MX23C1611TC-12 |

120ns |

60ns |

48 pin TSOP |

|

|

|

|

PIN DESCRIPTION

|

|

|

|

|

Symbol |

Pin Function |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A0~A19 |

Address Inputs |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0~D14 |

Data Outputs |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D15/A-1 |

D15 (Word Mode)/ LSB Address |

|||

|

|

A19 |

|

|

|

|

|

(Byte Mode) |

|

|

42 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|||

|

|

CE |

Chip Enable Input |

||||||

|

41 |

A8 |

|

||||||

|

40 |

A9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

OE |

Output Enable Input |

||||||

|

39 |

A10 |

|

||||||

|

38 |

A11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

Byte |

Word/ Byte Mode Selection |

||||||

|

37 |

A12 |

|

||||||

|

36 |

A13 |

|

|

|

|

|

|

|

|

|

VCC |

Power Supply Pin |

||||||

|

35 |

A14 |

|

||||||

MX23C1611 |

34 |

A15 |

|

|

|

|

|

|

|

|

VSS |

Ground Pin |

|||||||

33 |

A16 |

|

|||||||

|

32 |

BYTE |

|

|

|

|

|

|

|

|

|

NC |

No Connection |

||||||

|

31 |

VSS |

|

||||||

|

30 |

D15/A-1 |

|

|

|

|

|

|

|

|

29 |

D7 |

|

|

|

|

|

|

|

|

28 |

D14 |

|

|

|

|

|

|

|

|

27 |

D6 |

|

|

|

|

|

|

|

|

26 |

D13 |

|

|

|

|

|

|

|

|

25 |

D5 |

|

|

|

|

|

|

|

|

24 |

D12 |

|

|

|

|

|

|

|

|

23 |

D4 |

|

|

|

|

|

|

|

|

22 |

VCC |

|

|

|

|

|

|

|

MODE SELECTION

CE |

OE |

Byte |

D31/A-1 |

D0~D15 |

D16~D31 |

Mode |

Power |

|

|

|

|

|

|

|

|

H |

X |

X |

X |

High Z |

High Z |

- |

Stand-by |

|

|

|

|

|

|

|

|

L |

H |

X |

X |

High Z |

High Z |

- |

Active |

|

|

|

|

|

|

|

|

L |

L |

H |

Output |

D0~D7 |

D8~D15 |

Word |

Active |

|

|

|

|

|

|

|

|

L |

L |

L |

Input |

D0~D7 |

High Z |

Byte |

Active |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P/N:PM0241 |

|

|

|

|

|

|

REV. 2.1, JUL. 18, 2001 |

|

|

|

|

1 |

|

|

|

MX23C1611

48 TSOP (Normal Type)

BYTE |

|

|

1 |

|

A16 |

|

|

2 |

|

A15 |

|

|

3 |

|

A14 |

|

|

4 |

|

A13 |

|

|

5 |

|

A12 |

|

|

6 |

|

A11 |

|

|

7 |

|

A10 |

|

|

8 |

|

A9 |

|

9 |

|

|

A8 |

|

10 |

|

|

A19 |

|

11 |

MX23C1611 |

|

VSS |

|

12 |

||

NC |

|

13 |

(Normal Type) |

|

|

|

|||

A18 |

|

14 |

||

|

|

|||

A17 |

|

15 |

|

|

|

|

|

||

A7 |

|

16 |

|

|

|

|

|

||

A6 |

|

|

17 |

|

|

|

|

||

A5 |

|

|

18 |

|

|

|

|

||

A4 |

|

|

19 |

|

|

|

|

||

A3 |

|

|

20 |

|

|

|

|

||

A2 |

|

|

21 |

|

|

|

|

||

A1 |

|

|

22 |

|

|

|

|

||

A0 |

|

|

23 |

|

|

|

|

||

CE |

|

|

24 |

|

|

|

|

||

|

|

|

|

|

48  VSS

VSS

47  VSS

VSS

46  D15/A-1

D15/A-1

45  D7

D7

44  D14

D14

43  D6

D6

42  D13

D13

41  D5

D5

40  D12

D12

39  D4

D4

38  VCC

VCC

37  VCC

VCC

36  NC

NC

35  D11

D11

34  D3

D3

33  D10

D10

32  D2

D2

31  D9

D9

30  D1

D1

29  D8

D8

28  D0

D0

27  OE

OE

26  VSS

VSS

25  VSS

VSS

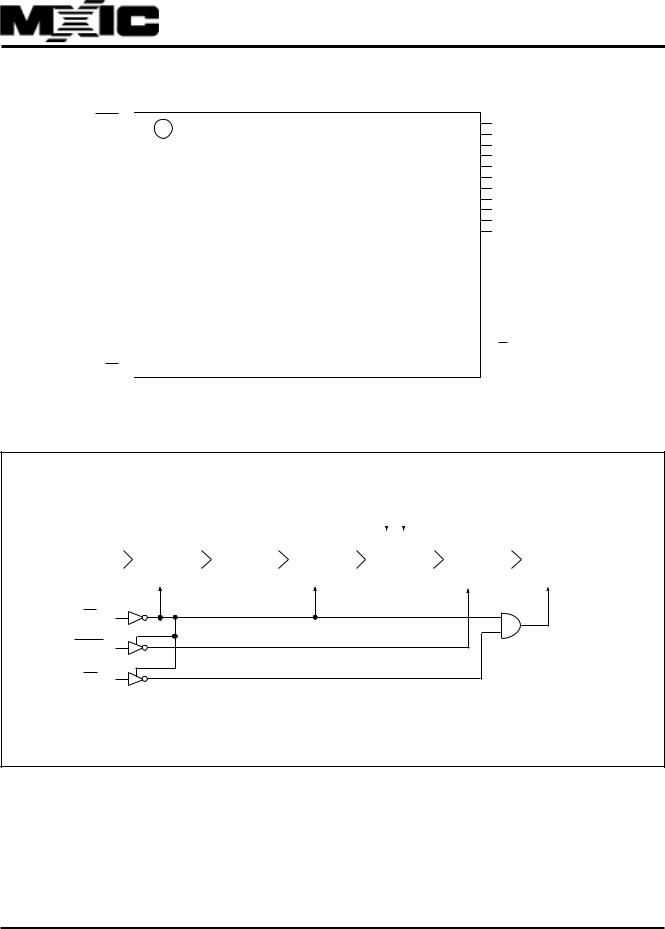

BLOCK DIAGRAM

A0/(A-1) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

A2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

A3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0 |

|||

|

|

Address |

|

|

|

|

Memory |

|

|

|

|

Page |

|

|

|

|

Page |

|

|

|

|

Word/ |

|

|

|

|

Output |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

Buffer |

|

|

|

|

Array |

|

|

|

|

Buffer |

|

|

|

|

Decoder |

|

|

|

|

Byte |

|

|

|

|

Buffer |

|

|

||

A19 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D15/(D7) |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

CE

BYTE

OE

Note: Chip Enable active low input activates the chip's control logic, Address buffer and Page buffer.

P/N:PM0241 |

REV. 2.1, JUL. 18, 2001 |

2

|

|

MX23C1611 |

|

ABSOLUTE MAXIMUM RATINGS |

|

|

|

|

|

|

|

Item |

Symbol |

Ratings |

|

|

|

|

|

Voltage on any Pin Relative to VSS |

VIN |

-1.3V to VCC+2.0V (Note) |

|

|

|

|

|

Ambient Operating Temperature |

Topr |

-40°C to 85°C |

|

|

|

|

|

Storage Temperature |

Tstg |

-65°C to 125°C |

|

|

|

|

|

Note: Minimum DC voltage on input or I/O pins is -0.5V. During voltage transitions, inputs may undershoot VSS to -1.3V for periods of up to 20ns. Maximum DC voltage on input or I/O pins is VCC+0.5V. During voltage transitions, input may overshoot VCC to VCC+2.0V for periods of up to 20ns.

DC CHARACTERISTICS (Ta = 0°C ~ 70°C, VCC = 5V±10%)

Item |

Symbol |

MIN. |

MAX. |

|

Conditions |

||

Output High Voltage |

VOH |

2.4V |

- |

IOH = -1.0mA |

|||

|

|

|

|

|

|

|

|

Output Low Voltage |

VOL |

- |

0.4V |

|

IOL = 2.1mA |

||

|

|

|

|

|

|

|

|

Input High Voltage |

VIH |

2.2V |

VCC+0.3V |

|

|

|

|

|

|

|

|

|

|

|

|

Input Low Voltage |

VIL |

-0.3V |

0.2 x VCC |

|

|

|

|

|

|

|

|

|

|

|

|

Input Leakage Current |

ILI |

- |

5uA |

0V, VCC |

|||

|

|

|

|

|

|

|

|

Output Leakage Current |

ILO |

- |

5uA |

0V, VCC |

|||

|

|

|

|

|

|

|

|

Operating Current |

ICC1 |

- |

60mA |

|

tRC = 100ns, all output open |

||

|

|

|

|

|

|

|

|

Standby Current (TTL) |

ISTB1 |

- |

1mA |

|

= VIH |

||

CE |

|||||||

|

|

|

|

|

|

|

|

Standby Current (cmos) |

ISTB2 |

- |

100uA |

|

|

|

|

CE>VCC-0.2V |

|||||||

|

|

|

|

|

|

|

|

Input Capacitance |

CIN |

- |

10pF |

Ta = 25°C, f = 1MHZ |

|||

|

|

|

|

|

|

|

|

Output Capacitance |

COUT |

- |

10pF |

|

Ta = 25°C, f = 1MHZ |

||

|

|

|

|

|

|

|

|

AC CHARACTERISTICS (Ta = 0°C ~ 70°C, VCC = 5V±10%)

Item |

Symbol |

23C1611-10 |

|

|

23C1611-12 |

|

||

|

|

MIN. |

MAX. |

MIN. |

MAX. |

|||

|

|

|

|

|

|

|

|

|

Read Cycle Time |

tRC |

100ns |

- |

|

|

120ns |

- |

|

|

|

|

|

|

|

|

|

|

Address Access Time |

tAA |

- |

100ns |

- |

120ns |

|||

|

|

|

|

|

|

|

|

|

Chip Enable Access Time |

tACE |

- |

100ns |

- |

120ns |

|||

|

|

|

|

|

|

|

|

|

Page Mode Access Time |

tPA |

- |

50ns |

- |

60ns |

|||

|

|

|

|

|

|

|

|

|

Output Enable Time |

tOE |

- |

50ns |

- |

60ns |

|||

|

|

|

|

|

|

|

|

|

Output Hold After Address |

tOH |

10ns |

- |

|

10ns |

- |

|

|

|

|

|

|

|

|

|

|

|

Output High Z Delay |

tHZ |

- |

20ns |

- |

20ns |

|||

|

|

|

|

|

|

|

|

|

Note:Output high-impedance delay (tHZ) is measured from OE or CE going high, and this parameter guaranteed by design over the full voltage and temperature operating range - not tested.

P/N:PM0241 |

REV. 2.1, JUL. 18, 2001 |

3

Loading...

Loading...