SGS-THOMSON Microelectronics ST93C57M6TR, ST93C57M3TR, ST93C57M6013TR, ST93C57M3013TR, ST93C57M1TR Datasheet

...

ST93C56, 56C

ST93C57C

2K (128 x 16 or 256 x 8)SERIALMICROWIREEEPROM

NOT FOR NEW DESIGN

June 1997 1/13

This isinformation on a productstill in productionbutnot recommendedfor new designs.

AI00881C

D

V

CC

ST93C56

ST93C57

V

SS

C

Q

S

ORG

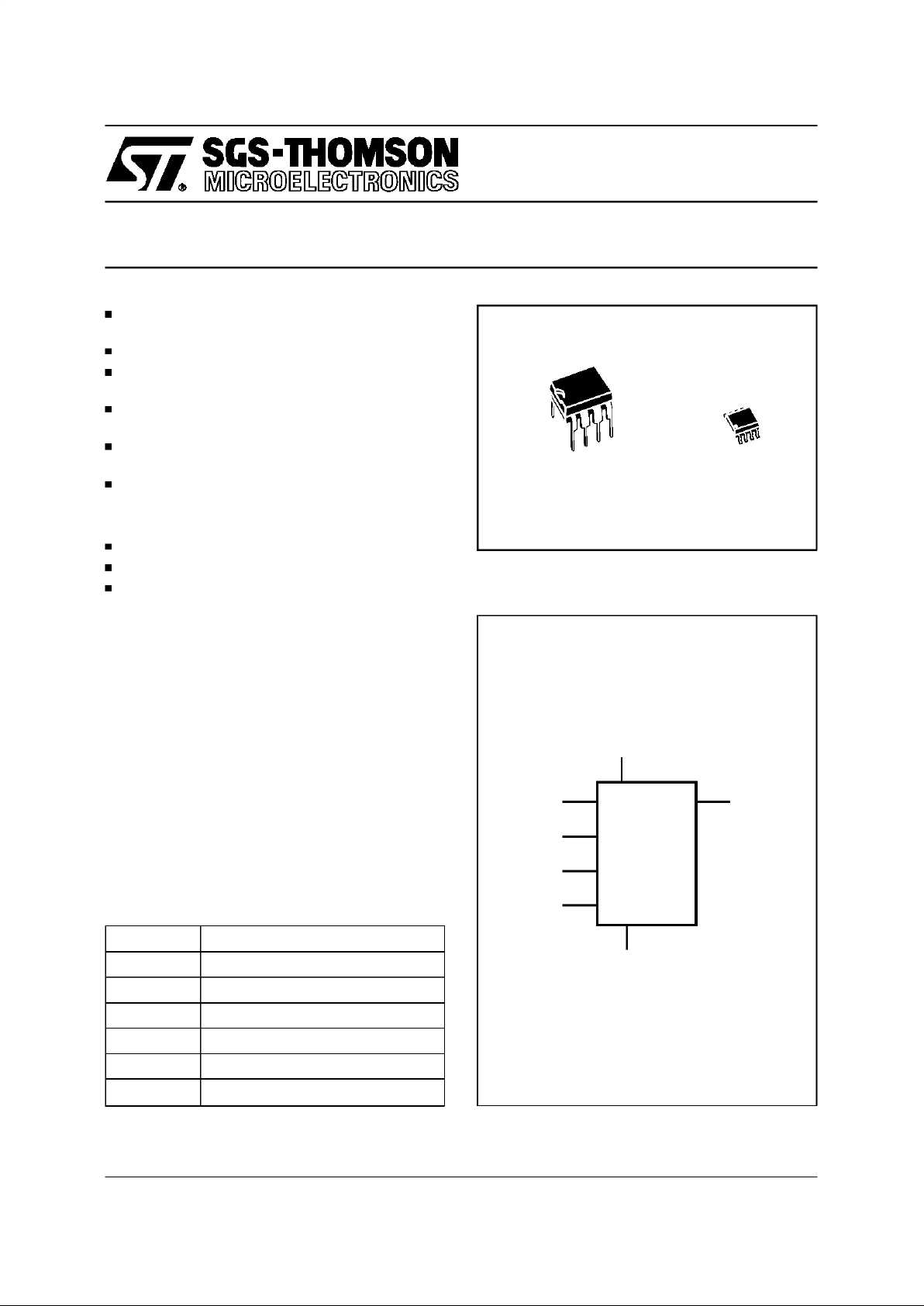

Figure 1. Logic Diagram

1 MILLIONERASE/WRITE CYCLES, with

40 YEARS DATARETENTION

DUALORGANIZATION:128 x 16 or 256 x 8

BYTE/WORDand ENTIRE MEMORY

PROGRAMMINGINSTRUCTIONS

SELF-TIMED PROGRAMMINGCYCLE with

AUTO-ERASE

READY/BUSYSIGNALDURING

PROGRAMMING

SINGLESUPPLYVOLTAGE:

– 4.5V to 5.5V for ST93C56version

– 3V to 5.5V for ST93C57 version

SEQUENTIALREAD OPERATION

5ms TYPICALPROGRAMMINGTIME

ST93C56,ST93C56C,ST93C57Care

replacedby the M93C56

DESCRIPTION

This specification covers a range of 2K bit serial

EEPROM products, the ST93C56, 56C specified

at 5V ± 10%and the ST93C57C specified at 3Vto

5.5V. In the text, products are referred to as

ST93C56.

The ST93C56 is a 2K bit Electrically Erasable

ProgrammableMemory(EEPROM)fabricatedwith

SGS-THOMSON’sHighEnduranceSinglePolysili-

con CMOS technology. The memory is accessed

through a serial input (D) and output (Q). The 2K

bit memory is divided into either 256 x 8 bit bytes

or 128 x 16 bit words. The organization may be

selectedby a signalappliedon the ORG input.

S Chip Select Input

D Serial Data Input

Q Serial Data Output

C Serial Clock

ORG Organisation Select

V

CC

Supply Voltage

V

SS

Ground

Table 1. Signal Names

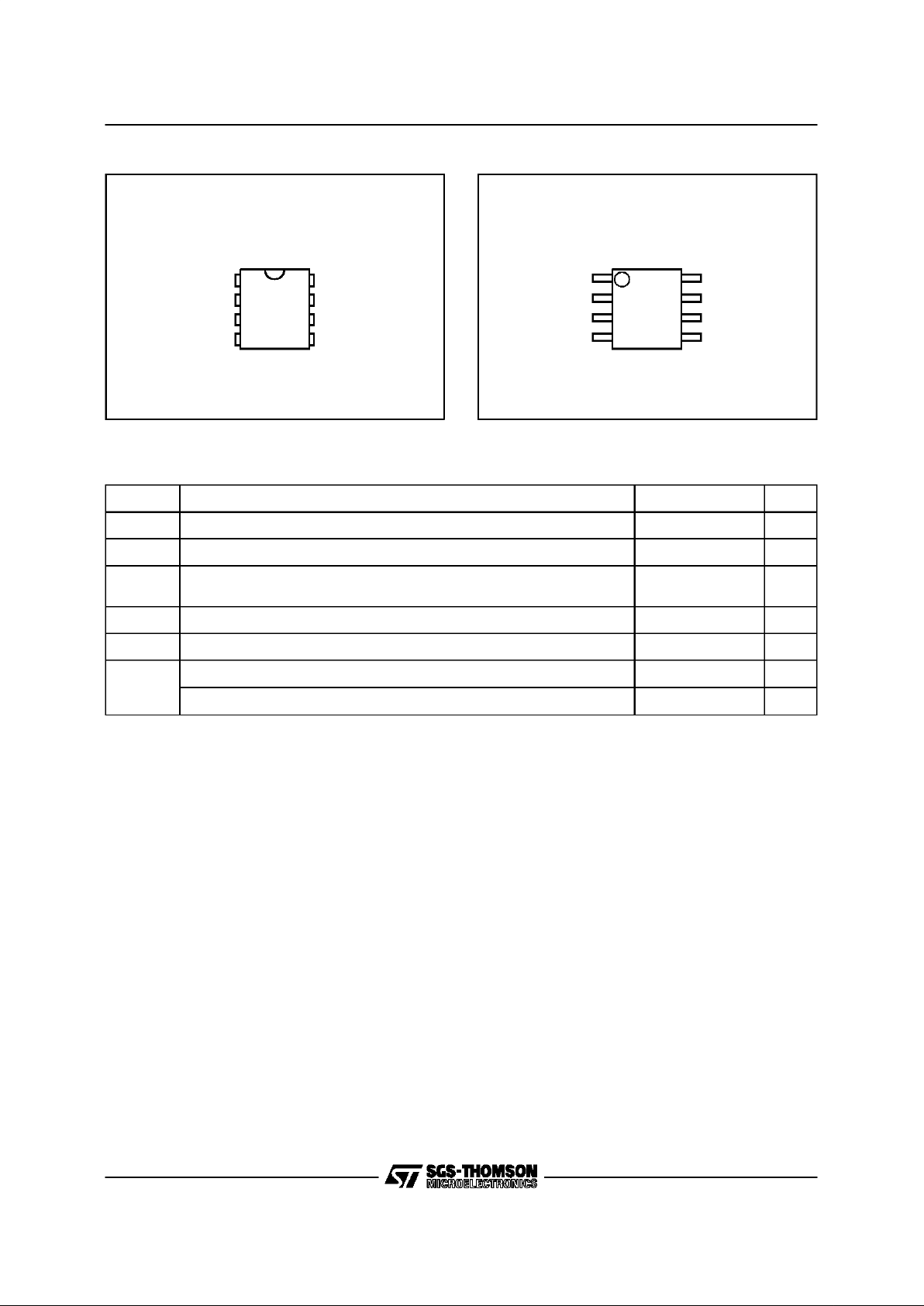

8

1

SO8 (M)

150mil Width

8

1

PSDIP8 (B)

0.4mm Frame

The memory is accessed by a set of instructions

which includes Read a byte/word, Write a

byte/word,Erasea byte/word, Erase All and Write

All. AReadinstructionloads theaddressof the first

byte/word to be read into an internal address

pointer. The datacontained at this addressis then

clocked out serially. The address pointer is auto-

maticallyincrementedafter the data is output and,

if the Chip Select input (S) is held High, the

ST93C56 can output a sequential stream of data

bytes/words.In this way,the memorycan be read

as a data stream from 8 to 2048 bits long, or

continuouslyas the addresscounterautomatically

rolls over to ’00’ when the highest address is

reached.Programming is internally self-timed (the

external clock signal on C input may be discon-

nectedorleftrunningafterthestart ofa Writecycle)

and does not require an erase cycle prior to the

Write instruction. The Write instruction writes8 or

16 bits at one time into oneof the256bytesor128

words. After the startof the programming cycle, a

Busy/Readysignal is available on the Data output

(Q)when Chip Select (S) is driven High.

The design of the ST93C56 and the High Endur-

anceCMOStechnologyusedforitsfabricationgive

an Erase/Write cycle Enduranceof 1,000,000cy-

clesand a data retention of 40 years.

TheDU (Don’tUse) pindoes notaffectthefunction

of the memory and it is reserved for use by SGS-

THOMSON duringtestsequences.Thepinmaybe

left unconnectedor may be connected to V

CC

or

V

SS

. Direct connection of DU to V

SS

is recom-

mended for the lowest standby power consump-

tion.

V

SS

Q

ORG

DUC

SV

CC

D

AI00882C

ST93C56

ST93C57

1

2

3

4

8

7

6

5

Figure2A. DIPPin Connections

1

V

SS

Q

ORG

DUC

SV

CC

D

AI00883D

ST93C56

ST93C57

2

3

4

8

7

6

5

Figure2B. SO Pin Connections

DESCRIPTION (cont’d)

Warning: DU = Don’t Use Warning: DU = Don’t Use

Symbol Parameter Value Unit

T

A

Ambient Operating Temperature –40 to125 °C

T

STG

Storage Temperature –65 to150 °C

T

LEAD

Lead Temperature,Soldering (SO8 package)

(PSDIP8 package)

40 sec

10 sec

215

260

°C

V

IO

Input or Output Voltages(Q = V

OH

or Hi-Z) –0.3 to V

CC

+0.5 V

V

CC

Supply Voltage –0.3 to 6.5 V

V

ESD

Electrostatic Discharge Voltage (Human Body model)

(2)

4000 V

Electrostatic Discharge Voltage (Machine model)

(3)

500 V

Notes: 1. Exceptfor the rating ”Operating Temperature Range”, stresses above those listed in the Table ”Absolute Maximum Ratings”

may cause permanent damage to thedevice. These are stress ratings only and operation of the device at these or any other

conditions abovethose indicated in the Operating sections of this specification is not implied. Exposure toAbsolute Maximum

Rating conditions for extended periods may affect device reliability.Refer also to the SGS-THOMSON SURE Program and other

relevant quality documents.

2. MIL-STD-883C, 3015.7(100pF, 1500 Ω).

3. EIAJ IC-121 (Condition C) (200pF, 0 Ω).

Table 2. Absolute MaximumRatings

(1)

2/13

ST93C56/56C, ST93C57C

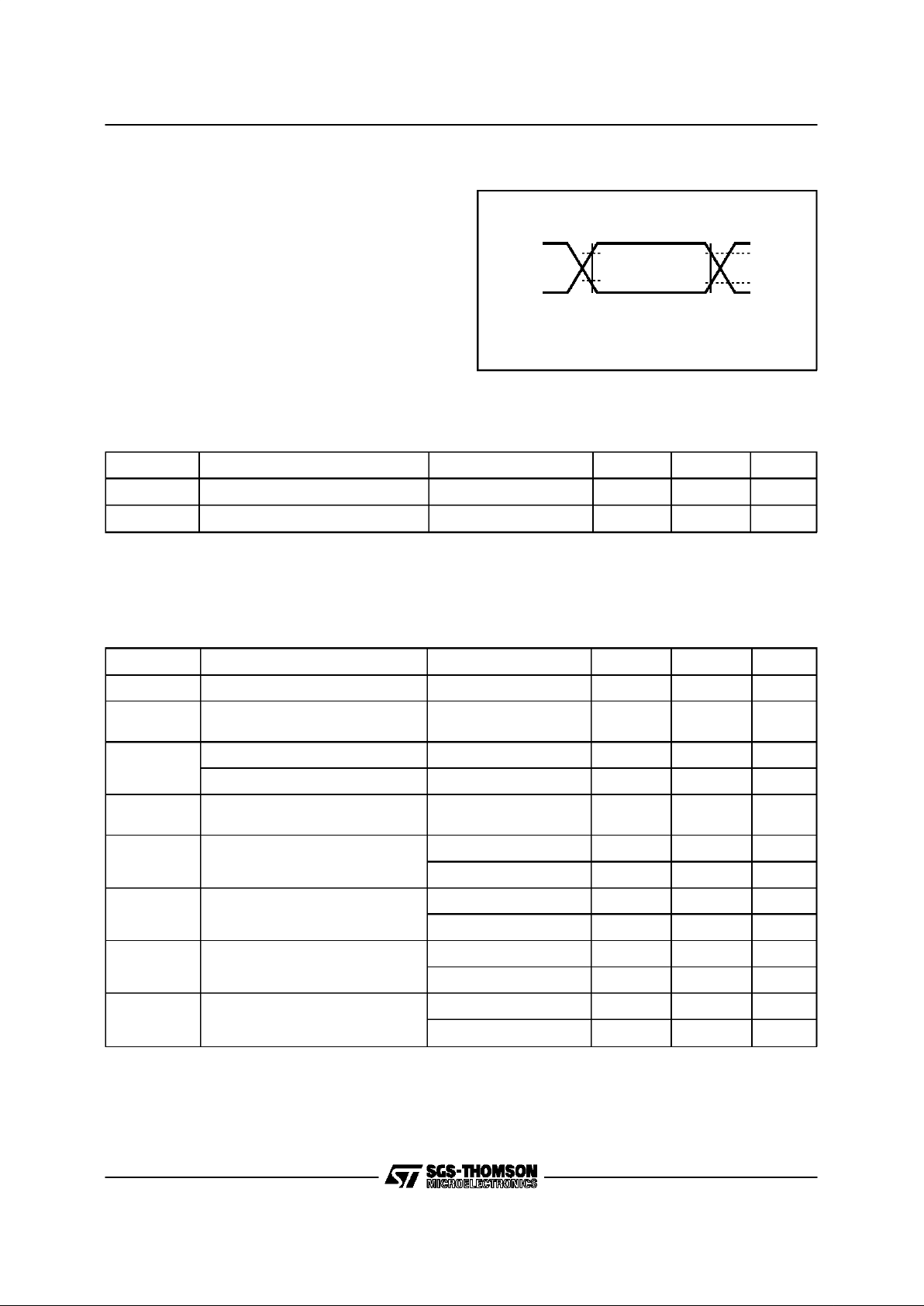

Input Rise and Fall Times ≤ 20ns

Input Pulse Voltages 0.4V to 2.4V

Input Timing Reference Voltages 1V to 2.0V

Output Timing Reference Voltages 0.8V to 2.0V

AC MEASUREMENT CONDITIONS

Note that Output Hi-Z is defined as the point where data

is no longer driven.

AI00815

2.4V

0.4V

2.0V

0.8V

2V

1V

INPUT OUTPUT

Figure 3. ACTesting Input Output Waveforms

Symbol Parameter Test Condition Min Max Unit

C

IN

Input Capacitance V

IN

=0V 5 pF

C

OUT

Output Capacitance V

OUT

=0V 5 pF

Note: 1. Sampled only, not 100% tested.

Table 3. Capacitance

(1)

(T

A

=25°C, f =1 MHz )

Symbol Parameter TestCondition Min Max Unit

I

LI

Input Leakage Current 0V ≤ V

IN

≤ V

CC

±2.5 µA

I

LO

Output Leakage Current

0V ≤ V

OUT

≤ V

CC

,

Q inHi-Z

±2.5 µA

I

CC

Supply Current (TTL Inputs) S = V

IH

, f = 1 MHz 3 mA

Supply Current (CMOS Inputs) S = V

IH

, f = 1 MHz 2 mA

I

CC1

Supply Current (Standby)

S=V

SS

,C=V

SS

,

ORG = V

SS

or V

CC

50 µA

V

IL

Input Low Voltage (D, C, S)

V

CC

=5V±10% –0.3 0.8 V

3V ≤ V

CC

≤ 4.5V –0.3 0.2V

CC

V

V

IH

Input High Voltage (D, C, S)

V

CC

=5V±10% 2 V

CC

+1 V

3V ≤ V

CC

≤ 4.5V 0.8 V

CC

V

CC

+1 V

V

OL

Output Low Voltage

I

OL

= 2.1mA 0.4 V

I

OL

=10µA 0.2 V

V

OH

Output High Voltage

I

OH

= –400µA 2.4 V

I

OH

= –10µAV

CC

–0.2 V

Table 4. DC Characteristics

(T

A

= 0 to70°C or –40 to 85°C; V

CC

= 4.5V to 5.5V or 3V to 5.5V)

3/13

ST93C56/56C, ST93C57C

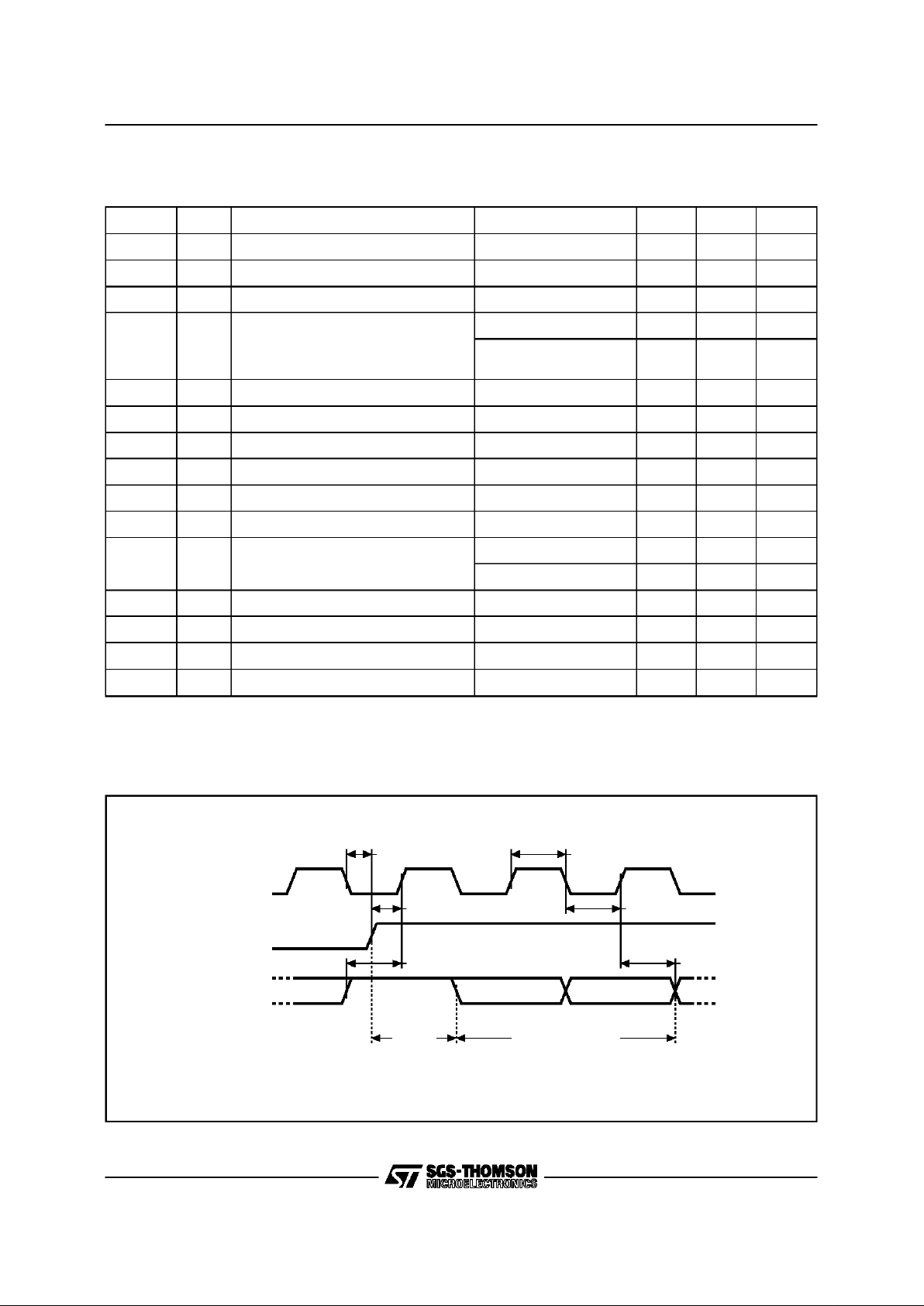

Symbol Alt Parameter Test Condition Min Max Unit

t

SHCH

t

CSS

Chip Select High to Clock High 50 ns

t

CLSH

t

SKS

Clock Low to Chip Select High 100 ns

t

DVCH

t

DIS

Input Valid to Clock High 100 ns

t

CHDX

t

DIH

Clock High to Input Transition

Temp.Range: grade 1 100 ns

Temp.Range:

grades 3, 6

200 ns

t

CHQL

t

PD0

Clock High to Output Low 500 ns

t

CHQV

t

PD1

Clock High to Output Valid 500 ns

t

CLSL

t

CSH

Clock Low to Chip Select Low 0 ns

t

SLCH

Chip Select Low to ClockHigh 250 ns

t

SLSH

t

CS

Chip Select Low to Chip Select High Note 1 250 ns

t

SHQV

t

SV

Chip Select High to Output Valid 500 ns

t

SLQZ

t

DF

Chip Select Low to Output Hi-Z

ST93C56 300 ns

ST93C56C, 57C 200 ns

t

CHCL

t

SKH

Clock High to Clock Low Note 2 250 ns

t

CLCH

t

SKL

Clock Low to Clock High Note 2 250 ns

t

W

t

WP

Erase/Write Cycle time 10 ms

f

C

f

SK

Clock Frequency 0 1 MHz

Notes: 1. Chip Select must bebrought low for a minimum of 250 ns(t

SLSH

) betweenconsecutive instructioncycles.

2. The Clock frequency specification calls for aminimum clock period of 1 µs, therefore the sum of the timings t

CHCL

+t

CLCH

must be greater or equal to 1 µs. For example, ift

CHCL

is 250 ns, then t

CLCH

must be at least 750ns.

Table 5. AC Characteristics

(T

A

= 0 to70°C or –40 to 85°C; V

CC

= 4.5V to 5.5V or 3V to 5.5V)

AI01428

C

OP CODE OP CODESTART

S

D

OP CODE INPUTSTART

tDVCH

tSHCH

tCLSH tCHCL

tCLCH

tCHDX

Figure4. Synchronous Timing, Start and Op-CodeInput

4/13

ST93C56/56C, ST93C57C

Loading...

Loading...