Maxim MAX1113CPE, MAX1113CEE, MAX1112MJP, MAX1112EPP, MAX1112EAP Datasheet

...

KIT

EVALUATION

AVAILABLE

Description

-power, 8-bit, 8-chan- (ADCs) that feature an clock, and serial a single +4.5V to +5.5V while sampling at 8 analog inputs

inputs are software-con- and single-

are performed an external serial-inter- input range is deterreference, or by an from 1V to VDD. with the SPI™, -interface standards.

the end-of-conversion

.

a software-program- down mode to minimize -down, the supply 1ksps, and only 82µA at be controlled using the

SHDN input pin. Accessing the serial interface automatically powers up the device.

The MAX1112 is available in 20-pin SSOP and DIP packages. The MAX1113 is available in small 16-pin QSOP and DIP packages.

________________________Applications

Portable Data Logging

Hand-Held Measurement Devices

Medical Instruments

System Diagnostics

Solar-Powered Remote Systems

4–20mA-Powered Remote

Data-Acquisition Systems

Pin Configurations appear at end of data sheet.

SPI and QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corp.

Serial 8-Bit ADCs

____________________________Features

♦+4.5V to +5.5V Single Supply

♦Low Power: 135µA at 50ksps

13µA at 1ksps

♦8-Channel Single-Ended or 4-Channel Differential Inputs (MAX1112)

♦4-Channel Single-Ended or 2-Channel Differential Inputs (MAX1113)

♦Internal Track/Hold; 50kHz Sampling Rate

♦Internal 4.096V Reference

♦SPI/QSPI/MICROWIRE-Compatible Serial Interface

♦Software-Configurable Unipolar or Bipolar Inputs

♦Total Unadjusted Error: ±1LSB (max)

±0.3LSB (typ)

Ordering Information

PART |

TEMP. RANGE |

PIN-PACKAGE |

|

|

|

MAX1112CPP |

0°C to +70°C |

20 Plastic DIP |

|

|

|

MAX1112CAP |

0°C to +70°C |

20 SSOP |

|

|

|

MAX1112C/D |

0°C to +70°C |

Dice* |

*Dice are specified at TA = +25°C, DC parameters only.

Ordering Information continued at end of data sheet.

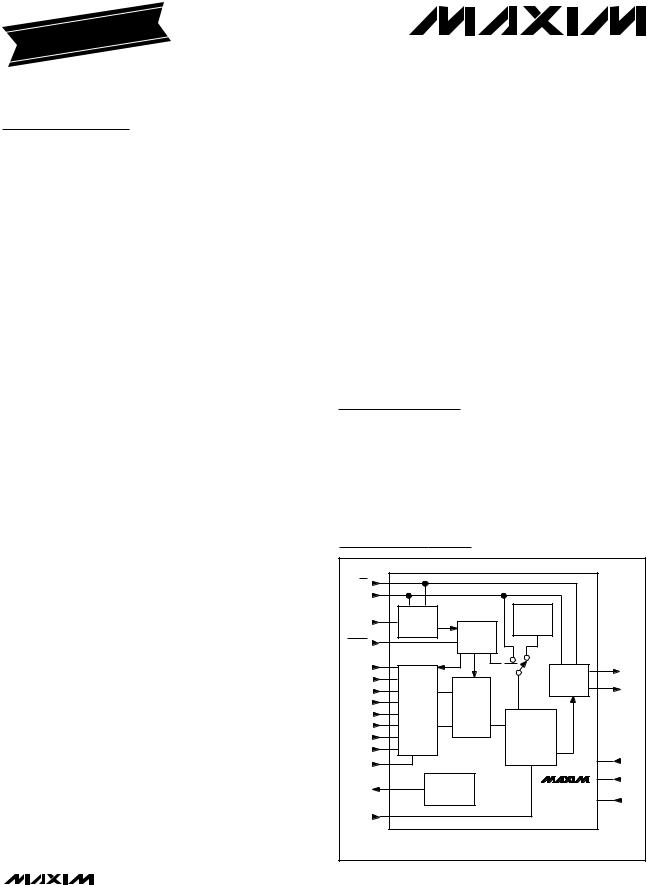

Functional Diagram

CS |

|

|

|

|

SCLK |

|

|

|

|

|

INPUT |

|

INT |

|

DIN |

SHIFT |

|

CLOCK |

|

|

REGISTER |

CONTROL |

|

|

SHDN |

|

LOGIC |

|

|

CH0 |

|

|

OUTPUT |

DOUT |

CH1 |

|

|

||

|

|

SHIFT |

|

|

CH2 |

ANALOG |

|

REGISTER |

SSTRB |

CH3 |

T/H |

|

|

|

CH4* |

INPUT |

CLOCK |

|

|

MUX |

|

|||

CH5* |

IN |

|

|

|

|

8-BIT |

|

||

CH6* |

|

|

||

|

SAR ADC |

|

||

CH7* |

|

|

||

|

|

OUT |

|

|

|

|

|

|

|

COM |

|

|

REF |

VDD |

REFOUT |

|

+4.096V |

MAX1112 |

DGND |

|

|

|||

REFERENCE |

AGND |

|||

|

|

|

MAX1113 |

|

REFIN |

|

|

|

|

*MAX1112 ONLY

________________________________________________________________ Maxim Integrated Products 1

MAX1112/MAX1113

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800. For small orders, phone 1-800-835-8769.

MAX1112/MAX1113

+5V, Low-Power, Multi-Channel,

Serial 8-Bit ADCs

ABSOLUTE MAXIMUM RATINGS

VDD to AGND.............................................................. |

-0.3V to 6V |

AGND to DGND ....................................................... |

-0.3V to 0.3V |

CH0–CH7, COM, REFIN, |

-0.3V to (VDD + 0.3V) |

REFOUT to AGND ................................... |

|

Digital Inputs to DGND ............................................... |

-0.3V to 6V |

Digital Outputs to DGND............................ |

-0.3V to (VDD + 0.3V) |

Continuous Power Dissipation (TA = +70°C) |

|

16 Plastic DIP (derate 10.53mW/°C above +70°C) ...... |

842mW |

16 QSOP (derate 8.30mW/°C above +70°C)................ |

667mW |

16 CERDIP (derate 10.00mW/°C above +70°C) .......... |

800mW |

20 Plastic DIP (derate 11.11mW/°C above +70°C) |

......889mW |

|

20 SSOP (derate 8.00mW/°C above +70°C) |

................ |

640mW |

20 CERDIP (derate 11.11mW/°C above +70°C) .......... |

889mW |

|

Operating Temperature Ranges |

|

|

MAX1112C_P/MAX1113C_E................................ |

0°C to +70°C |

|

MAX1112E_P/MAX1113E_E ............................. |

- 40°C to +85°C |

|

MAX1112MJP/MAX1113MJE.......................... |

- 55°C to +125°C |

|

Storage Temperature Range ............................. |

- 65°C to +150°C |

|

Lead Temperature (soldering, 10sec) ............................. |

|

+300°C |

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

ELECTRICAL CHARACTERISTICS

(VDD = +4.5V to +5.5V; unipolar input mode; COM = 0V; fSCLK = 500kHz, external clock (50% duty cycle); 10 clocks/conversion cycle (50ksps); 1µF capacitor at REFOUT; TA = TMIN to TMAX; unless otherwise noted.)

PARAMETER |

SYMBOL |

CONDITIONS |

MIN |

TYP |

MAX |

UNITS |

|

|

|

|

|

|

|

|

|

DC ACCURACY |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Resolution |

|

|

8 |

|

|

Bits |

|

|

|

|

|

|

|

|

|

Relative Accuracy (Note 1) |

INL |

|

|

±0.1 |

±0.5 |

LSB |

|

|

|

|

|

|

|

|

|

Differential Nonlinearity |

DNL |

No missing codes over temperature |

|

|

±1 |

LSB |

|

|

|

|

|

|

|

|

|

Offset Error |

|

|

|

±0.3 |

±1 |

LSB |

|

|

|

|

|

|

|

|

|

Gain Error (Note 2) |

|

Internal or external reference |

|

|

±1 |

LSB |

|

|

|

|

|

|

|

|

|

Gain Temperature Coefficient |

|

External reference, 4.096V |

|

±0.8 |

|

ppm/°C |

|

|

|

|

|

|

|

|

|

Total Unadjusted Error |

TUE |

MAX111_C/E |

|

±0.3 |

±1 |

LSB |

|

|

|

|

|

|

|

|

|

Channel-to-Channel |

|

|

|

±0.1 |

|

LSB |

|

Offset Matching |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DYNAMIC SPECIFICATIONS (10.034kHz sine- |

wave input, 4.096Vp-p, 50ksps, 500kHz external clock) |

|

|

|

|

||

|

|

|

|

|

|

|

|

Signal-to-Noise |

SINAD |

|

|

49 |

|

dB |

|

and Distortion Ratio |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Total Harmonic Distortion |

THD |

|

|

-70 |

|

dB |

|

(up to the 5th harmonic) |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Spurious-Free Dynamic Range |

SFDR |

|

|

68 |

|

dB |

|

|

|

|

|

|

|

|

|

Channel-to-Channel Crosstalk |

|

VCH_ = 4.096Vp-p, 25kHz (Note 3) |

|

-75 |

|

dB |

|

|

|

|

|

|

|

|

|

Small-Signal Bandwidth |

|

-3dB rolloff |

|

1.5 |

|

MHz |

|

|

|

|

|

|

|

|

|

Full-Power Bandwidth |

|

|

|

800 |

|

kHz |

|

|

|

|

|

|

|

|

|

2 _______________________________________________________________________________________

+5V, Low-Power, Multi-Channel,

Serial 8-Bit ADCs

ELECTRICAL CHARACTERISTICS (continued)

(VDD = +4.5V to +5.5V; unipolar input mode; COM = 0V; fSCLK = 500kHz, external clock (50% duty cycle); 10 clocks/conversion cycle (50ksps); 1µF capacitor at REFOUT; TA = TMIN to TMAX; unless otherwise noted.)

PARAMETER |

SYMBOL |

CONDITIONS |

MIN |

TYP |

MAX |

UNITS |

||

|

|

|

|

|

|

|

|

|

CONVERSION RATE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Conversion Time (Note 4) |

tCONV |

Internal clock |

|

|

25 |

55 |

µs |

|

|

|

|

|

|

|

|||

External clock, 500kHz, 10 clocks/conversion |

20 |

|

|

|||||

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

Track/Hold Acquisition Time |

tACQ |

External clock, 2MHz |

|

1 |

|

|

µs |

|

|

|

|

|

|

|

|

|

|

Aperture Delay |

|

|

|

|

|

10 |

|

ns |

|

|

|

|

|

|

|

|

|

Aperture Jitter |

|

|

|

|

|

<50 |

|

ps |

|

|

|

|

|

|

|

|

|

Internal Clock Frequency |

|

|

|

|

|

400 |

|

kHz |

|

|

|

|

|

|

|

|

|

External Clock-Frequency Range |

|

(Note 5) |

|

50 |

|

500 |

kHz |

|

|

|

|

|

|

|

|

|

|

|

Used for data transfer only |

|

|

2 |

MHz |

|||

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

ANALOG INPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Voltage Range, Single- |

|

Unipolar input, COM = 0V |

0 |

|

VREFIN |

|

||

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

COM ± |

||

Ended and Differential (Note 6) |

|

Bipolar input, COM = VREFIN / 2 |

|

|

||||

|

|

VREFIN / 2 |

|

|||||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Multiplexer Leakage Current |

|

On/off leakage current, VCH_ = 0V or VDD |

|

±0.01 |

±1 |

µA |

||

|

|

|

|

|

|

|

|

|

Input Capacitance |

|

|

|

|

|

18 |

|

pF |

|

|

|

|

|

|

|

|

|

INTERNAL REFERENCE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

REFOUT Voltage |

|

|

|

|

3.936 |

4.096 |

4.256 |

V |

|

|

|

|

|

|

|

|

|

REFOUT Short-Circuit Current |

|

|

|

|

|

6 |

|

mA |

|

|

|

|

|

|

|

|

|

REFOUT Temperature Coefficient |

|

|

|

|

|

±50 |

|

ppm/°C |

|

|

|

|

|

|

|

|

|

Load Regulation (Note 7) |

|

0mA to 0.5mA output load |

|

4.5 |

|

mV |

||

|

|

|

|

|

|

|

|

|

Capacitive Bypass at REFOUT |

|

|

|

|

1 |

|

|

µF |

|

|

|

|

|

|

|

|

|

EXTERNAL REFERENCE AT REFIN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Voltage Range |

|

|

|

|

1 |

|

VDD + |

V |

|

|

|

|

|

50mV |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Current |

|

(Note 8) |

|

|

1 |

20 |

µA |

|

|

|

|

|

|

|

|

|

|

POWER REQUIREMENTS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Supply Voltage |

VDD |

|

|

|

4.5 |

|

5.5 |

V |

|

|

|

|

|

|

|

|

|

|

|

Full-scale input |

|

Operating mode |

|

135 |

250 |

|

|

|

CLOAD = 10pF |

|

Reference disabled |

|

95 |

|

µA |

Supply Current |

IDD |

|

|

|

|

|

|

µA |

Power-down |

|

Software |

|

2 |

|

|||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

SHDN at DGND |

|

3.2 |

10 |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

Power-Supply Rejection |

PSR |

VDD = 4.5V to 5.5V; external reference, |

|

±0.4 |

±4 |

mV |

||

(Note 9) |

4.096V; full-scale input |

|

|

|||||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

MAX1112/MAX1113

_______________________________________________________________________________________ 3

MAX1112/MAX1113

+5V, Low-Power, Multi-Channel,

Serial 8-Bit ADCs

ELECTRICAL CHARACTERISTICS (continued)

(VDD = +4.5V to +5.5V; unipolar input mode; COM = 0V; fSCLK = 500kHz, external clock (50% duty cycle); 10 clocks/conversion cycle (50ksps); 1µF capacitor at REFOUT; TA = TMIN to TMAX; unless otherwise noted.)

PARAMETER |

|

SYMBOL |

CONDITIONS |

|

MIN |

TYP |

MAX |

UNITS |

|

|

|

|

|

|

|

|

|

|

|

DIGITAL INPUTS: DIN, SCLK, CS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIN, SCLK, CS Input High Voltage |

|

VIH |

|

|

3 |

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

DIN, SCLK, CS Input Low Voltage |

|

VIL |

|

|

|

|

0.8 |

V |

|

|

|

|

|

|

|

|

|

|

|

DIN, SCLK, CS Input Hysteresis |

|

VHYST |

|

|

|

0.2 |

|

V |

|

|

|

|

|

|

|

|

|

|

|

DIN, SCLK, CS Input Leakage |

|

IIN |

Digital inputs = 0V or VDD |

|

|

|

±1 |

µA |

|

|

|

|

|

|

|

|

|

|

|

DIN, SCLK, CS Input Capacitance |

|

CIN |

(Note 5) |

|

|

15 |

pF |

||

|

|

|

|

|

|

|

|

|

|

SHDN INPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SHDN Input High Voltage |

|

VSH |

|

|

VDD - 0.4 |

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

SHDN Input Mid-Voltage |

|

VSM |

|

|

1.1 |

|

VDD - 1.1 |

V |

|

|

|

|

|

|

|

|

|

|

|

SHDN Voltage, Floating |

|

VFLT |

SHDN = open |

|

VDD / 2 |

|

V |

||

|

|

|

|

|

|

|

|

|

|

SHDN Input Low Voltage |

|

VSL |

|

|

|

|

0.4 |

V |

|

|

|

|

|

|

|

|

|

|

|

SHDN Input Current |

|

|

SHDN = 0V or VDD |

|

|

|

±4 |

µA |

|

|

|

|

|

|

|

|

|

|

|

SHDN Maximum Allowed Leakage |

|

|

SHDN = open |

|

|

±100 |

nA |

||

for Mid-Input |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIGITAL OUTPUTS: DOUT, SSTRB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Low Voltage |

|

VOL |

ISINK = 5mA |

|

|

0.4 |

V |

|

|

|

|

|

|

|

|

|

|||

|

ISINK = 16mA |

|

|

|

0.8 |

|

|||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

Output High Voltage |

|

VOH |

ISOURCE = 0.5mA |

|

VDD - 0.5 |

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

Three-State Leakage Current |

|

IL |

CS = VDD |

|

|

±0.01 |

±10 |

µA |

|

|

|

|

|

|

|

|

|

|

|

Three-State Output Capacitance |

|

COUT |

CS = VDD (Note 5) |

|

|

15 |

pF |

||

|

|

|

|

|

|

|

|

|

|

4 _______________________________________________________________________________________

+5V, Low-Power, Multi-Channel,

Serial 8-Bit ADCs

TIMING CHARACTERISTICS (Figures 8 and 9)

(VDD = +4.5V to +5.5V, TA = TMIN to TMAX, unless otherwise noted.)

PARAMETER |

SYMBOL |

CONDITIONS |

|

MIN |

TYP |

MAX |

UNITS |

|

|

|

|

|

|

|

|

|

|

Track/Hold Acquisition Time |

tACQ |

|

|

|

1 |

|

|

µs |

|

|

|

|

|

|

|

|

|

DIN to SCLK Setup |

tDS |

|

|

|

100 |

|

|

ns |

|

|

|

|

|

|

|

|

|

DIN to SCLK Hold |

tDH |

|

|

|

0 |

|

|

ns |

|

|

|

|

|

|

|

|

|

SCLK Fall to Output Data Valid |

tDO |

Figure 1, |

MAX111_C/E |

|

20 |

|

200 |

ns |

CLOAD = 100pF |

MAX111_M |

|

20 |

|

240 |

|||

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

CS Fall to Output Enable |

tDV |

Figure 1, CLOAD = 100pF |

|

|

240 |

ns |

||

|

|

|

|

|

|

|

|

|

CS Rise to Output Disable |

tTR |

Figure 2, CLOAD = 100pF |

|

|

|

240 |

ns |

|

|

|

|

|

|

|

|

|

|

CS to SCLK Rise Setup |

tCSS |

|

|

|

100 |

|

|

ns |

|

|

|

|

|

|

|

|

|

CS to SCLK Rise Hold |

tCSH |

|

|

|

0 |

|

|

ns |

|

|

|

|

|

|

|

|

|

SCLK Pulse Width High |

tCH |

|

|

|

200 |

|

|

ns |

|

|

|

|

|

|

|

|

|

SCLK Pulse Width Low |

tCL |

|

|

|

200 |

|

|

ns |

|

|

|

|

|

|

|

|

|

SCLK Fall to SSTRB |

tSSTRB |

CLOAD = 100pF |

|

|

|

|

240 |

ns |

|

|

|

|

|

|

|

|

|

CS Fall to SSTRB Output Enable |

tSDV |

Figure 1, external clock mode only, |

|

|

|

240 |

ns |

|

(Note 5) |

CLOAD = 100pF |

|

|

|

|

|||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

CS Rise to SSTRB Output |

tSTR |

Figure 2, external clock mode only, |

|

|

|

240 |

ns |

|

Disable (Note 5) |

CLOAD = 100pF |

|

|

|

|

|||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

SSTRB Rise to SCLK Rise |

tSCK |

Figure 11, internal clock mode only |

|

0 |

|

|

ns |

|

(Note 5) |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Wakeup Time |

tWAKE |

External reference |

|

|

|

20 |

|

µs |

|

|

|

|

|

|

|

||

Internal reference (Note 10) |

|

|

24 |

|

ms |

|||

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

Note 1: Relative accuracy is the analog value’s deviation (at any code) from its theoretical value after the full-scale range is calibrated. Note 2: VREFIN = 4.096V, offset nulled.

Note 3: On-channel grounded; sine wave applied to all off-channels.

Note 4: Conversion time is defined as the number of clock cycles multiplied by the clock period; clock has 50% duty cycle. Note 5: Guaranteed by design. Not subject to production testing.

Note 6: Common-mode range for the analog inputs is from AGND to VDD.

Note 7: External load should not change during the conversion for specified accuracy. Note 8: External reference at 4.096V, full-scale input, 500kHz external clock.

Note 9: Measured as | VFS (4.5V) - VFS (5.5V) |.

Note 10: 1µF at REFOUT; internal reference settling to 0.5LSB.

MAX1112/MAX1113

_______________________________________________________________________________________ 5

MAX1112/MAX1113

+5V, Low-Power, Multi-Channel,

Serial 8-Bit ADCs

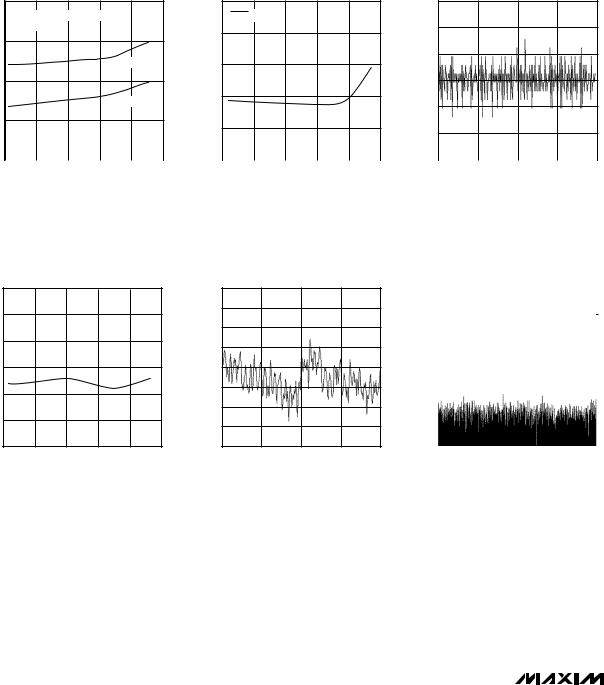

__________________________________________Typical Operating Characteristics

(VDD = +5.0V; fSCLK = 500kHz; external clock (50% duty cycle); RL = ∞; TA = +25°C, unless otherwise noted.)

|

SUPPLY CURRENT vs. TEMPERATURE |

|

|

|

SHUTDOWN SUPPLY CURRENT |

|

|

|

DIFFERENTIAL NONLINEARITY |

|

|

|

|

vs. TEMPERATURE |

|

|

|

vs. CODE |

|

|

180 |

MAX1112/13-01 |

A)(μ |

10 |

|

MAX1112/13-02 |

|

0.3 |

MAX1112/13-03 |

|

OUTPUT CODE = FULL SCALE |

|

SHDN = DGND |

|

|

||||

|

CLOAD = 10pF |

|

|

8 |

|

|

|

0.2 |

|

A)(CURRENTSUPPLYμ |

160 |

|

CURRENTSUPPLYSHUTDOWN |

|

|

(LSB)DNL |

-0.2 |

|

|

|

2 |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

VDD = 5.5V |

|

|

6 |

|

|

|

0.1 |

|

|

|

|

|

|

|

|

|

||

|

140 |

|

|

|

|

|

|

0 |

|

|

VDD = 4.5V |

|

|

4 |

|

|

|

-0.1 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

120 |

|

|

|

|

|

|

|

|

100 |

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

-0.3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

-60 |

-20 |

20 |

60 |

100 |

140 |

-60 |

-20 |

20 |

60 |

100 |

140 |

0 |

64 |

128 |

192 |

256 |

||||||

|

|

|

TEMPERATURE (°C) |

|

|

|

|

|

|

TEMPERATURE (°C) |

|

|

|

|

|

|

DIGITAL CODE |

|

|

|

||

OFFSET ERROR (LSB)

0.6

0.5

0.4

0.3

0.2

0.1

0

OFFSET ERROR vs. TEMPERATURE

MAX1112/13-04

-60 |

-20 |

20 |

60 |

100 |

140 |

TEMPERATURE (°C)

INL (LSB)

0.20

0.15

0.10

0.05

0

-0.05

-0.10

-0.15

-0.20

INTEGRAL NONLINEARITY vs. CODE

AMPLITUDE (dB)

MAX1112/13-05

0 |

64 |

128 |

192 |

256 |

DIGITAL CODE

|

|

|

FFT PLOT |

|

|

|

|

|||

20 |

|

|

|

|

|

|

|

|

|

06 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

- |

|

|

|

|

|

fCH_ |

= 10.034kHz, 4Vp-p |

MAX1112/13 |

|||

0 |

|

|

|

|

fSAMPLE = 50ksps |

|

||||

|

|

|

|

|

||||||

-20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-40 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-60 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-80 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

5 |

10 |

15 |

20 |

25 |

|||||

FREQUENCY (kHz)

6 _______________________________________________________________________________________

Loading...

Loading...