Kenwood FGZ-201-ELF-2, FGZ-201-ERF-2 Service manual

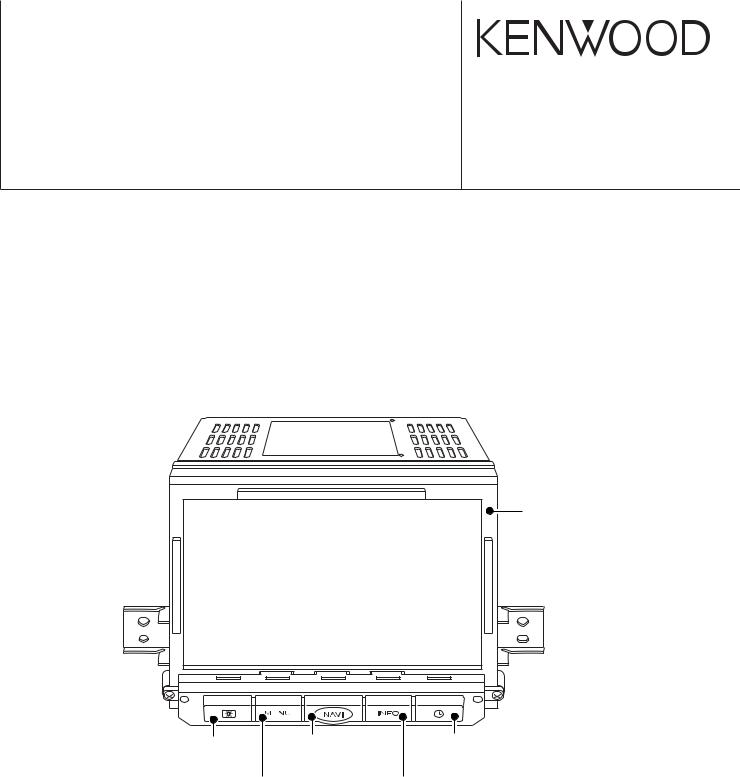

7 inch MULTIDISPLAY

FGZ201ELF2/ERF2

SERVICE MANUAL

© 2003-8 CREATED IN JAPAN B53-0084-00 (N) 0

SUBARU GENUINE

MODEL |

PARTS No. |

FGZ201ELF2 |

86281AG030 |

FGZ201ERF2 |

86281AG010 |

|

|

Panel

(A64-2772-21)

Liquid crystal (B38-1100-05)

Liquid crystal (B38-1100-05)

Knob (image adj.) K24-3974-24 (ERF2) K24-4009-24 (ELF2)

Knob (navi) |

|

K24-3973-24 |

(ERF2) |

K24-4008-24 |

(ELF2) |

Knob (clock) K24-3975-24 (ERF2) K24-4010-24 (ELF2)

Knob (menu) |

|

Knob (info.) |

|

K24-3971-24 |

(ERF2) |

K24-3972-24 |

(ERF2) |

K24-4011-24 |

(ELF2) |

K24-4012-24 |

(ELF2) |

FGZ201ELF2/ERF2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

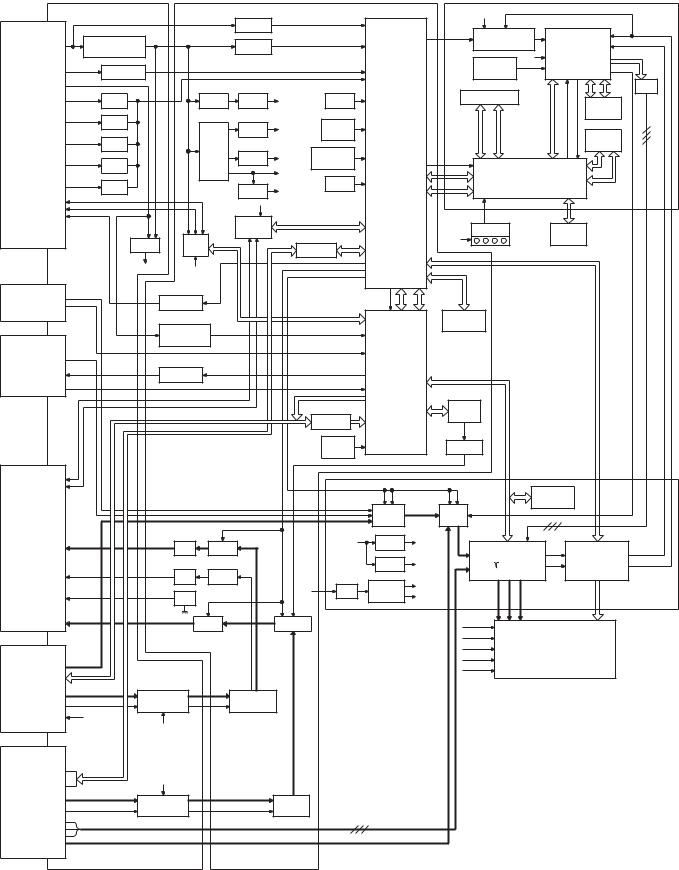

BLOCK DIAGRAM |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

SYNTHESIZER UNIT |

|

SYNTHESIZER UNIT |

|

|

|

|

ELECTRIC UNIT |

|

|

|

|

|

|

|

|

||||||||

(X14- ) (B/3)(C/3) |

|

(X14- ) (A/3) |

|

|

|

|

|

|

(X25- ) |

|

|

|

|

|

|

|

|

|

|

||||

J803 (B/3) |

|

|

|

|

|

|

|

|

|

IC5 |

|

|

P8.5V |

V-SYNC |

|

|

|

|

|

|

|

|

|

1-16PIN |

|

|

|

|

|

|

|

Q26,28 |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

+B DET |

|

|

|

|

|

|

|

IC4 |

|

|

|

|

|

|

||||

CAR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VD |

|

||||||

INTERFACE |

|

|

|

|

|

|

|

|

|

|

|

DATA |

SYNC |

|

|

|

|

|

|

|

|||

PROTECTION |

|

|

+B |

|

|

IC18 |

|

|

|

|

|

|

|

|

|

HD |

|

||||||

2. +BATT |

|

|

|

|

|

BU5V |

|

|

GENERATOR |

|

GRAPHIC |

|

|

||||||||||

CIRCUIT |

|

|

|

|

|

Q27,30 |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

P5V |

|

CONTROLLER |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

Q803 |

ACC DET |

|

|

|

|

|

|

|

|

|

|

SUB CLK |

|

|

|

|

|

|

|

|

||

4. ACC |

|

|

|

|

|

|

|

|

|

|

7.99MHz |

|

|

|

|

|

|

|

IC6 |

||||

12. ILL(PWM) |

Q801 |

|

|

|

IC20 |

Q49 |

|

|

IC1 |

|

|

FLASH ROM |

|

|

|

|

|

IC5 |

D/A |

||||

|

DET |

|

|

DC/D |

SW |

|

P5V |

RST |

|

|

|

|

|

|

|

|

|||||||

4. SPD |

|

|

|

|

|

CONTROL |

|

|

|

SDRAM |

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

7. PARKING |

|

DET |

|

|

|

Q31 |

|

|

|

SYSTEM |

|

|

DATA |

ADDRESS |

|

RST |

INT |

|

-CSYNC |

RGB |

|||

|

|

|

|

|

|

|

|

|

|

|

(8MB) |

|

|||||||||||

|

Q804 |

|

|

|

Q42 |

Q47 |

|

|

|

|

|

|

|

|

|

|

|

|

|

(8MB) |

|

|

|

8. IGN |

DET |

|

|

|

P-15.5V |

15MHz |

|

|

|

|

|

|

|

|

|

IC11 |

|

|

|

||||

|

Q800 |

|

|

|

|

REG. |

MAIN |

CPU1 |

|

|

|

|

|

|

|

|

|

SDRAM |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

Q805 |

|

|

|

SW |

REG. |

P18.5V |

32.768k |

MICRO- |

|

RST |

|

|

IC12 |

|

|

|

|

|

|

|

|

|

10. REVERSE |

DET |

|

|

|

SUB CLK |

PROCESSOR |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

P8.5V |

|

|

|

|

|

GRAPHIC |

|

|

|

|

|

|

|

|

|||

|

Q806 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

11. ILL(SMALL) |

DET |

|

|

IC19 REG. |

P7.5V |

TH |

|

|

|

|

MICROPROCESSOR |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

6. CAN-H |

|

|

|

|

|

|

BU5V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5. CAN-L |

|

|

|

|

|

IC17 |

|

|

|

|

|

SWTCH UNIT |

|

|

|

|

|

|

|

||||

16. PTT |

|

Q806, |

|

|

IE BUS |

CONTROL/DATA |

|

|

|

|

|

|

|

|

|

|

|

||||||

1. GND |

|

|

|

|

|

|

|

|

(X16- ) |

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

TOUCH |

|

|

|

|

|

||||||||

|

810 |

|

|

TX |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

3. GND |

|

CAN IC18 |

|

IC16 |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

15. GND |

|

ILL-V |

|

|

|

|

ILL-V |

|

|

|

|

PANEL |

|

|

|

|

|

||||||

|

|

TX |

|

|

BUFFER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

ILL-V |

|

P5V |

|

|

|

|

|

|

I2C BUS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

J800 (C/3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RCA |

|

|

|

Q43 |

|

|

|

|

|

IC3 RST |

|

|

|

|

|

|

|

|

|

|

|

|

|

1. AUX-V-IN2 |

|

|

|

PTT-DET |

|

|

|

|

|

IC7 |

|

|

|

|

|

|

|

|

|

|

|

||

2. AUX-DET |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

3. GND |

|

|

|

Q5 |

|

|

|

|

|

|

|

EEPROM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

J806 (C/3) |

|

|

|

ILL |

|

|

|

|

|

|

|

8kB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

REAR |

|

|

|

PWM DET. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAMERA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1. REAR-V-IN3 |

|

|

|

Q62 |

|

|

|

|

|

CPU2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

2. GND |

|

|

|

REAR-SW |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

3. GUIDE |

|

|

|

|

|

|

|

CAN |

|

I2C BUS |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

MICRO- |

|

|

|

|

|

|

|

|

|

|

|

|

|

4. REAR-DET |

|

|

|

|

|

|

|

|

|

PROCESSOR |

IC4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IC15 |

|

|

AUDIO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BUFFER |

|

|

MIX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10MHz |

|

|

IC6 |

|

|

|

|

|

|

|

|

|

|

|

J803 (C/3) |

|

|

|

|

|

|

|

|

|

|

E-VOL |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

CLK |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

VIDEO UNIT |

|

|

|

|

|

|||||

17-36PIN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

AUDIO BUS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(X35- ) |

|

|

|

|

|

|

||

20. F-BUS+ |

|

|

|

|

|

|

|

|

V SYNC SW |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

22. F-BUS- |

|

|

|

|

|

|

|

|

|

|

|

|

|

EEPROM |

|

|

|

|

|

||||

19. GND |

|

|

|

|

|

|

|

|

|

IC200 |

IC201 |

|

|

|

|

|

|

|

|

||||

21. GND |

|

|

|

|

|

|

|

|

|

|

|

|

1kB |

|

|

|

|

|

|

||||

23. RESET |

|

|

|

|

|

|

|

|

|

VIDEO |

|

SYNC |

|

|

|

|

|

|

|

|

|

|

|

24. AUDIO-MUTE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

SW |

|

SW |

|

|

RGB |

|

|

|

|

|

|

|

||

26. BUS ON |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

17. BUS OFF |

|

|

|

Q65 |

Q22 |

|

|

|

|

|

|

|

IC203 |

|

|

|

IC102 |

|

|

|

|

||

18. +B |

|

|

|

|

|

|

P7.5V |

REG. |

P5V |

|

|

|

|

|

|

|

|

||||||

34. A-OUT(L) |

|

|

|

SW |

MUTE |

|

|

|

CHROMA |

|

HD |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

TIMING |

|

|

|

||||||||||

|

|

|

|

Q60 |

Q21 |

|

|

|

|

REG. |

P3V |

|

DECODER & |

|

VD |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

RGB |

|

|

CONTROLLER |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

32. A-OUT(R) |

|

|

|

SW |

MUTE |

|

|

|

|

|

|

COMPENSATION |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

Q45, |

|

|

|

+B |

SW |

B/L INV |

VFL H |

|

R |

G B |

|

|

|

|

|

|

|

|

||

|

|

|

|

52 |

|

|

|

VFL L |

|

|

|

|

|

|

|

|

|

||||||

33. A-GND |

|

|

|

SW |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

35. NAVI-GND |

|

|

|

|

Q17 |

|

|

IC13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MONO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

36. NAVI-AUDIO |

|

|

|

MUTE |

|

|

SW-OP |

|

|

|

P18.5V |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

J802 (C/3) |

|

|

|

|

|

|

|

|

|

|

|

P-15.5V |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

P5V |

|

TFT LCD ASSY |

|

|

|

|

|

|||||

TV TUNER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

VFL H |

|

|

|

|

|

|

||||||

UNIT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

VFL L |

|

|

|

|

|

|

|

|

|

|

||

8. TV-V-IN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

10-15. TU 5L |

|

IC801 |

|

IC14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

18. TV-AUDIO-L |

L/R |

L |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

ISOLATION |

TV-AUDIO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

20. TV-AUDIO-R |

AUDIO-GND |

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

19. TV-A-GND |

+B |

|

AMP |

|

|

BUFFER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.2. TU+B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3-8. GND |

|

|

P7.5V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

J805 (B/3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NAVIGATION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UNIT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10. NAVI-RX |

|

|

P7.5V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11. NAVI-TX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

IC800 |

|

|

|

IC10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

8. NAVI-A-R |

L/R |

|

L |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

ISOLATION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

12. NAVI-A-L |

AUDIO-GND |

|

R |

|

MIX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

7. NAVI-A-GND |

AMP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

1. NAVI-R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5. NAVI-G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9. NAVI-B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13. C-SYNC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2.6. GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2

FGZ201ELF2/ERF2

COMPONENTS DESCRIPTION

● Synthesizer unit (X14-9122-71)

Ref. No. |

Component Name |

Application / Function / Operation / Condition |

|

|

|

|

|

IC1 |

S-80943CNMC |

Reset IC (when resets at the time of backup power supply is OFF) |

|

|

|

|

|

IC2 |

TC7WHU04FU |

Inverter IC (audio unit control and microprocessor program writing) |

|

|

|

|

|

IC3 |

M306NBFCTFP5Q0 |

CAN microprocessor (control of a setup and ADA voice synthesis of the connection existence distinction |

|

quality of image of a communication rear camera and an AUX terminal with a car unit and TV tuner) |

|||

|

|

||

|

|

|

|

|

|

System microprocessor (surveillance of communication internal electrical power source control and a |

|

IC5 |

M30624FGAFP9P3 |

power supply with the setting audio unit and NAVI unit of the control video sauce, the screen zoom, and |

|

the brightness of the control and the graphic microprocessor of a CAN microprocessor, and the abnor- |

|||

|

|

||

|

|

malities in temperature) |

|

|

|

|

|

IC7 |

S-24CS08AFJ-TB |

EEP-ROM (memory of a receiving TV station name and touch-panel compensation data for memory) |

|

|

|

|

|

IC8 |

TJA1054 |

CAN transceiver (communication with a car unit) |

|

|

|

|

|

IC9 |

S-80943CNMC |

Reset IC (detection of the 5V power supply ) |

|

|

|

|

|

IC10 |

NJM4565MD |

OP AMP IC (LR sound MIX of NAVI audio and bias of power supply an internal audio circuit) |

|

|

|

|

|

IC12 |

TC4066BFT(N) |

Analog SW (port SW at the time of microprocessor program writing) |

|

|

|

|

|

IC13 |

NJM2120M |

OP AMP with SW (change of a NAVI sound and an ADA sound) |

|

|

|

|

|

IC16 |

TC7WH126FU |

Buffer IC (the microprocessor is protected from a communication line with a NAVI unit) |

|

|

|

|

|

IC17 |

HA12187FP |

BUS transceiver (communication with an audio unit) |

|

|

|

|

|

IC18 |

S-816A50AMC-T2 |

Regulator IC (5V power supply of a system microprocessor) |

|

|

|

|

|

IC19 |

BA00ASFP |

Regulator IC (analog system 7.5V power supply) |

|

|

|

|

|

IC20 |

BA9743AFV |

DC/DC controller IC (power supply of without system microprocessor and key illumination circuit) |

|

|

|

|

|

IC21 |

S-80925CNMC |

Reset IC (it resets at the time of the abnormal of function for system microprocessor) |

|

|

|

|

|

IC800 |

TDA8579T-T |

Isolation AMP (noise removal of a NAVI audio sound) |

|

|

|

|

|

Q1 |

DTA124EUA |

Audio MUTE SW |

|

|

|

|

|

Q2 |

DTA124EUA |

|

|

|

|

|

|

Q32,37 |

2SC4081 |

|

|

|

|

|

|

Q34 |

2SA1576A |

DC/DC controller power supply |

|

|

|

||

Q35,53 |

DTC144EUA |

||

|

|||

|

|

|

|

Q36,39,41 |

DTA144EUA |

|

|

|

|

|

|

Q46 |

2SB1188(Q,R) |

|

|

|

|

|

|

Q4 |

DTC144EUA |

Microprocessor reset SW (at the time of power-supply ON/OFF is ON : CAN microprocessor is reset mode) |

|

|

|

|

|

Q5 |

DTC124EUA |

Key illumination tone light detection (it turns on at the time of a illumination PWM input) |

|

|

|

|

|

Q6 |

DTA124EUA |

Temperature detection SW (at the time of ACC → ON is ON : temperature detection mode start) |

|

|

|

|

|

Q7~11, |

DTC124EUA |

Video setup SW (it is ON/OFF by screen mode and adjustment) |

|

Q55,56,58 |

|||

|

|

||

|

|

|

|

Q12,16 |

DTC144EUA |

Audio control SW (at the time of the audio communication is ON : Q16 is ON, at the time of OFF : Q15 is |

|

|

|

|

|

Q15,18 |

DTA144EUA |

ON) |

|

|

|

|

|

Q17 |

2SD2114K |

Audio MUTE (at the time of power supply ON/OFF MUTE is ON) |

|

|

|

||

Q50 |

DTA124EUA |

||

|

|||

|

|

|

3

FGZ201ELF2/ERF2

COMPONENTS DESCRIPTION

Ref. No. |

Component Name |

Application / Function / Operation / Condition |

||

|

|

|

|

|

Q19 |

2SB1188(Q,R) |

Microprocessor power supply SW (at the time of CAN microprocessor program writing is OFF) |

||

|

|

|||

Q25 |

DTC124EUA |

|||

|

|

|||

|

|

|

||

Q20 |

2SC4081 |

Audio SW (at the time of ADA audio out is ON) |

||

|

|

|

||

Q24 |

2SC4081 |

Power supply voltage dropout detection (when turns off at the time of backup power supply voltage dropout) |

||

|

|

|

|

|

Q26 |

DTC124EUA |

Voltage detection (at the time of Q26 : ON backup power supply voltage detection) |

||

|

|

|||

Q28 |

2SA1576A |

|||

|

|

|||

|

|

|

|

|

Q29 |

2SC4081 |

|

|

|

|

|

|

||

Q30 |

2SB1203-FA |

Constant voltage power supply (backup 5V power regulator) |

||

|

|

|

|

|

Q64 |

2SA1576A |

|

|

|

|

|

|

|

|

Q31 |

FMY6 |

|

|

|

|

|

|

||

Q57 |

2SA1576A |

Constant voltage power supply (at the time of Q61 is ON : +18.5V output) |

||

|

|

|

|

|

Q61 |

DTC144EUA |

|

|

|

|

|

|

||

Q33 |

2SA1576A |

Over-current detection (at the time of 18.5V over-current detection the controller power supply is OFF) |

||

|

|

|

||

Q38 |

IMT1A |

Over-current detection (at the time of 8.5V over-current detection the controller power supply is OFF) |

||

|

|

|

|

|

Q40 |

FMY6 |

DC/DC switching (primary side switching of a transformer) |

||

|

|

|||

Q42 |

2SJ327Z |

|||

|

|

|||

|

|

|

|

|

Q43 |

FMY6 |

DC/DC switching (switching of 5V power supply) |

||

|

|

|||

Q49 |

2SJ327Z |

|||

|

|

|||

|

|

|

||

Q44 |

2SC4081 |

Over-current detection (at the time of -15.5V over-current detection the controller power supply is OFF) |

||

|

|

|

||

Q47 |

FMY6 |

Constant voltage power supply (-15.5V constant voltage power supply) |

||

|

|

|

||

Q48 |

IMT1A |

Over-current detection (at the time of 5V over-current detection the controller power supply is OFF) |

||

|

|

|

|

|

Q66,67 |

DTA144EUA |

Timer (at the time of a system microprocessor reckless run Q67 is OFF) |

||

|

|

|||

Q68,69 |

DTC144EUA |

|||

|

|

|||

|

|

|

|

|

Q700,701 |

2SC4081 |

Audio connection detection (at the time of audio connection Q700 is ON) |

||

|

|

|||

Q702 |

DTA124EUA |

|||

|

|

|||

|

|

|

||

Q800 |

DTA124EUA |

PARKING detection (at the time of car PARKING is ON) |

||

|

|

|

||

Q801 |

DTA124EUA |

Speed detection (at the time of a speed pulse input is ON) |

||

|

|

|

||

Q802 |

DTC124EUA |

Reset input (at the time of Q802 ON when system microprocessor is reset mode) |

||

|

|

|

|

|

Q803 |

2SC4081 |

ACC detection (at the time of car ACC → |

ON : ON) |

|

|

|

|

|

|

Q804 |

2SC4081 |

IGN detection (at the time of car Ignition → |

ON : ON) |

|

|

|

|

||

Q805 |

2SC4081 |

Reverse detection (at the time of car reverse : ON) |

||

|

|

|

||

Q806 |

2SC4081 |

SMALL detection (at the time of car SMALL → ON : ON) |

||

|

|

|

|

|

Q807,809 |

DTA124EUA |

Key illumination tone light power supply regulator (it is illumination VCC (7V) with the duty cycle according |

||

|

|

|||

Q808,811 |

2SC4081 |

|||

to PWM output) |

|

|||

|

|

|

||

Q810 |

2SB1203-FA |

|

||

|

|

|||

|

|

|

|

|

4

FGZ201ELF2/ERF2

COMPONENTS DESCRIPTION

● Electric unit (X25-9412-71)

Ref. No. |

Component Name |

Application / Function / Operation / Condition |

|

|

|

|

|

IC2 |

TC9246F |

PLL Oscillator IC |

|

|

|

|

|

IC3 |

TC7SHU04F |

Inverter (DOT CLOCK) |

|

|

|

|

|

IC4 |

HD64412FI |

Graphic control IC |

|

|

|

|

|

IC5 |

MSM5118165FP60 |

The memory for graphic control IC |

|

|

|

|

|

IC6 |

BU3616K |

Video D/A converter |

|

|

|

|

|

IC7 |

TC7SHU04F |

Inverter (DACK SIGNAL) |

|

|

|

|

|

IC10 |

TC7SH32FU |

OR gate IC |

|

|

|

|

|

IC11 |

MSM5118165FP60 |

The memory for graphic microprocessors |

|

|

|

|

|

IC12 |

HD6437041AG57E |

Graphic microprocessor |

|

|

|

|

|

IC19 |

MBM29F160TE9P6 |

Graphic bitmap data & program data memory |

|

|

|

|

|

IC20 |

TC7SHU04F |

Inverter (SYNC. SIGNAL) |

|

|

|

|

|

IC22 |

TC7SHU04F |

Inverter |

|

|

|

|

|

IC23 |

TC7SET08FU |

AND gate |

|

|

|

|

|

IC24 |

MSM5258MS-K |

Synchronized signal generator |

|

|

|

|

|

IC26 |

TA78DS05F |

5V AVR |

|

|

|

|

|

IC27,28 |

TC7SHU04F |

Inverter (SYNC. SIGNAL) |

|

|

|

|

|

Q2,3 |

DTC124EUA |

The transistor for touch-panel detection |

|

|

|

||

Q4,5 |

DTA124EUA |

||

|

|||

|

|

|

● Video unit (X35-4250-00)

Ref. No. |

Component Name |

Application / Function / Operation / Condition |

|

|

|

|

|

IC31 |

TL5001ID |

Switching regulator (for back light 7.5V power supply) |

|

|

|

|

|

IC101 |

NJM2107F |

Operational amplifier (oscillating circuit : low path output) |

|

|

|

|

|

IC102 |

TC160G11AF1146 |

Timing controller (LCD driver IC) |

|

|

|

|

|

IC200,201 |

NJM2535V |

Video switch (input video signal change) |

|

|

|

|

|

IC202 |

NJW1303V |

Synchronous separation |

|

|

|

|

|

IC203 |

AN2546FH-A |

Chrome decoder, gamma correction (an input video signal conversion to LCD drive signal) |

|

|

|

|

|

IC205 |

S-24C01B |

EEP-ROM (I2C memory backup) |

|

|

|

|

|

IC207 |

NJM4580V |

Operational amplifier (V-COM buffer) |

|

|

|

|

|

IC209 |

TC7W34FU |

Buffer containing 3 circuits (synchronized signal output buffer) |

|

|

|

|

|

IC211 |

NJU7222U30 |

3V Regulator |

|

|

|

|

|

IC212 |

NJU7223DL1-50 |

5V Regulator |

|

|

|

|

|

IC217 |

TC7S14F |

Inverter (for side black reverse signal ) |

|

|

|

|

|

Q1 |

2SC4081 |

ACC ON/OFF SW (for back light power supply) |

|

|

|

|

|

Q2 |

2SB1203-FA |

+B SW (for back light power supply) |

|

|

|

|

|

Q3 |

DTA124EUA |

ACC ON/OFF SW (for back light power supply) |

|

|

|

||

Q4 |

DTC124EUA |

||

|

|||

|

|

|

5

FGZ201ELF2/ERF2

COMPONENTS DESCRIPTION

Ref. No. |

Component Name |

Application / Function / Operation / Condition |

|

|

|

Q31 |

2SC4081 |

SW REG Output (FET drive) |

|

|

|

Q32 |

2SA1576A |

SW REG Output (FET drive) |

|

|

|

Q33 |

2SJ327Z |

DC/DC converter SW (for back light power supply) |

|

|

|

Q35,36 |

2SD1803 |

Inverter oscillation change SW |

|

|

|

Q37 |

2SD1803 |

Back light tone light (for PWM pules drive) |

|

|

|

Q38 |

DTA124EUA |

Back light tone light (for PWM pules drive) |

|

|

|

Q39 |

DTC124EUA |

Back light tone light (for PWM pules drive) |

|

|

|

Q40 |

2SA1576A |

Transistor for over-current protection (back light power supply) |

|

|

|

Q41 |

2SC4081 |

An over-current for over voltage protection (back light power supply) |

|

|

|

Q42 |

2SJ327Z |

FET for the back light lighting SW |

|

|

|

Q43 |

DTC124EUA |

The transistor for the back light lighting SW |

|

|

|

Q101 |

2SC2411K |

Transistor for oscillating circuits (a timing controller for a standard oscillation) |

|

|

|

Q102 |

DTC124EUA |

LCD reverse signal control (LCD up-and-down side reverse control transistor) |

|

|

|

Q203 |

2SC4097 |

V-COM buffer |

|

|

|

Q204 |

2SA1577 |

V-COM buffer |

|

|

|

Q205 |

2SC4081 |

Video signal buffer |

|

|

|

Q206 |

2SA1576A |

Video signal buffer |

|

|

|

Q209,210 |

DTC124EUA |

Synchronized signal muting (timing controller : at the time of adjustment muting) |

|

|

|

X200 |

L78-0549-05 |

Synchronous separation reference oscillator (15.734kHz) |

|

|

|

X201 |

L77-2818-05 |

Color reference oscillator (3.58MHz) |

|

|

|

6

FGZ201ELF2/ERF2

MICROCOMPUTER’S TERMINAL DESCRIPTION

● System microprocessor : M30624FGAFP9P3 (X14-9122-71 : IC5)

Pin No. |

|

|

|

Pin Name |

I/O |

Purpose / Description / Processing / Operation |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

C-SYSDATA |

O |

System microprocessor data output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

CANCLK |

O |

System microprocessor clock output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

SPD |

I |

Speed pulse input |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

PON2 |

O |

PON7.5V control output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

PON3 |

O |

PON18.5V control output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

WDP |

O |

Watch dog pulse output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

PTT |

O |

The PTT output for a telephone |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

BYTE |

- |

Un-connecting |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

CNVSS |

- |

It is high at the time of rewriting |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

10 |

XCIN |

I |

Sub clock input |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

XCOUT |

O |

Sub clock output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

RESET |

I |

Reset input |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

XOUT |

O |

Clock output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

VSS |

- |

Ground |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

XIN |

I |

Clock input |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

16 |

VCC |

- |

Power supply |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

17 |

NMI |

I |

Interruption input |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

18 |

CANREQ |

I |

System microprocessor Request-to-Send input |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

NC |

- |

Un-connecting |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

20 |

CANCON |

O |

CAN microprocessor control output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

21 |

AUDIO-BUS+ |

I |

AUDIO BUS communication end detection input |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

22 |

BUS_ON_REQ |

I |

AUDIO BUS ON detection input |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

23 |

BUS_OFF_REQ |

I |

AUDIO BUS OFF detection input |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

24 |

BRIGHT |

O |

BRIGHT control output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

25~27 |

NC |

- |

Un-connecting |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

28 |

STB |

O |

AUDIO BUS communication standby output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

29 |

SI |

I |

AUDIO BUS communication data reception input |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

30 |

SO |

O |

AUDIO BUS communication data transmitting output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

NAVI-TXD |

O |

Usually, a NAVI communication transmitting data output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

NAVI-RXD |

I |

It is NAVI communication receiving data input at the time of usual |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

BUS_SYS_ON |

O |

It is an AUDIO BUS system-on output at the time of usual |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

34 |

BUS_SYS_OFF |

O |

AUDIO BUS system-off output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

35 |

SYSDATA |

O |

System microprocessor data output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

SHDATA |

I |

System microprocessor data input |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

SHCLK |

O |

System microprocessor clock output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

38 |

SHRST |

O |

Graphic microprocessor reset output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

39 |

SHINI |

O |

Graphic microprocessor initial output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

40 |

SHRDY |

I |

The notice input of a state which can be graphic communicated |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

41 |

EPM |

I |

Flash write-in EPM input |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

7

FGZ201ELF2/ERF2

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. |

|

|

|

Pin Name |

I/O |

Purpose / Description / Processing / Operation |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

42 |

|

SHCON |

O |

Graphic microprocessor standby control output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

43 |

|

SHSTBY |

I |

The completion input of graphic microprocessor standby shift |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

44 |

|

SYSCS |

O |

System microprocessor Request-to-Send output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

45 |

|

SH_VMUTE |

I |

Graphic microprocessor image muting demand input |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

46 |

|

CE |

I |

Flash write-in CE input |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

47 |

|

TOUCH_EN |

O |

Graphic microprocessor touch key analysis permission output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

|

TOUCH |

I |

Notice input of graphic microprocessor touch key-on |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

49 |

|

PLLCE |

O |

The clock generating IC mode output for Q2i |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

50 |

|

PLLSDA |

O |

The clock generating IC data output for Q2i |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

51 |

|

PLLSCK |

O |

The clock generating IC clock output for Q2i |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

52 |

|

BL-ON |

O |

Back light switch output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

53 |

|

VIDEO Swa |

O |

TV/REAR changeover switch output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

54 |

|

NC |

- |

Un-connecting |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

55 |

|

VIDEO SWb |

O |

DVD changeover switch output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

56 |

|

SYNC Swa |

O |

VIDEO/NAVI SYUn-connecting changeover switch output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

57 |

|

SYNC SWb |

O |

GRAPHICS SYUn-connecting changeover switch output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

58 |

|

VIDEO SWc |

O |

DVD-CH/NAVI-AUX changeover switch output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

59 |

|

VIDEO SWd |

O |

AUX changeover switch output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

60 |

|

HPOSI1 |

O |

Level position adjusted power |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

61 |

|

HPOSI2 |

O |

Level position adjusted power |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

62 |

|

VCC |

- |

Power supply |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

63 |

|

SCAN1 |

O |

Screen mode changeover switch output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

64 |

|

VSS |

- |

Ground |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

65 |

|

SCAN2 |

O |

Screen mode changeover switch output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

66 |

|

NTSC/PAL |

O |

NTSC/PAL changeover switch output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

67 |

|

VMUTE |

O |

Video muting control output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

68 |

|

+BDET SW |

O |

+B voltage detector circuit control output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

69 |

|

REV |

I |

Reverse detection input |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

70 |

|

PARKING |

I |

Parking detection input |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

71 |

|

P-ON |

O |

Power supply control output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

72 |

|

FAULT |

O |

FAULT display output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

73 |

|

ACC |

I |

ACC voltage detection input |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

74 |

|

BUDET |

I |

+B voltage variation detection input |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

75 |

|

SHCS |

I |

Graphic microprocessor Request-to-Send input |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

76 |

|

IGN |

I |

Ignition voltage detection input |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

77 |

|

ADA-INT |

O |

NAVI voice changeover switch output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

78 |

|

AUDIO-MUTE |

O |

AUDIO muting signal output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

79 |

|

TV |

O |

TV voice muting output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

80 |

|

MUTE1 |

O |

MUTE1 signal output |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

81 |

|

TYPE0 |

I |

It forces and is a setting input |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8

FGZ201ELF2/ERF2

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. |

|

|

|

Pin Name |

I/O |

Purpose / Description / Processing / Operation |

||||

|

|

|

|

|

|

|

|

|

|

|

82 |

TYPE1 |

I |

It forces and is a setting input |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

83 |

MUTE2 |

O |

MUTE2 signal output |

|||||||

|

|

|

|

|

|

|

|

|

|

|

84 |

E2PSCL |

O |

IIC clock output |

|||||||

|

|

|

|

|

|

|

|

|

|

|

85 |

E2PSDA |

O |

IIC data input and output |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

86 |

INH |

- |

Un-connecting. |

|||||||

|

|

|

|

|

|

|

|

|

|

|

87 |

HPOSI3 |

O |

Level position adjusted power |

|||||||

|

|

|

|

|

|

|

|

|

|

|

88 |

HPOSI4 |

O |

Level position adjusted power |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

89 |

AUDIODET |

I |

Audio voltage detection input |

|||||||

|

|

|

|

|

|

|

|

|

|

|

90 |

TEMPDET |

I |

High temperature temperature detection input |

|||||||

|

|

|

|

|

|

|

|

|

|

|

91 |

BLDET2 |

I |

Back light voltage detection input |

|||||||

|

|

|

|

|

|

|

|

|

|

|

92 |

BLDET |

I |

Back light voltage detection input |

|||||||

|

|

|

|

|

|

|

|

|

|

|

93 |

+BDET |

I |

+B voltage detection input |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

94 |

DC/DC DET |

I |

PON5V voltage detection input |

|||||||

|

|

|

|

|

|

|

|

|

|

|

95 |

CANRESET |

O |

CAN microprocessor reset output |

|||||||

|

|

|

|

|

|

|

|

|

|

|

96 |

AVSS |

I |

Analog grand input |

|||||||

|

|

|

|

|

|

|

|

|

|

|

97 |

C-SYSREQ |

O |

System microprocessor Request-to-Send output |

|||||||

|

|

|

|

|

|

|

|

|

|

|

98 |

VREF |

- |

Reference voltage |

|||||||

|

|

|

|

|

|

|

|

|

|

|

99 |

AVCC |

- |

Analog power supply |

|||||||

|

|

|

|

|

|

|

|

|

|

|

100 |

CANDATA |

I |

System microprocessor data input |

|||||||

|

|

|

|

|

|

|

|

|

|

|

● Graphic microprocessor : HD6437041AG57E (X25-9412-71 : IC12)

Pin No. |

Pin Name |

I/O |

Purpose / Description / Processing / Operation |

|

|

|

|

1~5 |

NC |

- |

Un-connecting |

|

|

|

|

6 |

VSS |

- |

Ground |

|

|

|

|

7~11 |

A0~A4 |

O |

Address bus output |

|

|

|

|

12 |

VCC |

- |

Power supply |

|

|

|

|

13 |

A5 |

O |

Address bus output |

|

|

|

|

14 |

VSS |

- |

Ground |

|

|

|

|

15~25 |

A6~A16 |

O |

Address bus output |

|

|

|

|

26 |

VCC |

- |

Power supply |

|

|

|

|

27 |

A17 |

O |

Address bus output |

|

|

|

|

28 |

VSS |

- |

Ground |

|

|

|

|

29, 30 |

NC |

- |

Un-connecting |

|

|

|

|

31 |

RAS |

O |

DRAM row address Strobe output |

|

|

|

|

32 |

CASL |

O |

DRAM low rank side column address Strobe output |

|

|

|

|

33 |

NC |

- |

Un-connecting |

|

|

|

|

34 |

CASH |

O |

DRAM higher rank side column address Strobe output |

|

|

|

|

35 |

VSS |

- |

Ground |

|

|

|

|

36 |

RDWR |

O |

DRAM write-in Strobe output |

|

|

|

|

9

FGZ201ELF2/ERF2

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. |

Pin Name |

I/O |

Purpose / Description / Processing / Operation |

|

|

|

|

37~39 |

A18~A20 |

O |

Address bus output |

|

|

|

|

40 |

VCC |

- |

Power supply |

|

|

|

|

41 |

A21 |

O |

Address bus output |

|

|

|

|

42 |

VSS |

- |

Ground |

|

|

|

|

43 |

RD |

O |

External device read-out Strobe output |

|

|

|

|

44 |

NC |

- |

Un-connecting |

|

|

|

|

45 |

SH_VMUTE |

O |

Graphic microprocessor video mute request output |

|

|

|

|

46 |

NC |

- |

Un-connecting |

|

|

|

|

47 |

WRH |

O |

An external device higher rank side write-in output |

|

|

|

|

48 |

WRL |

O |

An external device low rank side write-in output |

|

|

|

|

49 |

CS1 |

O |

Chip selection output (inside register of Q2i) |

|

|

|

|

50 |

CS0 |

O |

Chip selection output (flash ROM) |

|

|

|

|

51~53 |

NC |

- |

Un-connecting |

|

|

|

|

54 |

CS2 |

O |

Chip selection output (Q2iUGM) |

|

|

|

|

55 |

VSS |

- |

Ground |

|

|

|

|

56 |

ROM_RESET |

O |

Flash ROM reset output |

|

|

|

|

57 |

ROM_RY/BY |

I |

Flash ROM lady busy input |

|

|

|

|

58 |

NC |

- |

Un-connecting. |

|

|

|

|

59 |

DACK |

O |

Q2iDMA transmission Strobe output |

|

|

|

|

60 |

NC |

- |

Un-connecting. |

|

|

|

|

61 |

VSS |

- |

Grand input |

|

|

|

|

62 |

DREQ |

I |

Q2iDMA transmission demand input |

|

|

|

|

63 |

VCC |

- |

Power supply |

|

|

|

|

64~68 |

NC |

- |

Un-connecting. |

|

|

|

|

69 |

SYSCS |

I |

Graphic microprocessor Request-to-Send input |

|

|

|

|

70 |

IRL |

I |

Q2i interrupt request input |

|

|

|

|

71 |

VSS |

- |

Ground |

|

|

|

|

72 |

SHCON |

I |

Graphic microprocessor standby control input |

|

|

|

|

73~76 |

D12~D15 |

I/O |

Data bus input and output |

|

|

|

|

77 |

VCC |

- |

Power supply |

|

|

|

|

78 |

D11 |

I/O |

Data bus input and output |

|

|

|

|

79 |

VSS |

- |

Ground |

|

|

|

|

80~84 |

D6~D10 |

I/O |

Data bus input and output |

|

|

|

|

85 |

VCC |

- |

Power supply |

|

|

|

|

86 |

D5 |

I/O |

Data bus input and output |

|

|

|

|

87 |

VSS |

- |

Ground |

|

|

|

|

88~92 |

D0~D4 |

I/O |

Data bus input and output |

|

|

|

|

93 |

VSS |

- |

Ground |

|

|

|

|

94 |

XTAL |

I |

Crystal oscillator input |

|

|

|

|

95 |

MD3 |

I |

Mode setting input of operation |

|

|

|

|

10

FGZ201ELF2/ERF2

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin No. |

Pin Name |

I/O |

Purpose / Description / Processing / Operation |

|

|

|

|

96 |

EXTAL |

I |

Crystal oscillator input |

|

|

|

|

97 |

MD2 |

I |

Mode setting input of operation |

|

|

|

|

98 |

NMI |

I |

Non maskable interrupt input |

|

|

|

|

99 |

VCC |

- |

Power supply |

|

|

|

|

100 |

NC |

- |

Un-connecting |

|

|

|

|

101 |

WAIT |

I |

Q2i wait cycle insertion input |

|

|

|

|

102 |

MD1 |

I |

Mode setting input of operation |

|

|

|

|

103 |

MD0 |

I |

Mode setting input of operation |

|

|

|

|

104 |

PLLVCC |

I |

The power supply input for built-in PLL |

|

|

|

|

105 |

PLLCAP |

I |

The capacity input for built-in PLL |

|

|

|

|

106 |

PLLVSS |

I |

The grand input for built-in PLL |

|

|

|

|

107 |

NC |

- |

Un-connecting |

|

|

|

|

108 |

SHRST |

I |

Reset input |

|

|

|

|

109~111 |

NC |

- |

Un-connecting |

|

|

|

|

112 |

VCC |

- |

Power supply |

|

|

|

|

113 |

Y- |

O |

The switching output for a touch-panel input |

|

|

|

|

114 |

X- |

O |

The switching output for a touch-panel input |

|

|

|

|

115 |

Y+ |

O |

The switching output for a touch-panel input |

|

|

|

|

116 |

X+ |

O |

The switching output for a touch-panel input |

|

|

|

|

117 |

VSS |

- |

Ground |

|

|

|

|

118 |

KEYDATA1 |

I |

Touch-panel data input (Y) |

|

|

|

|

119 |

KEYDATA2 |

I |

Touch-panel data input (X) |

|

|

|

|

120 |

NC |

- |

Un-connecting. |

|

|

|

|

121 |

KEY5 |

I |

Key switch input |

|

|

|

|

122 |

KEY4 |

I |

Key switch input |

|

|

|

|

123 |

KEY3 |

I |

Key switch input |

|

|

|

|

124 |

AVSS |

- |

Analog ground |

|

|

|

|

125 |

KEY2 |

I |

Key switch input |

|

|

|

|

126 |

KEY1 |

I |

Key switch input |

|

|

|

|

127 |

VREF |

- |

Reference voltage |

|

|

|

|

128 |

AVCC |

- |

Analog power supply |

|

|

|

|

129 |

VSS |

- |

Ground |

|

|

|

|

130 |

SYSDATA |

I |

Graphic microprocessor data input |

|

|

|

|

131 |

SHDATA |

O |

Graphic microprocessor data output |

|

|

|

|

132 |

SYSCLK |

I |

Graphic microprocessor clock input |

|

|

|

|

133 |

ROM_RXD |

I |

Flash ROM write-in data input |

|

|

|

|

134 |

ROM_TXD |

O |

Flash ROM write-in data output |

|

|

|

|

135 |

VCC |

- |

Power supply |

|

|

|

|

136 |

SHSTBY |

O |

The completion output of graphic microprocessor standby shift |

|

|

|

|

137 |

TOUCH |

O |

Notice output of graphic microprocessor touch key-on |