Kenwood DVF-3060-S Service manual

DVD/VCD/CD PLAYER

70%

76

0

POWER

ON OFF

4¢

1¡

DVF-3060/3060-S

DVF-3060K-S

SERVICE MANUAL

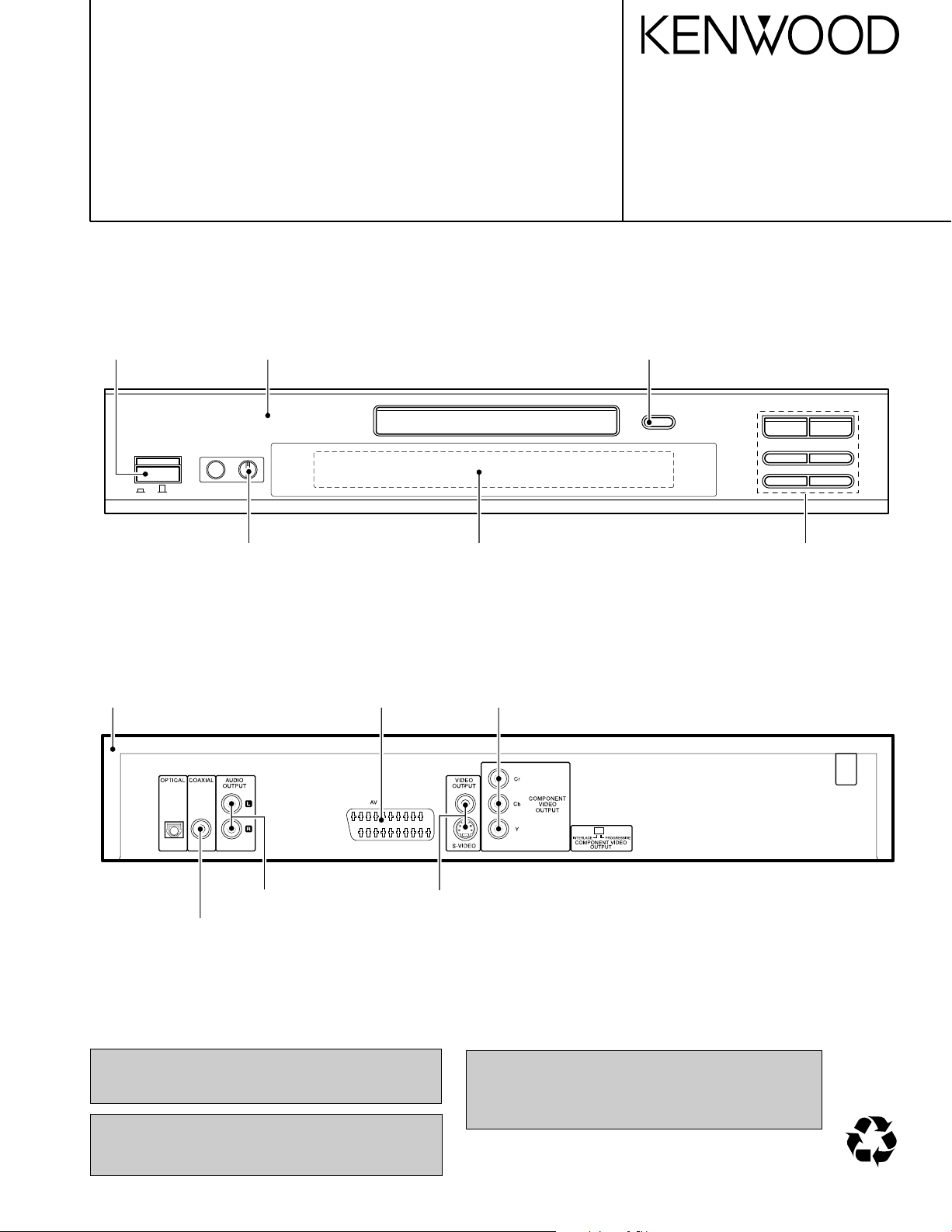

Knob(POWER) *

(K29-)

Front panel *

(A60-)

Knob(LEVEL)

(K29-8225-08)

Window display *

(B10-)

© 2002-4 PRINTED IN KOREA

B51-5789-00 (K/K) 2007

OPEN/CLOSE *

(K29-)

Knob *

(K29-)

Top cover *

(A09-)

Connection phono socket

(E63-1286-08)

Connection phono socket

(E63-1244-08)

In compliance with Federal Regulations, following are reproduction of labels on, or inside the product relating to laser

product safety.

Caution : No connection of ground line if disassemble

the unit. Please connect the ground line on

rear panel, PCBs, Chassis and some others.

Connection scart dual

(E40-8779-08)

Connection phono socket *

(E63-)

Connection din socket

(E63-1243-08)

KENWOOD-Corp. certifies this equipment conforms to DHHS

Regulations No.21 CFR 1040. 10, Chapter 1, subchapter J.

DANGER : Laser radiation when open and interlock defeated.

AVOID DIRECT EXPOSURE TO BEAM.

* Refer to parts list on page 16.

Figure is DVF-3060K.

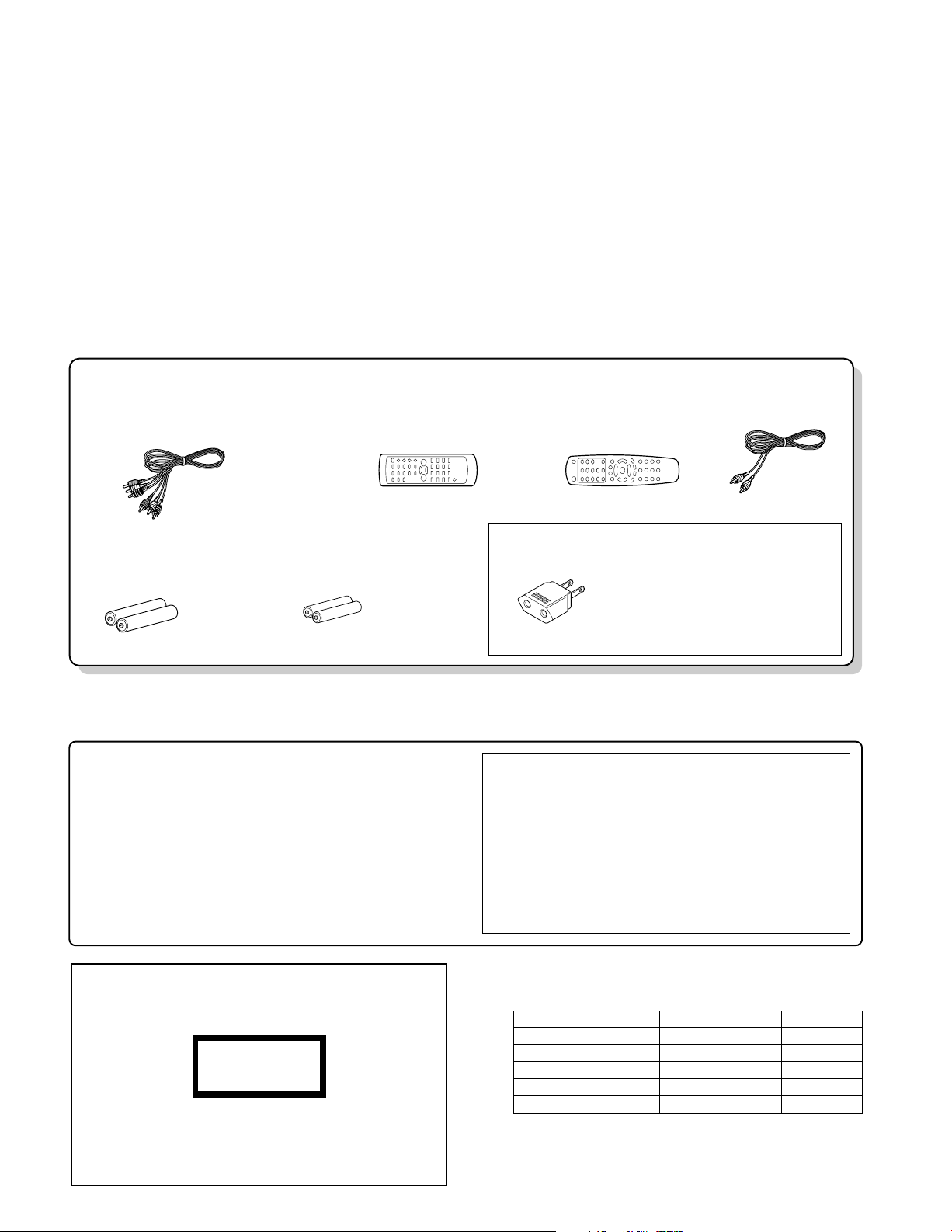

Please confirm that the following accessories are present.

Audio video cord (Red, White, Yellow) ...(1)

(E30-2990-08)

Batteries ...............................(2)

Remote control unit .........(1)

Coaxial cable ...(1)

(E30-7235-08)

DV-603/DVF-3060 (R6/AA)

DVF-3060K

(R03/AAA)

DVF-3060K

(A70-1592-08)

AC Plug Adaptor (1)

(E03-0115-05)

Use to adapt the plug on the

power cord to the shape of the

wall outlet.

(Accessory only for regions where

use is necessary.)

DV-603/DVF-3060

(A70-1532-08)

Operation to reset

÷ Please note that resetting the microprocessor clears the

contents stored in, it returns the microprocessor to the condition when it left the factory.

1 In Power ON condition, keep the 7 (Stop) key and the ¡

(Search) key pressed at the same time.

2 When both keys are pressed, the region code of the

unit, the software version, etc. will be displayed on

the display. (When nothing is done, the display of this

information continues.)

Example: 72. 14.02:05

3 Press the POWER ON/OFF switch to go to Power OFF.

4 When Power ON is performed with the

POWER ON/OFF

switch, the settings become the default factory settings.

The microprocessor may fall into malfunction (impossibility to operate erroneous display, etc.) when the

power cord is unplugged while power is ON or due to

an external factor. In this case, execute the following

procedure to reset the microprocessor and return it to

normal condition.

The marking of products using lasers

(For countries other than U.S.A., U.S.-Military and Canada)

The marking this product has been classified as Class 1. It

means that there is no danger of hazardous radiation outside

the product.

Location: Back panel

CLASS 1

LASER PRODUCT

DVF-3060/3060-S/3060K-S

CONTENTS / ACCESSORIES / CAUTIONS

Contents

CONTENTS / ACCESSORIES / CAUTIONS............. 2

DISASSEMBLY FOR REPAIR....................................3

CIRCUIT DESCRIPTION ............................................4

PC BOARD ................................................................ 9

Accessories

SCHEMATIC DIAGRAM .......................................... 13

EXPLODED VIEW ....................................................19

PARTS LIST..............................................................20

SPECIFICATIONS ....................................................25

Cautions

2

Model vs description

MODEL DESTINATION COLOR

DVF-3060 E BLACK

DVF-3060 Y BLACK

DVF-3060-S ETXY SILVER

DVF-3060K-S HM SILVER

DVF-3060K-S(M2) M2 SILVER

DVF-3060/3060-S/3060K-S

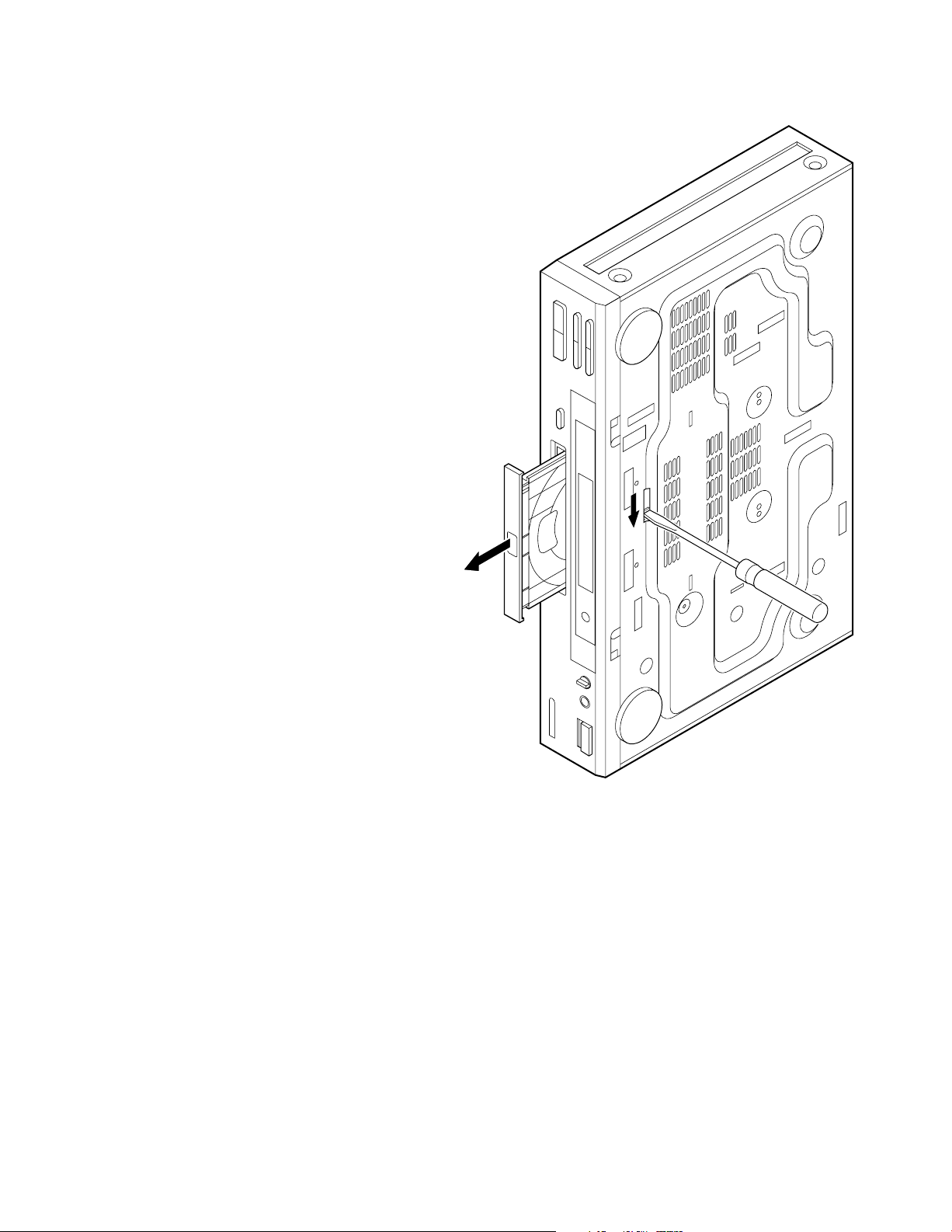

DISASSEMBLY FOR REPAIR

How to open the tray if it does not come out.

1. Insert a flat driver and pull it down in the drawing through the

hole on the loading chassis bottom.

2. Pull out the tray frontward by hand when it comes just out.

3

DVF-3060/3060-S/3060K-S

CIRCUIT DESCRIPTION

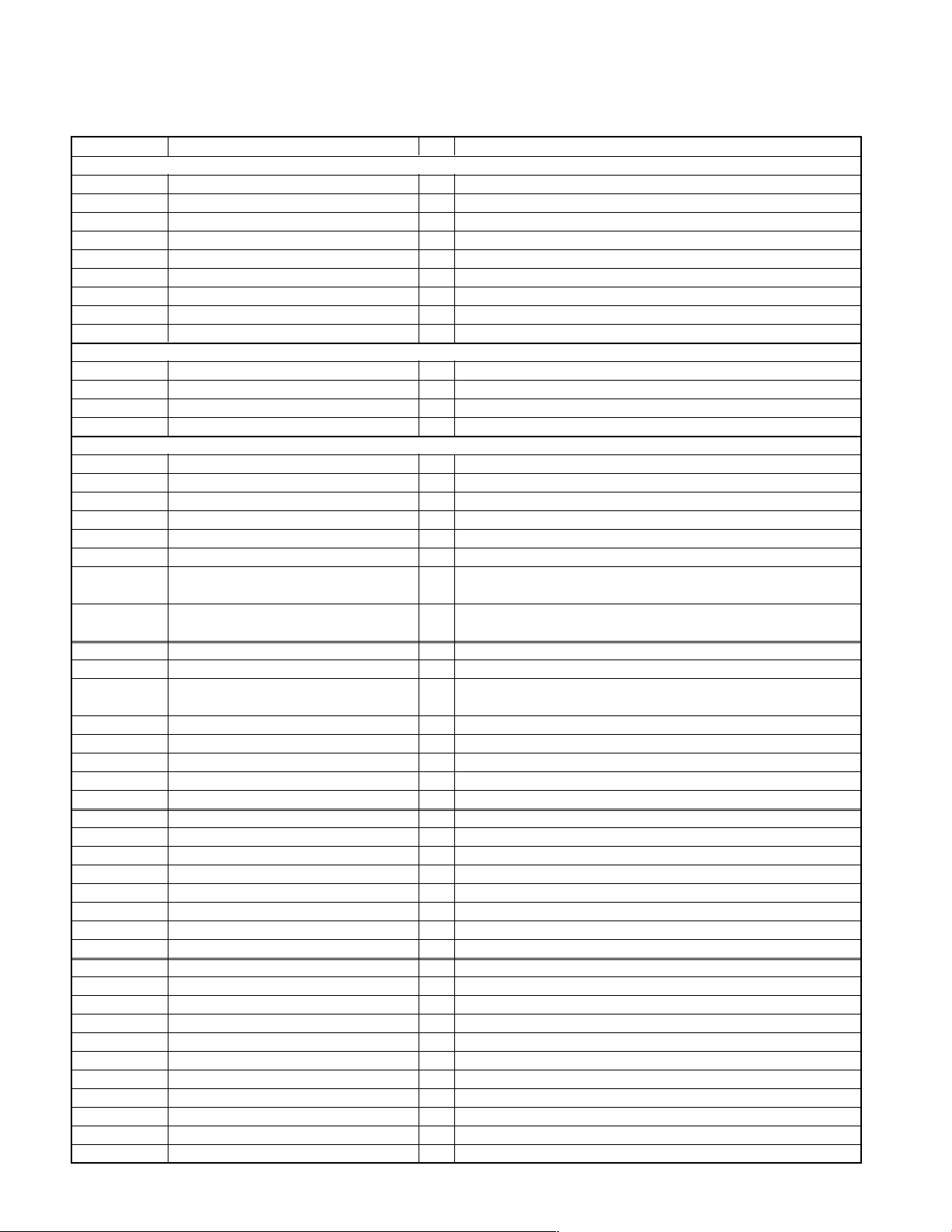

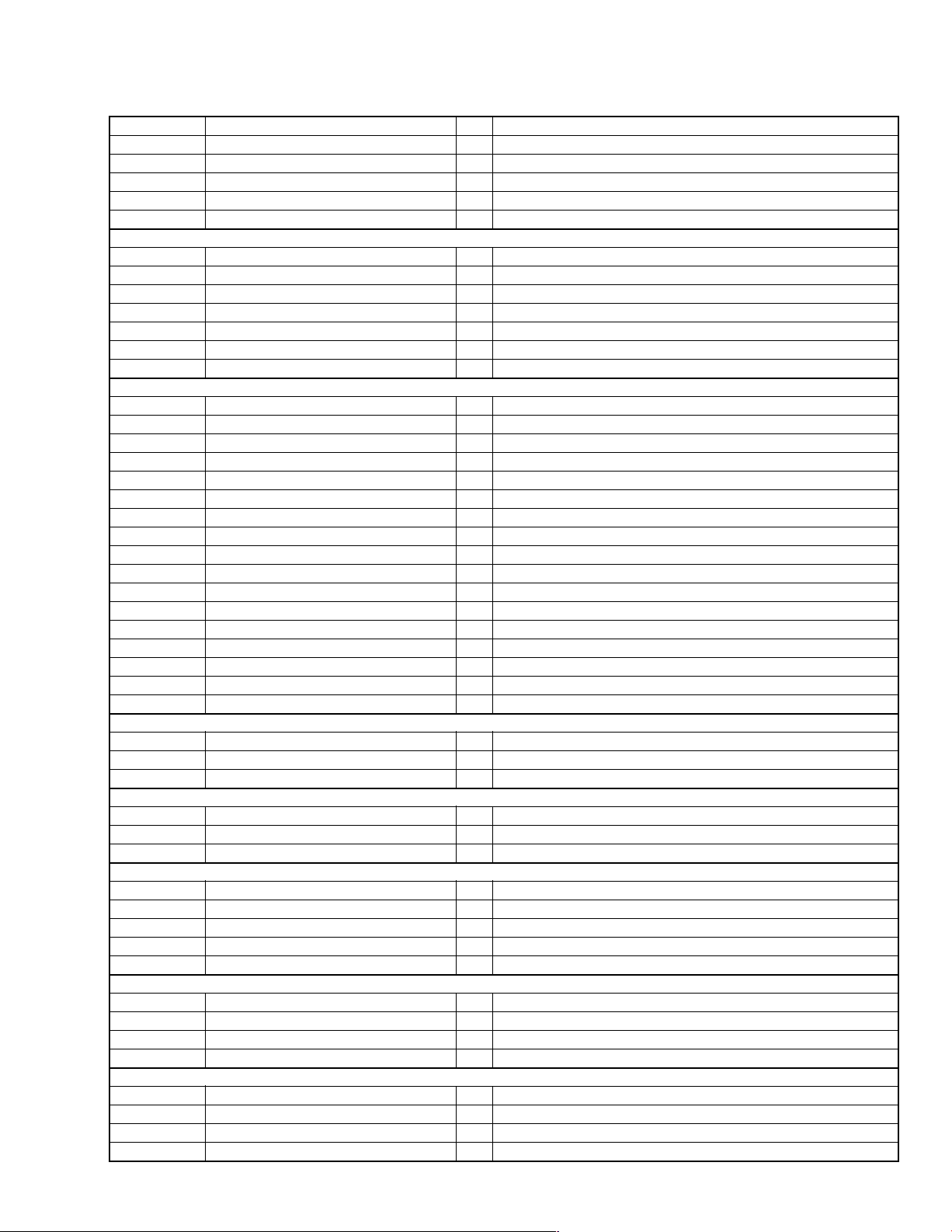

1. Port list sorted by function for MPEG Processor IC(Main IC21)

Port No. Port Name I/O Port Description

Audio DAC

51 DAC SCLK (BCK) O DAC sampling clock.

52 DAC PCMOUT0 O DAC PCM data out 0.

53 DAC PCMOUT1 O DAC PCM out 1 (unused).

54 DAC PCMOUT2 O DAC PCM out 2 (unused).

55 DAC PCMCLK O DAC PCM clock.

56 DAC LRCLK O DAC PCM Left/Right clock.

57 SPDIF OUT O Audio digital data output.

48 VDD PCM - Supply voltage for PCM (+2V5).

49 VSS PCM - Ground for PCM.

Clock & Reset

124 RESET I Chip reset input.

122 VDD PLL - Supply voltage for PLL (+2V5).

123 VSS PLL - Ground for PLL.

120 PIX CLK I 27MHz main clock input.

PIOs and communication

186 PIO0(0) T STROBE I/O Flash ROM down-load JIG module signal.

187 PIO0(1) MOD SW I/O Flash ROM down-load JIG module signal.

188 PIO0(2) VFD STB O VFD strobe output.

189 PIO0(3) VFD CLK O VFD clock output.

190 PIO0(4) VFD DATA OUT O VFD data output.

191 PIO0(5) VFD DATA IN I Data input from VFD.

192

193

194 PIO1(0) SDA I/O 12C serial data.

195 PIO1(1) SCL I/O 12C serial clock.

196

197 PIO1(3) TXD(JIG) I/O UART TXD

200 PIO1(4) RXD(JIG) I/O UART RXD

201 PIO1(5) FRONT TXDI I/O Unused.

202 TRIGGER IN I/O Trigger input from JIG.

203 TRIGGER OUT I/O Trigger output from JIG.

204 PIO2(0) H/P IND - Unused.

205 PIO2(1) FRONT RXD - Unused.

✽

✽

✽

✽

206 PIO2(2) MIC DET I Detection port of MIC jack.

207 PIO2(3) MIC MUTE - Unused.

208 PIO2(4) AUDIO MUTE O Audio mute control.

1 PIO2(5) RGB SEL(BLANK) I/O RGB sel (blank). E/T type only

2 PIO2(6) VIDEO MUTE I/O Video mute control.

3 PIO2(7) 16: 9 INDICATOR I/O 16 : 9 indicator (E/T type only)

6 PIO3(0) SCART H (TV/AUX) I/O Unused.

7 PIO3(1) I/O Unused.

8 PIO3(2) CSB O 3-wire MPU chip select/2-wire MPU interface address selection.

9 PIO3(3) SDIN O 3-wire MPU data output /2-wire MPU data output.

10 PIO3(4) IR REMOCON I/O IR Remote controller signal output.

11 PIO3(5) SCLK O 3-wire MPU clock output /2-wire MPU clock output.

12 PIO3(6) I/O Unused

13 PIO3(7) DVD RESET I/O Power- on reset of front-end module.

39 PIO4(0)HP MUTE - Unused.

40 PIO4(1) - Unused.

41 PIO4(2) DAC SCKDSD O DAC system clock output

PIO0(6) SLIDER SENSOR

OPEN/CLOSE (DRAWER POSITION)

PIO0(7) SLIDER IN

(DRAWER CCW/CTRL)

PIO1(2) SLIDER OUT

(DRAWER CW CTRL)

I/O Detection port of slider sensor for DVD mechanism.

I/O Control port of slider (IN) for DVD mechanism.

I/O Control port of slider (OUT) for DVD mechanism.

4

DVF-3060/3060-S/3060K-S

CIRCUIT DESCRIPTION

Port No. Port Name I/O Port Description

42 PIO4(3) DAC SDIDEM O DAC data output.

43 PIO4(4) DAC MUTEB O DAC mute control.

44 PIO4(5) DAC LAT12S O DAC latch output.

45 PIO4(6) DAC CSBIWL O DAC chip select.

46 PIO4(7) ZERO I/O Zero data flag.

Reserved

20 B WCLK I/O Unused.

21 B V4 I/O Unused.

22 NRSS OUT I/O Unused.

✽

✽

✽

✽

103 ADC SCLK I/O Digital audio port clock.

104 ADC LRCLK I/O ADC sample rate clock

105 ADC DATA I ADC digital audio data input.

106 ADC PCMCLK O Crystal input or master clock input (MCLK).

EMI Interface

161~170 CPU ADR(1~10) O Flash ROM address (1~10).

173~183 CPU ADR(11~21) O Flash ROM address (11~21).

141~148 CPU DATA(0~7) I/O Flash ROM data input/output (0~7).

151~158 CPU DATA(8~15) I/O Flash ROM data input/output (8~15).

138 CPU RAS1 I/O Unused.

131 CPU WAIT I Wait state (connected to be ground).

130 CPU RW O Unused.

128 CPU BE(0) O Flash ROM write enable.

129 CPU BE(1) O Unused.

139 CPU CAS0 O Unused.

140 CPU CAS1 O Unused.

135 CPU CE(0) O Unused.

134 CPU CE(1) O Unused.

133 CPU CE(2) O Flash ROM down-load JIG module select.

132 CPU CE(3) O Flash ROM chip select.

118 CPU PRO CLK O SDRAM clock (unused).

117 CPU OE I/O Flash ROM output enable.

Interrupt

127 IRQ(0) I Unused.

126 IRQ(1) I Unused.

125 IRQ(2) I Interrupt request 2 from front-end module.

Timers

116 PWM0 I/O Unused.

115 PWM1 I/O ROM boot option port (voltage low = emulator booting).

114 PWM2 I/O Unused.

JTAG

113 TCK I Test clock input from emulator module.

112 TDI I Test data input from emulator module.

111 TDO O Test data out to emulator module.

110 TMS I Test mode select.

109 TRST4 I Test reset from emulator module.

Front-end

16 B DATA I Pack data of front-end serial data.

17 B BCLK I Bit clock of front-end serial data.

18 B FLAG I Pack clock of front-end serial data.

19 B SYNC I Sector start of front-end serial data.

Video DAC

27,26,25 R/G/B (OUT) O R/G/B signal outputs.

32~34 Y/C/CV (OUT) O Y/C/CV signal outputs.

29 I REF RG I Reference current input for DAC RGB.

28 V REF RG I Reference voltage input for DAC RGB.

5

DVF-3060/3060-S/3060K-S

CIRCUIT DESCRIPTION

Port No. Port Name I/O Port Description

36 I REF YCC I Reference current input for DAC YCC.

35 V REF YCC I Reference voltage input for DAC YCC.

23 VDD RGB - Supply voltage for RGB (+2.5VA).

24 VSS RGB - GND

30 VDD YCC - Supply voltage for YCC (+2.5VA).

31 VSS YCC - GND

Shared memory interface

66~69 SMI ADR(3~0) O SDRAM address bus.

58~63 SMI ADR(4~9) O SDRAM address bus.

70~73 SMI ADR(10~13) O SDRAM address bus.

84~93 SMI DATA(0~9)

97~102 SMI DATA(10~15)

74 SMI CS(0) O Chip select bank 0.

75 SMI CS(1) - Unused.

76 SMI RAS O SDRAM RAS

77 SMI CAS O SDRAM CAS

78 SMI WE O SDRAM write enable

79 SMI DQML O DQ MASK enable low.

80 SMI DQMU O DQ MASK enable up.

82 SMI CLKIN I SDRAM clock input.

95 SMI CLKOUT O SDRAM clock out.

Power supply

4,47,81,107

136,159,184

14,37,64,94

119,149,171 VDD2 5 - 2.5V Power supply.

198

5,15,38,50,65

83,96,108,121

137,150,160

172,185,199

✽ M type only

VDD3 3 - 3.3V Power supply.

VSS - GND

I/O SDRAM data bus.

2. Description of Ics

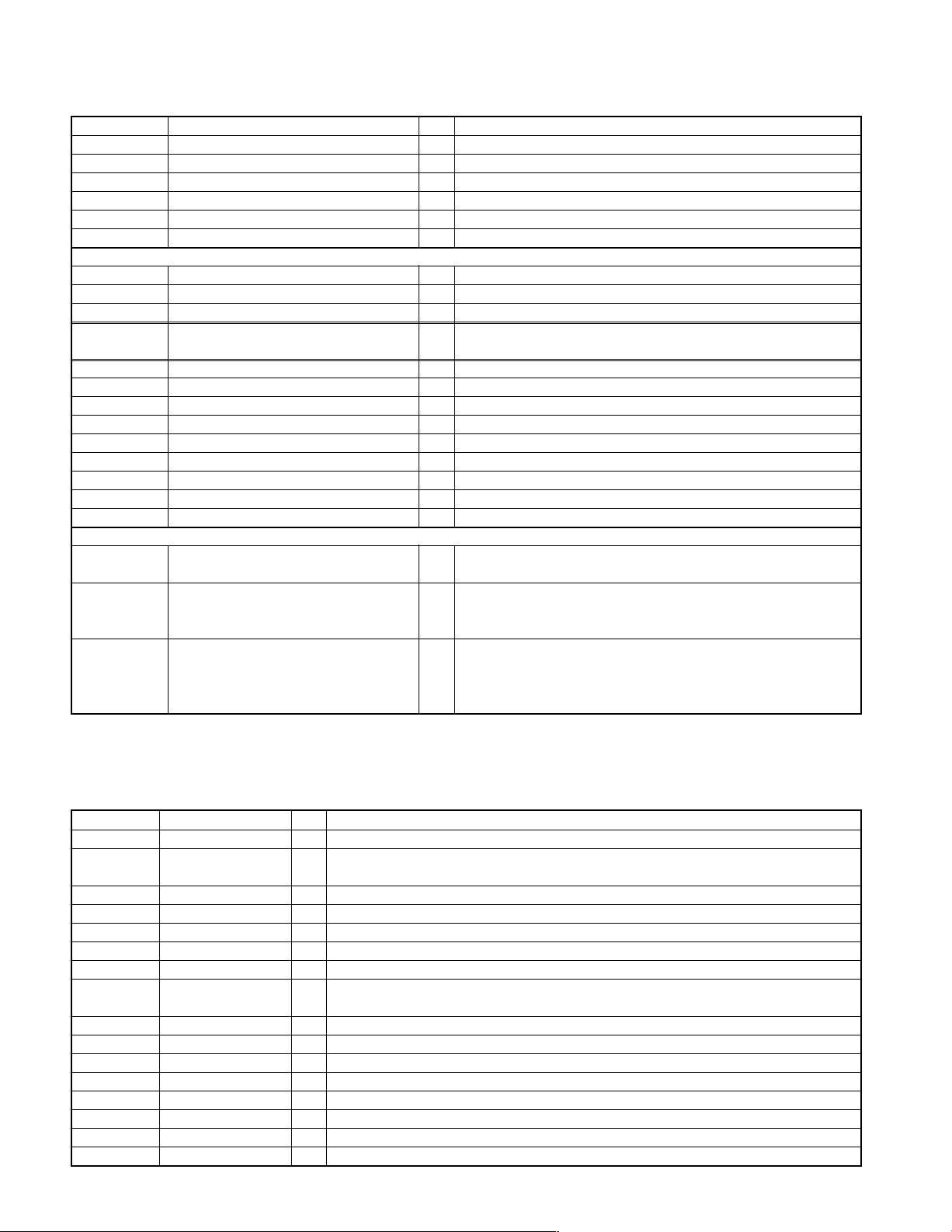

2-1 VFO controller : uPD16311(IC91)

Pin No. Pin Name I/O Pin Description

6 DIN I Inputs serial data at rising edge of shift clock, starting from lower bit.

5 DOUT O

9 STB - Strobe pin.

8 CLK I Reads serial data at rising edge, and output data at falling edge.

52 OSC - Connect resistor for determining oscillation frequency to this pin.

15~26 S1/KS1~S12/KS12 O Segment output pins (Dual function as key source).

35~44 G10~G1 O Grid output pins.

27~30 S13~S16

31,32 12G,11G

46,47,49,50 LED (5,4,2,1) O Unused.

48 LED3 O Control pin of standby LED.

10~13 KEY1~KEY4 I Data input to these pins is latched at end of display cycle.

1~4 N.C. - Unused.

14,33,45 VDD - +5V power supply.

51 VSS - Connect this pin to GND of system.

34 VEE - -27V power supply.

7 N.C. - Unused.

6

Output serial data at falling edge of shift clock, starting from lower bit.

This is N-ch open-drain output pin.

O These pins are selectable for segment or grid output.

DVF-3060/3060-S/3060K-S

CIRCUIT DESCRIPTION

2-2 HEX Inverter (Single Stage) : M74HCU04(IC51)

Pin No. Pin Name I/O Pin Description

1,3,5,9,11,13 A0 to A5 I Data Inputs

2,4,6,8,10,12 Q0 to Q5 O Data Outputs

7 GND - Ground

14 VCC - Positive Supply Voltage

2-3 Flash Memory : M29W 800AT

Pin No. Pin Name I/O Pin Description

1~8 A15~A8 I Address Inputs

9,10 N.C. - Unused

11 WE - Write Enable

12 RP - Reset/Block Temporary Unprotect

13,14 N.C. - Unused

15 RY/BY O Ready/Busy/Output

16,17 A18,A17 I Address Inputs

18~25 A7~A0 I Address Inputs

26 CE - Chip Enable

27,46 VSS - Ground

28 QE - Output Enable

29~36

38~45

37 VCC - Supply Voltage

45 DQ15 I/O Data Input/Outputs or Address input

47 BYTE - Byte/Word Organization

48 A16 I Address Inputs

DQ0~DQ15 I/O Data Input/Outputs, Command Inputs

Truth Table

AQ

LH

HL

2-4 DC Motor Driver : KA8082(IC23)

Pin No. Pin Name I/O Pin Description

1 GND - Ground

2 VO1 O Output 1

3 VCTL I Motor speed control

4 VIN1 I Input 1

5 VIN2 I Input 2

6 SVCC - Supply voltage (Signal)

7 PVCC - Supply voltage (Power)

8 VO2 O Output 2

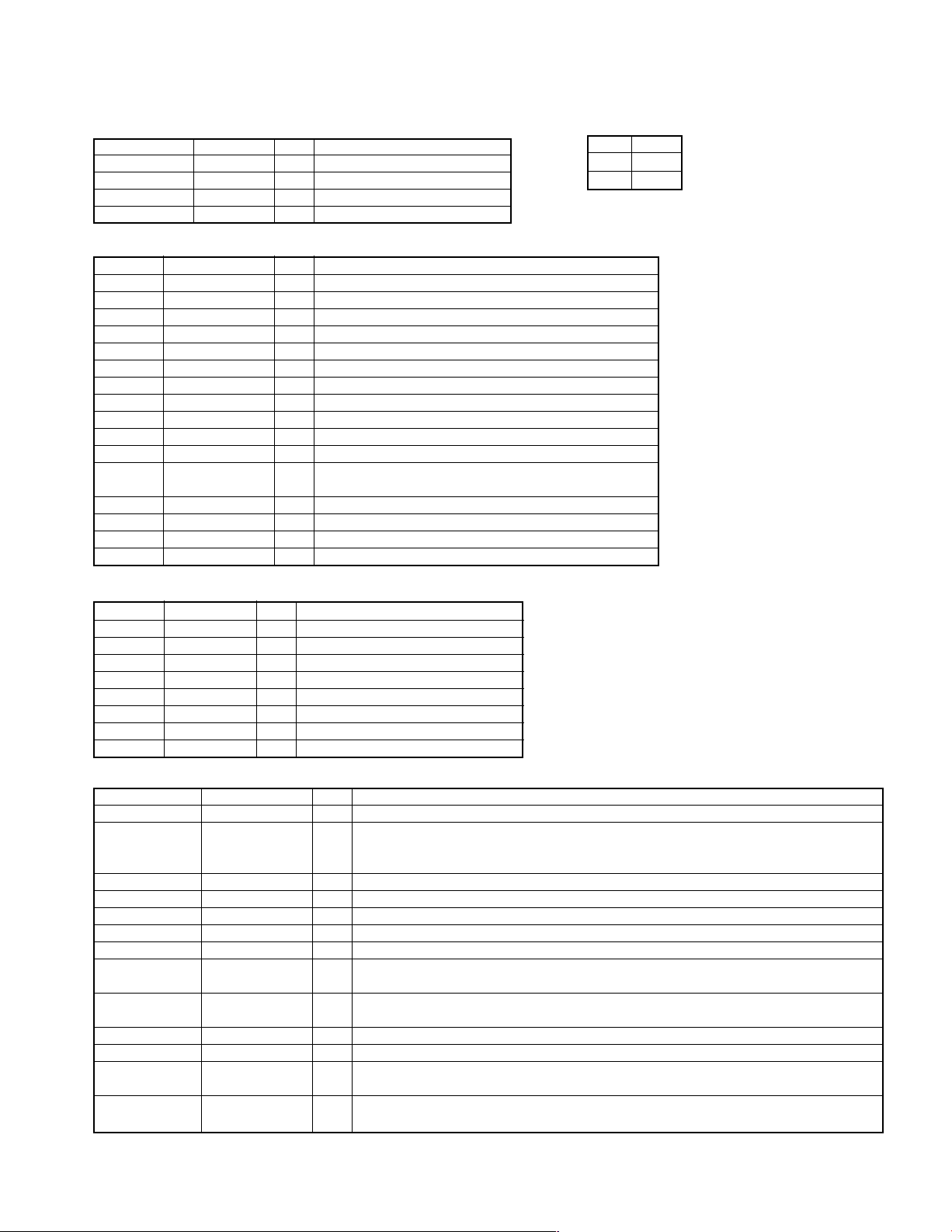

2-5 64 Bit SDRAM : HY57V641620HGT

Pin No. Pin Name I/O Pin Description

1,14,27, VCC - Power supply for internal circuits and input buffers.

2,4,5,7,8,10

11,13,42,44 45, DQ0~DQ15 I/O Multiplexed data input/output pin.

47,48,5051,53

3,9,43,49 VCCQ - Power supply for output buffers.

6,12,46,52 VSSQ - Ground for output buffer.

15,39 LDQM,UDQM I/O Controls output buffers in read mode and masks input data in write mode.

16,17,18 WE,CAS,RAS - WE, CAS and RAS define the operation.

19 CS - Enables or disables all inputs except CLK, CKE, and DQM.

20,21 BA0,BA1 -

22,23~26 A10, A0~A3

29~34,35 A4~A9, A11

28,41,54 VSS - Ground for internal circuits and input buffers.

36,40 NC - Unused.

37 CKE -

38 CLK I

Selects bank to be activated during RAS activity.

Selects bank to be read/written during CAS activity.

- Address bus : A0~A11

Controls internal clock signal and when deactivated, the SDRAM will be

one of the states among power down, suspend or self refresh.

The system clock input. all other inputs are registered to the SDRAM on

the rising edge of CLK.

7

Loading...

Loading...