ISSI IS61NLF25618-9TQ, IS61NLF25618-9B, IS61NLF25618-10TQI, IS61NLF25618-10TQ, IS61NLF25618-10B Datasheet

...

IS61NF12832 IS61NF12836 IS61NF25618 ISSI®

IS61NLF12832 IS61NLF12836 IS61NLF25618

128K x 32, 128K x 36 and 256K x 18 FLOW-THROUGH 'NO WAIT' STATE BUS SRAM

PRELIMINARY INFORMATION

OCTOBER 2000

FEATURES |

DESCRIPTION |

•100 percent bus utilization

•No wait cycles between Read and Write

•Internal self-timed write cycle

•Individual Byte Write Control

•Single R/W (Read/Write) control pin

•Clock controlled, registered address, data and control

•Interleaved or linear burst sequence control using MODE input

•Three chip enables for simple depth expansion and address pipelining for TQFP

•Power Down mode

•Common data inputs and data outputs

•CKE pin to enable clock and suspend operation

•JEDEC 100-pin TQFP, 119 PBGA package

•Single +3.3V power supply (± 5%)

•NF Version: 3.3V I/O Supply Voltage

•NLF Version: 2.5V I/O Supply Voltage

•Industrial temperature available

FAST ACCESS TIME

The 4 Meg 'NF' product family feature high-speed, low-power synchronous static RAMs designed to provide a burstable, high-performance, 'no wait' state, device for network and communications customers. They are organized as 131,072 words by 32 bits, 131,072 words by 36 bits and 262,144 words by 18 bits, fabricated with ISSI's advanced CMOS technology.

Incorporating a 'no wait' state feature, wait cycles are eliminated when the bus switches from read to write, or write to read. This device integrates a 2-bit burst counter, high-speed SRAM core, and high-drive capability outputs into a single monolithic circuit.

All synchronous inputs pass through registers are controlled by a positive-edge-triggered single clock input. Operations may be suspended and all synchronous inputs ignored when Clock Enable, CKE is HIGH. In this state the internal device will hold their previous values.

All Read, Write and Deselect cycles are initiated by the ADV input. When the ADV is HIGH the internal burst counter is incremented. New external addresses can be loaded when ADV is LOW.

Write cycles are internally self-timed and are initiated by the rising edge of the clock inputs and when WE is LOW. Separate byte enables allow individual bytes to be written.

A burst mode pin (MODE) defines the order of the burst sequence. When tied HIGH, the interleaved burst sequence is selected. When tied LOW, the linear burst sequence is selected.

Symbol |

Parameter |

-8.5* |

-9 |

-10 |

Units |

tKQ |

Clock Access Time |

8.5 |

9 |

10 |

ns |

|

|

|

|

|

|

tKC |

Cycle Time |

10 |

12 |

12 |

ns |

|

|

|

|

|

|

|

Frequency |

100 |

83 |

83 |

MHz |

|

|

|

|

|

|

*This speed available only in NF version

This document contains PRELIMINARY INFORMATION data. ISSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which may appear in this publication. © Copyright 2000, Integrated Silicon Solution, Inc.

Integrated Silicon Solution, Inc. — 1-800-379-4774 |

1 |

PRELIMINARY INFORMATION Rev. 00C

11/30/00

IS61NF12832 |

IS61NF12836 |

IS61NF25618 |

ISSI |

® |

IS61NLF12832 |

IS61NLF12836 |

IS61NLF25618 |

|

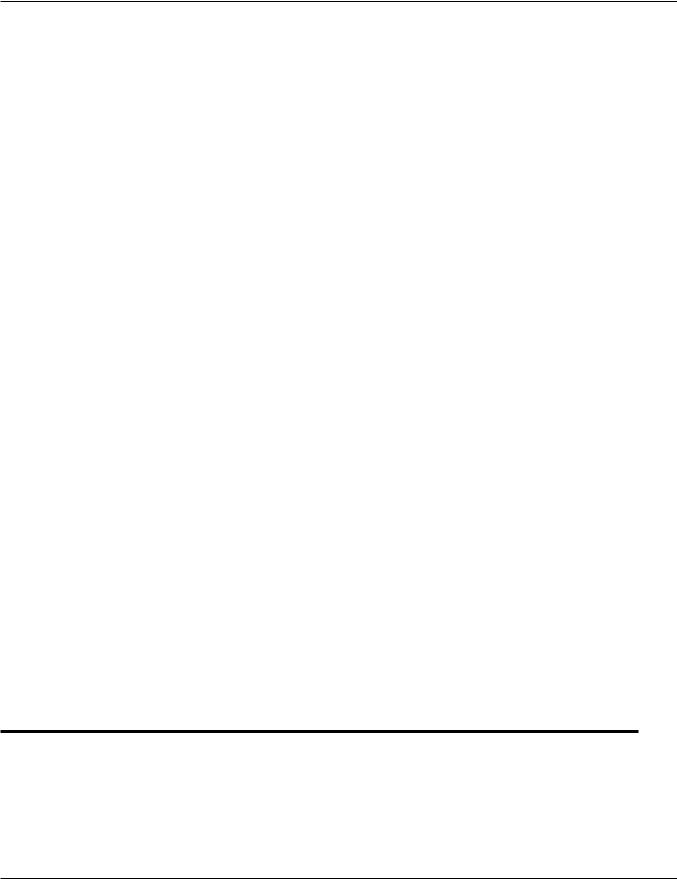

BLOCK DIAGRAM

A [0:16] or |

ADDRESS |

A2-A16 or A2-A17 |

128Kx32; 125Kx36; |

|||

|

|

|||||

A [0:17] |

REGISTER |

|

|

|

256Kx18 |

|

|

|

|

|

|

|

MEMORY ARRAY |

|

|

|

MODE |

BURST |

|

|

|

|

|

A0-A1 |

ADDRESS |

A'0-A'1 |

|

|

|

|

COUNTER |

|

||

|

|

|

|

|

|

|

CLK |

CONTROL |

|

WRITE |

|

K |

DATA-IN |

CKE |

LOGIC |

K |

ADDRESS |

|

|

REGISTER |

REGISTER |

|

|

|

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

CE |

|

|

|

|

|

|

CE2 |

|

|

|

|

|

|

CE2 |

|

|

|

|

|

|

ADV |

CONTROL |

|

|

|

|

|

REGISTER |

|

|

|

|

||

BWŸWEX } |

|

CONTROL |

|

|

||

|

|

|

|

|

||

|

|

|

LOGIC |

|

|

|

(X=a,b,c,d or a,b) |

|

|

|

|

BUFFER |

|

|

|

|

|

|

|

|

OE |

|

|

|

|

|

|

ZZ |

|

|

|

|

32, 36 or 18 |

|

DQa0-DQd7 or DQa0-DQb8 |

|

|

|

|||

|

|

|

|

|||

DQPa-DQPd |

|

|

|

|

|

|

2 |

Integrated Silicon Solution, Inc. — 1-800-379-4774 |

PRELIMINARY INFORMATION Rev. 00C

11/30/00

IS61NF12832 |

IS61NF12836 |

IS61NF25618 |

ISSI |

® |

IS61NLF12832 |

IS61NLF12836 |

IS61NLF25618 |

|

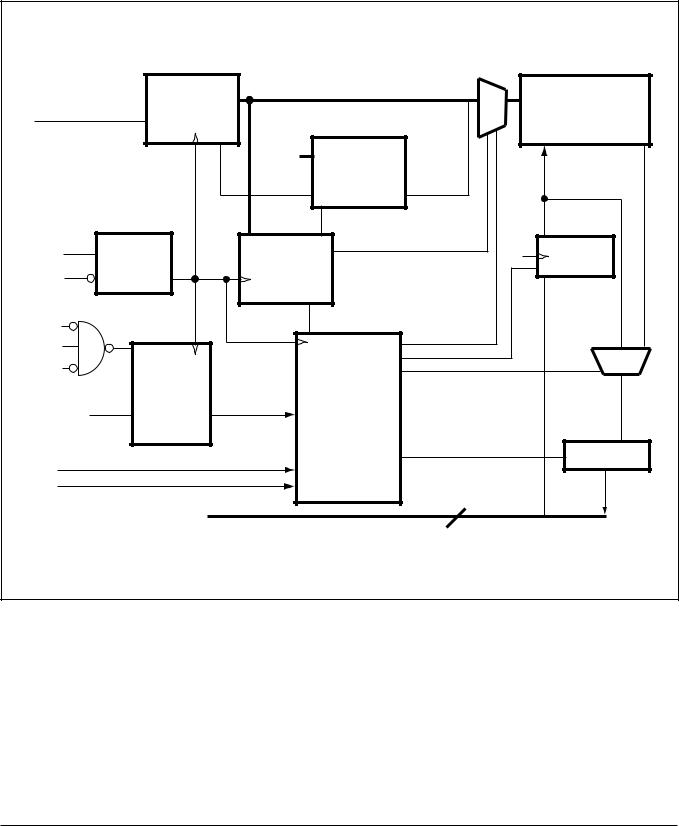

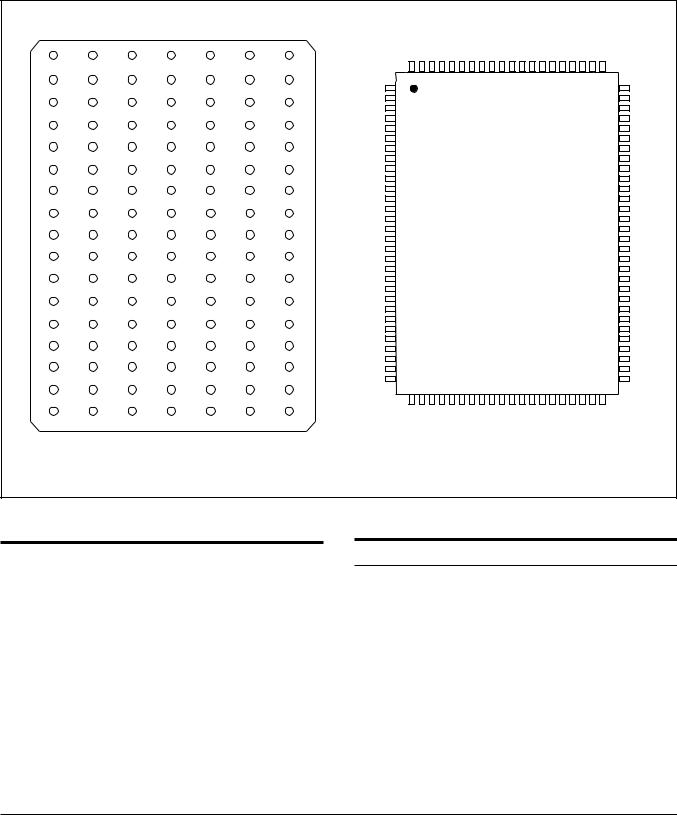

PIN CONFIGURATION

119-pin PBGA (Top View) and 100-Pin TQFP

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

A6 |

A7 CE |

CE2 |

BWd BWc BWb BWa |

CE2 VCC |

GND CLK WE CKE OE |

ADV |

NC NC A8 |

A9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCCQ |

A6 |

A4 |

NC |

A8 |

A16 |

VCCQ |

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

|

100 99 98 97 |

96 95 94 93 |

92 91 90 89 88 87 86 |

85 84 83 82 81 |

|

|||||

NC |

CE2 |

A3 |

ADV |

A9 |

CE2 |

NC |

NC |

1 |

|

|

|

|

|

|

|

80 |

NC |

C |

|

|

|

|

|

|

DQc1 |

2 |

|

|

|

|

|

|

|

79 |

DQb8 |

NC |

A7 |

A2 |

VCC |

A12 |

A15 |

NC |

DQc2 |

3 |

|

|

|

|

|

|

|

78 |

DQb7 |

D |

|

|

|

|

|

|

VCCQ |

4 |

|

|

|

|

|

|

|

77 |

VCCQ |

|

|

|

|

|

|

GND |

5 |

|

|

|

|

|

|

|

76 |

GND |

|

DQc1 |

NC |

GND |

NC |

GND |

NC |

DQb8 |

|

|

|

|

|

|

|

||||

E |

|

|

|

|

|

|

DQc3 |

6 |

|

|

|

|

|

|

|

75 |

DQb6 |

|

|

|

|

|

|

DQc4 |

7 |

|

|

|

|

|

|

|

74 |

DQb5 |

|

DQc2 |

DQc3 |

GND |

CE |

GND |

DQb6 |

DQb7 |

|

|

|

|

|

|

|

||||

DQc5 |

8 |

|

|

|

|

|

|

|

73 |

DQb4 |

|||||||

F |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

DQc6 |

9 |

|

|

|

|

|

|

|

72 |

DQb3 |

|

VCCQ |

DQc4 |

GND |

OE |

GND |

DQb5 |

VCCQ |

|

|

|

|

|

|

|

||||

GND |

10 |

|

|

|

|

|

|

|

71 |

GND |

|||||||

G |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

VCCQ |

11 |

|

|

|

|

|

|

|

70 |

VCCQ |

|

DQc5 |

DQc6 |

BWc |

NC |

BWb |

DQb4 |

DQb3 |

DQc7 |

12 |

|

|

|

|

|

|

|

69 |

DQb2 |

H |

|

|

|

|

|

|

DQc8 |

13 |

|

|

|

|

|

|

|

68 |

DQb1 |

DQc7 |

DQc8 |

GND |

WE |

GND |

DQb2 |

DQb1 |

GND |

14 |

|

|

|

|

|

|

|

67 |

GND |

J |

|

|

|

|

|

|

VCC |

15 |

|

|

|

|

|

|

|

66 |

GND |

|

|

|

|

|

|

VCC |

16 |

|

|

|

|

|

|

|

65 |

VCC |

|

VCCQ |

VCC |

NC |

VCC |

NC |

VCC |

VCCQ |

|

|

|

|

|

|

|

||||

K |

|

|

|

|

|

|

GND |

17 |

|

|

|

|

|

|

|

64 |

ZZ |

|

|

|

|

|

|

DQd1 |

18 |

|

|

|

|

|

|

|

63 |

DQa8 |

|

DQd1 |

DQd2 |

GND |

CLK |

GND |

DQa7 |

DQa8 |

|

|

|

|

|

|

|

||||

DQd2 |

19 |

|

|

|

|

|

|

|

62 |

DQa7 |

|||||||

L |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

VCCQ |

20 |

|

|

|

|

|

|

|

61 |

VCCQ |

|

DQd4 |

DQd3 |

BWd |

NC |

BWa |

DQa5 |

DQa6 |

|

|

|

|

|

|

|

||||

GND |

21 |

|

|

|

|

|

|

|

60 |

GND |

|||||||

M |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

DQd3 |

22 |

|

|

|

|

|

|

|

59 |

DQa6 |

|

VCCQ |

DQd5 |

GND |

CKE |

GND |

DQa4 |

VCCQ |

DQd4 |

23 |

|

|

|

|

|

|

|

58 |

DQa5 |

N |

|

|

|

|

|

|

DQd5 |

24 |

|

|

|

|

|

|

|

57 |

DQa4 |

DQd6 |

DQd7 |

GND |

A1 |

GND |

DQa3 |

DQa2 |

DQd6 |

25 |

|

|

|

|

|

|

|

56 |

DQa3 |

P |

|

|

|

|

|

|

GND |

26 |

|

|

|

|

|

|

|

55 |

GND |

DQd8 |

NC |

GND |

A0 |

GND |

NC |

DQa1 |

VCCQ |

27 |

|

|

|

|

|

|

|

54 |

VCCQ |

R |

|

|

|

|

|

|

DQd7 |

28 |

|

|

|

|

|

|

|

53 |

DQa2 |

|

|

|

|

|

|

DQd8 |

29 |

|

|

|

|

|

|

|

52 |

DQa1 |

|

NC |

A5 |

MODE |

VCC |

NC |

A13 |

NC |

|

|

|

|

|

|

|

||||

NC |

30 |

|

|

|

|

|

|

|

51 |

NC |

|||||||

T |

|

|

|

|

|

|

|

34 35 36 37 38 39 40 |

|

|

|

||||||

|

|

|

|

|

|

|

31 32 33 |

41 42 43 44 45 46 47 48 49 50 |

|

||||||||

NC |

NC |

A10 |

A11 |

A14 |

NC |

ZZ |

|

|

|

|

|

|

|

|

|

|

|

U |

|

|

|

|

|

|

|

MODE |

A5 A4 |

A3 |

A2 A1 A0 NC |

NC GND |

VCC NC NC A10 A11 |

A12 |

A13 A14 A15 |

A16 |

|

VCCQ |

NC |

NC |

NC |

NC |

NC |

VCCQ |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

128K x 32 |

|

|

|

|

|

|

|

|

|

|

|

PIN DESCRIPTIONS

A0, A1 |

Synchronous Address Inputs. These |

|

pins must tied to the two LSBs of the |

|

address bus. |

|

|

A2-A16 |

Synchronous Address Inputs |

|

|

CLK |

Synchronous Clock |

|

|

ADV |

Synchronous Burst Address Advance |

|

|

BWa-BWd |

Synchronous Byte Write Enable |

|

|

WE |

Write Enable |

|

|

CKE |

Clock Enable |

|

|

CE, CE2, CE2 Synchronous Chip Enable

OE |

Output Enable |

|

|

DQa-DQd |

Synchronous Data Input/Output |

|

|

MODE |

Burst Sequence Mode Selection |

|

|

VCC |

+3.3V Power Supply |

|

|

GND |

Ground |

|

|

VCCQ |

Isolated Output Buffer Supply: +3.3V/2.5V |

|

|

ZZ |

Snooze Enable |

|

|

Integrated Silicon Solution, Inc. — 1-800-379-4774 |

3 |

PRELIMINARY INFORMATION Rev. 00C

11/30/00

IS61NF12832 |

IS61NF12836 |

IS61NF25618 |

ISSI |

® |

IS61NLF12832 |

IS61NLF12836 |

IS61NLF25618 |

|

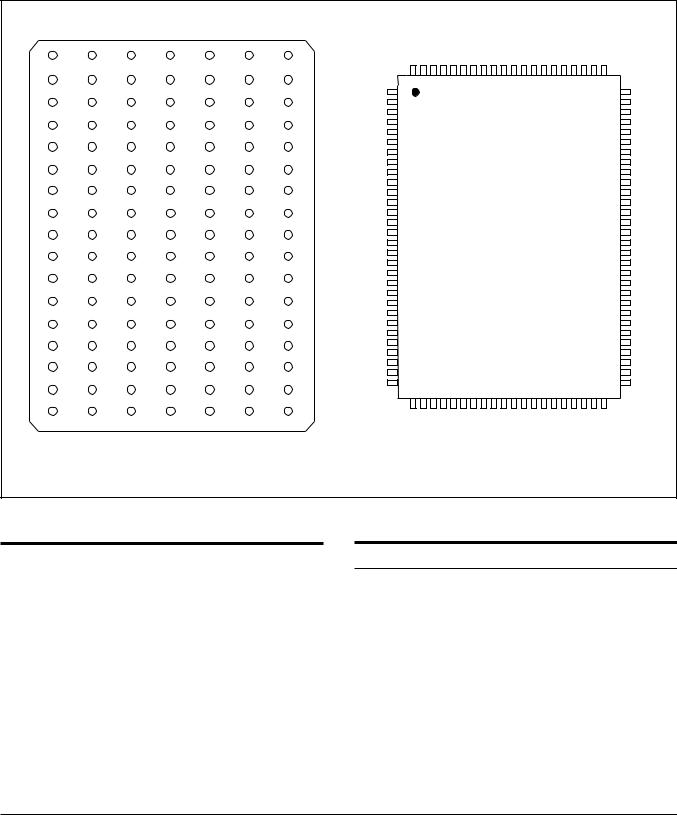

PIN CONFIGURATION

119-pin PBGA (Top View) and 100-Pin TQFP

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

|

|

BWd BWc BWb BWa |

|

|

GND CLK WE CKE OE |

|

|

|

|

A |

|

|

|

|

|

|

|

A6 |

A7 CE |

CE2 |

CE2 |

VCC |

ADV |

NC NC A8 |

A9 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCCQ |

A6 |

A4 |

NC |

A8 |

A16 |

VCCQ |

|

100 99 98 97 |

96 95 94 93 |

92 91 90 89 88 87 86 |

85 84 83 82 81 |

|

||||||

B |

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

DQPc |

1 |

|

|

|

|

|

|

|

|

80 |

DQPb |

|

NC |

CE2 |

A3 |

ADV |

A9 |

CE2 |

NC |

|

|

|

|

|

|

|

|

||||

C |

|

|

|

|

|

|

DQc1 |

2 |

|

|

|

|

|

|

|

|

79 |

DQb8 |

|

|

|

|

|

|

DQc2 |

3 |

|

|

|

|

|

|

|

|

78 |

DQb7 |

|

NC |

A7 |

A2 |

VCC |

A12 |

A15 |

NC |

|

|

|

|

|

|

|

|

||||

VCCQ |

4 |

|

|

|

|

|

|

|

|

77 |

VCCQ |

|||||||

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

GND |

5 |

|

|

|

|

|

|

|

|

76 |

GND |

|

DQc1 |

DQPc |

GND |

NC |

GND |

DQPb |

DQb8 |

|

|

|

|

|

|

|

|

||||

DQc3 |

6 |

|

|

|

|

|

|

|

|

75 |

DQb6 |

|||||||

E |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

DQc4 |

7 |

|

|

|

|

|

|

|

|

74 |

DQb5 |

|

DQc2 |

DQc3 |

GND |

CE |

GND |

DQb6 |

DQb7 |

DQc5 |

8 |

|

|

|

|

|

|

|

|

73 |

DQb4 |

F |

|

|

|

|

|

|

DQc6 |

9 |

|

|

|

|

|

|

|

|

72 |

DQb3 |

VCCQ |

DQc4 |

GND |

OE |

GND |

DQb5 |

VCCQ |

GND |

10 |

|

|

|

|

|

|

|

|

71 |

GND |

G |

|

|

|

|

|

|

VCCQ |

11 |

|

|

|

|

|

|

|

|

70 |

VCCQ |

|

|

|

|

|

|

DQc7 |

12 |

|

|

|

|

|

|

|

|

69 |

DQb2 |

|

DQc5 |

DQc6 |

BWc |

NC |

BWb |

DQb4 |

DQb3 |

|

|

|

|

|

|

|

|

||||

H |

|

|

|

|

|

|

DQc8 |

13 |

|

|

|

|

|

|

|

|

68 |

DQb1 |

|

|

|

|

|

|

GND |

14 |

|

|

|

|

|

|

|

|

67 |

GND |

|

DQc7 |

DQc8 |

GND |

WE |

GND |

DQb2 |

DQb1 |

|

|

|

|

|

|

|

|

||||

VCC |

15 |

|

|

|

|

|

|

|

|

66 |

GND |

|||||||

J |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

VCC |

16 |

|

|

|

|

|

|

|

|

65 |

VCC |

|

VCCQ |

VCC |

NC |

VCC |

NC |

VCC |

VCCQ |

|

|

|

|

|

|

|

|

||||

GND |

17 |

|

|

|

|

|

|

|

|

64 |

ZZ |

|||||||

K |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

DQd1 |

18 |

|

|

|

|

|

|

|

|

63 |

DQa8 |

|

DQd1 |

DQd2 |

GND |

CLK |

GND |

DQa7 |

DQa8 |

DQd2 |

19 |

|

|

|

|

|

|

|

|

62 |

DQa7 |

L |

|

|

|

|

|

|

VCCQ |

20 |

|

|

|

|

|

|

|

|

61 |

VCCQ |

DQd4 |

DQd3 |

BWd |

NC |

BWa |

DQa5 |

DQa6 |

GND |

21 |

|

|

|

|

|

|

|

|

60 |

GND |

M |

|

|

|

|

|

|

DQd3 |

22 |

|

|

|

|

|

|

|

|

59 |

DQa6 |

VCCQ |

DQd5 |

GND |

CKE |

GND |

DQa4 |

VCCQ |

DQd4 |

23 |

|

|

|

|

|

|

|

|

58 |

DQa5 |

N |

|

|

|

|

|

|

DQd5 |

24 |

|

|

|

|

|

|

|

|

57 |

DQa4 |

|

|

|

|

|

|

DQd6 |

25 |

|

|

|

|

|

|

|

|

56 |

DQa3 |

|

DQd6 |

DQd7 |

GND |

A1 |

GND |

DQa3 |

DQa2 |

|

|

|

|

|

|

|

|

||||

GND |

26 |

|

|

|

|

|

|

|

|

55 |

GND |

|||||||

P |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

VCCQ |

27 |

|

|

|

|

|

|

|

|

54 |

VCCQ |

|

DQd8 |

DQPd |

GND |

A0 |

GND |

DQPa |

DQa1 |

|

|

|

|

|

|

|

|

||||

DQd7 |

28 |

|

|

|

|

|

|

|

|

53 |

DQa2 |

|||||||

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

DQd8 |

29 |

|

|

|

|

|

|

|

|

52 |

DQa1 |

|

NC |

A5 |

MODE |

VCC |

NC |

A13 |

NC |

DQPd |

30 |

|

|

|

|

|

|

|

|

51 |

DQPa |

T |

|

|

|

|

|

|

|

31 32 33 |

34 35 36 37 38 39 40 |

41 42 43 44 45 46 47 48 49 50 |

|

|||||||

NC |

NC |

A10 |

A11 |

A14 |

NC |

ZZ |

|

|

|

|

|

|

|

|

|

|

|

|

U |

|

|

|

|

|

|

|

MODE |

A5 A4 |

A3 |

A2 A1 A0 NC |

NC |

GND |

VCC NC NC A10 A11 |

A12 |

A13 A14 A15 |

A16 |

|

VCCQ |

NC |

NC |

NC |

NC |

NC |

VCCQ |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

128K x 36 |

|

|

|

|

|

|

|

|

|

|

|

|

PIN DESCRIPTIONS

A0, A1 |

Synchronous Address Inputs. These |

|

pins must tied to the two LSBs of the |

|

address bus. |

|

|

A2-A16 |

Synchronous Address Inputs |

|

|

CLK |

Synchronous Clock |

|

|

ADV |

Synchronous Burst Address Advance |

|

|

BWa-BWd |

Synchronous Byte Write Enable |

|

|

WE |

Write Enable |

|

|

CKE |

Clock Enable |

|

|

CE, CE2, CE2 |

Synchronous Chip Enable |

|

|

OE |

Output Enable |

|

|

DQa-DQd |

Synchronous Data Input/Output |

|

|

MODE |

Burst Sequence Mode Selection |

|

|

VCC |

+3.3V Power Supply |

|

|

GND |

Ground |

|

|

VCCQ |

solated Output Buffer Supply: +3.3V/2.5V |

|

|

ZZ |

Snooze Enable |

|

|

DQPa-DQPd |

Parity Data I/O |

|

|

4 Integrated Silicon Solution, Inc. — 1-800-379-4774

PRELIMINARY INFORMATION Rev. 00C

11/30/00

IS61NF12832 |

IS61NF12836 |

IS61NF25618 |

ISSI |

® |

IS61NLF12832 |

IS61NLF12836 |

IS61NLF25618 |

|

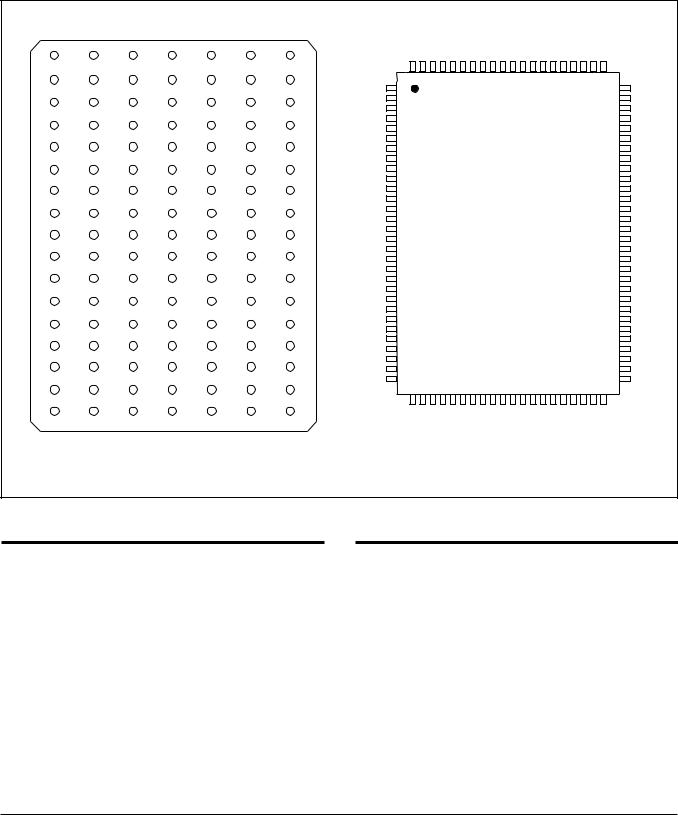

PIN CONFIGURATION

119-pin PBGA (Top View) and 100-Pin TQFP

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

|

|

NC NC BWb BWa |

|

GND CLK WE CKE OE |

|

|

|

|

A |

|

|

|

|

|

|

|

A6 |

A7 CE |

CE2 |

CE2 VCC |

ADV |

NC NC A8 |

A9 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCCQ |

A6 |

A4 |

NC |

A8 |

A16 |

VCCQ |

|

100 99 98 97 |

96 95 94 93 |

92 91 90 89 88 87 86 |

85 84 83 82 81 |

|

|||||

B |

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

NC |

1 |

|

|

|

|

|

|

|

80 |

A10 |

|

NC |

CE2 |

A3 |

ADV |

A9 |

CE2 |

NC |

|

|

|

|

|

|

|

||||

C |

|

|

|

|

|

|

NC |

2 |

|

|

|

|

|

|

|

79 |

NC |

|

|

|

|

|

|

NC |

3 |

|

|

|

|

|

|

|

78 |

NC |

|

NC |

A7 |

A2 |

VCC |

A12 |

A15 |

NC |

|

|

|

|

|

|

|

||||

VCCQ |

4 |

|

|

|

|

|

|

|

77 |

VCCQ |

|||||||

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

GND |

5 |

|

|

|

|

|

|

|

76 |

GND |

|

DQ9 |

NC |

GND |

NC |

GND |

DQP1 |

NC |

|

|

|

|

|

|

|

||||

NC |

6 |

|

|

|

|

|

|

|

75 |

NC |

|||||||

E |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

NC |

7 |

|

|

|

|

|

|

|

74 |

DQP1 |

|

NC |

DQ10 |

GND |

CE |

GND |

NC |

DQ8 |

DQ9 |

8 |

|

|

|

|

|

|

|

73 |

DQ8 |

F |

|

|

|

|

|

|

DQ10 |

9 |

|

|

|

|

|

|

|

72 |

DQ7 |

VCCQ |

NC |

GND |

OE |

GND |

DQ7 |

VCCQ |

GND |

10 |

|

|

|

|

|

|

|

71 |

GND |

G |

|

|

|

|

|

|

VCCQ |

11 |

|

|

|

|

|

|

|

70 |

VCCQ |

|

|

|

|

|

|

DQ11 |

12 |

|

|

|

|

|

|

|

69 |

DQ6 |

|

NC |

DQ11 |

BWb |

A17 |

NC |

NC |

DQ6 |

|

|

|

|

|

|

|

||||

H |

|

|

|

|

|

|

DQ12 |

13 |

|

|

|

|

|

|

|

68 |

DQ5 |

|

|

|

|

|

|

GND |

14 |

|

|

|

|

|

|

|

67 |

GND |

|

DQ12 |

NC |

GND |

WE |

GND |

DQ5 |

NC |

|

|

|

|

|

|

|

||||

VCC |

15 |

|

|

|

|

|

|

|

66 |

GND |

|||||||

J |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

VCC |

16 |

|

|

|

|

|

|

|

65 |

VCC |

|

VCCQ |

VCC |

NC |

VCC |

NC |

VCC |

VCCQ |

|

|

|

|

|

|

|

||||

GND |

17 |

|

|

|

|

|

|

|

64 |

ZZ |

|||||||

K |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

DQ13 |

18 |

|

|

|

|

|

|

|

63 |

DQ4 |

|

NC |

DQ13 |

GND |

CLK |

GND |

NC |

DQ4 |

DQ14 |

19 |

|

|

|

|

|

|

|

62 |

DQ3 |

L |

|

|

|

|

|

|

VCCQ |

20 |

|

|

|

|

|

|

|

61 |

VCCQ |

DQ14 |

NC |

NC |

NC |

BWa |

DQ3 |

NC |

GND |

21 |

|

|

|

|

|

|

|

60 |

GND |

M |

|

|

|

|

|

|

DQ15 |

22 |

|

|

|

|

|

|

|

59 |

DQ2 |

VCCQ |

DQ15 |

GND |

CKE |

GND |

NC |

VCCQ |

DQ16 |

23 |

|

|

|

|

|

|

|

58 |

DQ1 |

N |

|

|

|

|

|

|

DQP2 |

24 |

|

|

|

|

|

|

|

57 |

NC |

|

|

|

|

|

|

NC |

25 |

|

|

|

|

|

|

|

56 |

NC |

|

DQ16 |

NC |

GND |

A1 |

GND |

DQ2 |

NC |

|

|

|

|

|

|

|

||||

GND |

26 |

|

|

|

|

|

|

|

55 |

GND |

|||||||

P |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

VCCQ |

27 |

|

|

|

|

|

|

|

54 |

VCCQ |

|

NC |

DQP2 |

GND |

A0 |

GND |

NC |

DQ1 |

|

|

|

|

|

|

|

||||

NC |

28 |

|

|

|

|

|

|

|

53 |

NC |

|||||||

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

NC |

29 |

|

|

|

|

|

|

|

52 |

NC |

|

NC |

A5 |

MODE |

VCC |

NC |

A13 |

NC |

NC |

30 |

|

|

|

|

|

|

|

51 |

NC |

T |

|

|

|

|

|

|

|

31 32 33 |

34 35 36 37 38 39 40 |

41 42 43 44 45 46 47 48 49 50 |

|

||||||

NC |

A10 |

A11 |

NC |

A14 |

NC |

ZZ |

|

|

|

|

|

|

|

|

|

|

|

U |

|

|

|

|

|

|

|

MODE |

A5 A4 |

A3 |

A2 A1 A0 NC |

NC GND |

VCC NC NC A11 A12 |

A13 |

A14 A15 A16 |

A17 |

|

VCCQ |

NC |

NC |

NC |

NC |

NC |

VCCQ |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

256K x 18 |

|

|

|

|

|

|

|

|

|

|

|

PIN DESCRIPTIONS

A0, A1 |

Synchronous Address Inputs. These |

|

pins must tied to the two LSBs of the |

|

address bus. |

|

|

A2-A17 |

Synchronous Address Inputs |

|

|

CLK |

Synchronous Clock |

|

|

ADV |

Synchronous Burst Address Advance |

|

|

BWa-BWb |

Synchronous Byte Write Enable |

|

|

WE |

Write Enable |

|

|

CKE |

Clock Enable |

|

|

CE, CE2, CE2 Synchronous Chip Enable

OE |

Output Enable |

|

|

DQ1-DQ16 |

Synchronous Data Input/Output |

|

|

MODE |

Burst Sequence Mode Selection |

|

|

VCC |

+3.3V Power Supply |

|

|

GND |

Ground |

|

|

VCCQ |

Isolated Output Buffer Supply: +3.3V/2.5V |

|

|

ZZ |

Snooze Enable |

|

|

DQP1-DQP2 |

Parity Data I/O DQP1 is parity for |

|

DQ1-8; DQP2 is parity for DQ9-16 |

|

|

Integrated Silicon Solution, Inc. — 1-800-379-4774 |

5 |

PRELIMINARY INFORMATION Rev. 00C

11/30/00

IS61NF12832 |

IS61NF12836 |

IS61NF25618 |

|

|

ISSI |

® |

|||||||||||||

IS61NLF12832 |

IS61NLF12836 |

IS61NLF25618 |

|

|

|

||||||||||||||

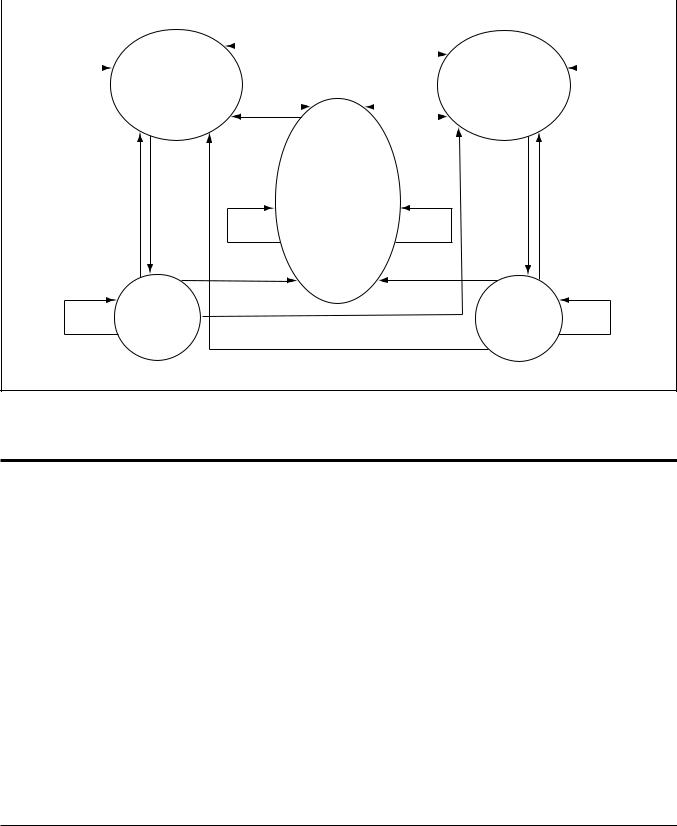

STATE DIAGRAM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

READ |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BEGIN |

|

|

|

|

WRITE |

|

|

|

|

|

|||||

|

READ |

|

|

|

BEGIN |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

READ |

|

|

DS |

|

|

|

DS |

WRITE |

WRITE |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

READ |

|

|

|

WRITE |

|

|

|

|

|

||

READ BURST |

|

DESELECT |

BURST WRITE |

|

|

||

|

DS |

|

BURST |

|

DS |

|

DS |

BURST |

WRITE |

|

BURST |

BURST |

|

|

BURST |

READ |

|

|

WRITE |

|

|

|

READ |

SYNCHRONOUS TRUTH TABLE(1)

|

Address |

|

|

|

|

|

|

|

|

|

Operation |

Used |

CS1 |

CS2 |

CS2 |

ADV |

WE |

BWx |

OE |

CKE |

CLK |

|

|

|

|

|

|

|

|

|

|

|

Not Selected Continue |

N/A |

X |

X |

X |

H |

X |

X |

X |

L |

↑ |

Begin Burst Read |

External Address |

L |

H |

L |

L |

H |

X |

L |

L |

↑ |

Continue Burst Read |

Next Address |

X |

X |

X |

H |

X |

X |

L |

L |

↑ |

NOP/Dummy Read |

External Address |

L |

H |

L |

L |

H |

X |

H |

L |

↑ |

Dummy Read |

Next Address |

X |

X |

X |

H |

X |

X |

H |

L |

↑ |

Begin Burst Write |

External Address |

L |

H |

L |

L |

L |

L |

X |

L |

↑ |

Continue Burst Write |

Next Address |

X |

X |

X |

H |

X |

L |

X |

L |

↑ |

|

|

|

|

|

|

|

|

|

|

|

NOP/Write Abort |

N/A |

L |

H |

L |

L |

L |

H |

X |

L |

↑ |

Write Abort |

Next Address |

X |

X |

X |

H |

X |

H |

X |

L |

↑ |

|

|

|

|

|

|

|

|

|

|

|

Ignore Clock |

Current Address |

X |

X |

X |

X |

X |

X |

X |

H |

↑ |

Notes:

1."X" means don't care.

2.The rising edge of clock is symbolized by ↑

3.A continue deselect cycle can only be entered if a deselect cycle is executed first.

4.WE = L means Write operation in Write Truth Table. WE = H means Read operation in Write Truth Table.

5.Operation finally depends on status of asynchronous pins (ZZ and OE).

6 Integrated Silicon Solution, Inc. — 1-800-379-4774

PRELIMINARY INFORMATION Rev. 00C

11/30/00

Loading...

Loading...