Intel ZT 7102 User Manual

Intel® NetStructure™ ZT 7102

Chassis Management Module

Technical Product Specification

August 2004

Order Number: 273770-017

Intel® NetStructure™ ZT 7102 Chassis Management Module

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800- 548-4725, or by visiting Intel's website at http://www.intel.com.

AlertVIEW, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Connect, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel XScale, IPLink, Itanium, LANDesk, LanRover, MCS, MMX, MMX logo, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, RemoteExpress, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside., The Journey Inside, TokenExpress, Trillium, VoiceBrick, Vtune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © Intel Corporation 2004.

2 |

Technical Product Specification |

|

|

|

Intel® NetStructure™ ZT 7102 Chassis Management Module |

|

|

|

|

|

Contents |

Contents |

|

|||

|

|

|

|

|

1.0 |

Introduction...................................................................................................................................... |

|

13 |

|

|

1.1 |

Overview............................................................................................................................. |

13 |

|

|

1.2 |

ZT 7102 Features ............................................................................................................... |

13 |

|

|

1.3 |

Terms Used in This Document ........................................................................................... |

15 |

|

2.0 |

Hardware Specifications.................................................................................................................... |

17 |

||

|

2.1 |

Overview............................................................................................................................. |

17 |

|

|

2.2 |

System Architecture............................................................................................................ |

18 |

|

|

2.3 |

Backplane Connections ...................................................................................................... |

18 |

|

|

|

2.3.1 |

Slot Connections.................................................................................................... |

18 |

|

|

2.3.2 |

Chassis Sensor Connections................................................................................. |

19 |

|

|

2.3.3 |

Chassis FRU Device Connections......................................................................... |

19 |

|

|

2.3.4 |

Redundancy........................................................................................................... |

19 |

|

2.4 |

Power Modules ................................................................................................................... |

19 |

|

|

2.5 |

Fan Modules ....................................................................................................................... |

19 |

|

|

2.6 |

Face Plate........................................................................................................................... |

20 |

|

|

|

2.6.1 |

Faceplate Features................................................................................................ |

21 |

|

2.7 |

Mechanical.......................................................................................................................... |

22 |

|

|

|

2.7.1 |

Board Dimensions and Weight .............................................................................. |

22 |

|

|

2.7.2 |

PCB Dimensions.................................................................................................... |

22 |

|

2.8 |

Connectors ......................................................................................................................... |

22 |

|

|

|

2.8.1 |

J1 Backplane Connector........................................................................................ |

24 |

|

|

2.8.2 |

J2 Backplane Connector........................................................................................ |

24 |

|

|

2.8.3 |

J3 Backplane Connector........................................................................................ |

25 |

|

|

2.8.4 |

Backplane Pin Descriptions ................................................................................... |

26 |

|

|

2.8.5 |

JA1 Ethernet Port .................................................................................................. |

27 |

|

|

2.8.6 |

J6 Serial Port ......................................................................................................... |

28 |

|

|

2.8.7 |

J7 Telco Alarm Connector ..................................................................................... |

28 |

|

2.9 |

Electrical and Environmental .............................................................................................. |

29 |

|

|

|

2.9.1 |

CMM Power ........................................................................................................... |

29 |

|

|

2.9.2 |

Power Ramp Circuitry ............................................................................................ |

30 |

|

|

2.9.3 |

Operating Temperature ......................................................................................... |

30 |

|

|

2.9.4 |

Reliability ............................................................................................................... |

30 |

|

|

2.9.5 |

Absolute Maximum Ratings ................................................................................... |

30 |

|

|

2.9.6 |

DC Operating Characteristics ................................................................................ |

31 |

|

2.10 |

Onboard Switches .............................................................................................................. |

31 |

|

|

|

2.10.1 |

Switch Descriptions ............................................................................................... |

32 |

|

|

|

2.10.1.1 S1 (Alarm Cutoff and Board Reset) ....................................................... |

32 |

|

|

|

2.10.1.2 SW1-1 (Password Reset) ...................................................................... |

32 |

|

2.11 |

Processor and Chipset ....................................................................................................... |

32 |

|

|

2.12 |

Memory |

............................................................................................................................... |

33 |

|

|

2.12.1 |

Removing the SODIMM ......................................................................................... |

33 |

|

|

2.12.2 |

Installing Memory................................................................................................... |

33 |

|

2.13 |

Flash ................................................................................................................................... |

|

33 |

|

2.14 |

Dual Ethernet Controllers ................................................................................................... |

33 |

|

|

2.15 |

Serial I/O............................................................................................................................. |

33 |

|

Technical Product Specification |

3 |

Intel® NetStructure™ ZT 7102 Chassis Management Module

Contents

|

2.16 |

Telco Alarm Signal.............................................................................................................. |

34 |

|

|

|

2.16.1 |

Alarm Relays ......................................................................................................... |

34 |

|

|

2.16.2 |

Opto Inputs ............................................................................................................ |

34 |

|

2.17 |

Real Time Clock ................................................................................................................. |

34 |

|

|

2.18 |

Network Time Synchronization ........................................................................................... |

34 |

|

|

2.19 |

Watchdog Timer ................................................................................................................. |

35 |

|

|

2.20 |

Battery Backup ................................................................................................................... |

35 |

|

|

|

2.20.1 |

Replacing the Battery ............................................................................................ |

35 |

|

2.21 |

Running Your System Without A CMM............................................................................... |

36 |

|

3.0 |

Software Specifications ..................................................................................................................... |

37 |

||

|

3.1 |

Operating System ............................................................................................................... |

37 |

|

|

3.2 |

Command Line Interface (CLI) ........................................................................................... |

37 |

|

|

3.3 |

SNMP/UDP......................................................................................................................... |

37 |

|

|

3.4 |

Remote Procedure Call (RPC) Interface ............................................................................ |

37 |

|

|

3.5 |

Ethernet Interfaces ............................................................................................................. |

37 |

|

|

3.6 |

Sensor Event Logs (SEL) ................................................................................................... |

38 |

|

|

|

3.6.1 |

CMM SEL Architecture .......................................................................................... |

38 |

|

|

3.6.2 |

Satellite Management Controller (SMC) Boards.................................................... |

38 |

|

|

3.6.3 |

Baseboard Management Controller (BMC) Boards ............................................... |

38 |

|

|

3.6.4 |

Retrieving a SEL.................................................................................................... |

38 |

4.0 CMM Redundancy, Synchronization and Failover ................................................................................ |

39 |

|||

|

4.1 |

Overview............................................................................................................................. |

39 |

|

|

4.2 |

Hardware Redundancy Specification.................................................................................. |

39 |

|

|

4.3 |

Synchronization .................................................................................................................. |

39 |

|

|

|

4.3.1 |

Synchronization Requirements.............................................................................. |

40 |

|

4.4 |

CMM Failover ..................................................................................................................... |

41 |

|

|

|

4.4.1 |

Scenarios That Force a Failover............................................................................ |

41 |

|

|

4.4.2 |

Scenarios That Prevent Failover ........................................................................... |

41 |

|

|

4.4.3 |

Scenarios That Failover to a Healthier Standby CMM........................................... |

41 |

|

|

4.4.4 |

Scenarios That Failover to an Equally Healthy CMM ............................................ |

42 |

|

|

4.4.5 |

Failover Timing ...................................................................................................... |

42 |

|

|

4.4.6 |

Manual Failover ..................................................................................................... |

42 |

5.0 CMM Installation and Removal .......................................................................................................... |

43 |

|||

|

5.1 |

Unpacking........................................................................................................................... |

43 |

|

|

5.2 |

Connectivity ........................................................................................................................ |

43 |

|

|

5.3 |

Installing the CMM .............................................................................................................. |

43 |

|

|

5.4 |

Removing the CMM ............................................................................................................ |

44 |

|

6.0 |

Built-In Self Test |

............................................................................................................................... |

47 |

|

|

6.1 |

BIST Test Flow ................................................................................................................... |

47 |

|

|

6.2 |

Boot-BIST ........................................................................................................................... |

48 |

|

|

6.3 |

Early-BIST .......................................................................................................................... |

48 |

|

|

6.4 |

Mid-BIST............................................................................................................................. |

48 |

|

|

6.5 |

Late-BIST............................................................................................................................ |

49 |

|

|

6.6 |

Event Log Area and Event Management............................................................................ |

49 |

|

|

6.7 |

OS Flash Corruption Detection and Recovery Design ....................................................... |

50 |

|

|

|

6.7.1 |

Monitoring the Static Images ................................................................................. |

50 |

|

|

6.7.2 |

Monitoring the Dynamic Images ............................................................................ |

50 |

4 |

Technical Product Specification |

Intel® NetStructure™ ZT 7102 Chassis Management Module

Contents

|

|

6.7.3 |

CMM Failover ........................................................................................................ |

50 |

|

|

6.8 |

BIST Test Descriptions ....................................................................................................... |

51 |

||

|

|

6.8.1 |

Flash Checksum Test ............................................................................................ |

51 |

|

|

|

6.8.2 |

Base Memory Test................................................................................................. |

51 |

|

|

|

6.8.3 |

Extended Memory Tests ........................................................................................ |

51 |

|

|

|

|

6.8.3.1 |

Walking Ones Test................................................................................. |

51 |

|

|

|

6.8.3.2 |

32-Bit Address Test ............................................................................... |

51 |

|

|

|

6.8.3.3 32-Bit Inverse Address Test................................................................... |

51 |

|

|

|

6.8.4 |

FPGA Version Check............................................................................................. |

52 |

|

|

|

6.8.5 |

DS1307 RTC Test ................................................................................................. |

52 |

|

|

|

6.8.6 |

NIC Presence/Local PCI Bus Test......................................................................... |

52 |

|

|

|

6.8.7 |

OS Image Checksum Test..................................................................................... |

52 |

|

|

|

6.8.8 |

CRC32 Checksum ................................................................................................. |

52 |

|

|

|

6.8.9 |

IPMB Bus Busy/Not Ready Test ............................................................................ |

52 |

|

7.0 CMM Connection and Setup .............................................................................................................. |

53 |

||||

|

7.1 |

CLI Overview ...................................................................................................................... |

|

53 |

|

|

7.2 |

Connecting to the CLI ......................................................................................................... |

53 |

||

|

|

7.2.1 |

Connecting through a Console .............................................................................. |

53 |

|

|

|

7.2.2 |

Telnet into the CMM .............................................................................................. |

53 |

|

|

|

7.2.3 |

FTP Into the CMM ................................................................................................. |

54 |

|

|

7.3 |

Initial Setup - Logging in for the First Time ......................................................................... |

54 |

||

|

|

7.3.1 |

Setting IP Address Properties................................................................................ |

54 |

|

|

|

|

7.3.1.1 Setting IP Information (IP Address, Netmask, and Gateway) ................ |

55 |

|

|

|

|

7.3.1.2 Setting Eth0 to DHCP ............................................................................ |

55 |

|

|

|

7.3.2 |

Setting a Hostname ............................................................................................... |

56 |

|

|

|

7.3.3 |

Setting Auto-Logout Time Limit ............................................................................. |

56 |

|

|

|

7.3.4 |

Rebooting the CMM ............................................................................................... |

56 |

|

8.0 |

Command Line Interface (CLI) Syntax and Arguments.......................................................................... |

57 |

|||

|

8.1 |

cmmget and cmmset syntax ............................................................................................... |

57 |

||

|

8.2 |

Help Parameter: -h ............................................................................................................. |

57 |

||

|

8.3 |

Location Parameter: -l ........................................................................................................ |

57 |

||

|

8.4 |

Target Parameter: -t ........................................................................................................... |

58 |

||

|

8.5 |

Dataitem Parameter: -d ...................................................................................................... |

58 |

||

|

8.6 |

Value Parameter: -v............................................................................................................ |

61 |

||

|

8.7 |

Sample CLI Operations ...................................................................................................... |

61 |

||

|

8.8 |

Generating a System Status Report ................................................................................... |

62 |

||

9.0 |

Resetting the Password .................................................................................................................... |

|

63 |

||

|

9.1 |

Resetting the Password in a Single CMM System ............................................................. |

63 |

||

|

9.2 |

Resetting the Password in a Dual CMM System ................................................................ |

63 |

||

10.0 |

Sensor Types................................................................................................................................... |

|

|

65 |

|

|

10.1 |

Threshold-Based Sensors .................................................................................................. |

65 |

||

|

|

10.1.1 |

Threshold-Based Sensor Events ........................................................................... |

65 |

|

|

10.2 |

Discrete Sensors ................................................................................................................ |

|

65 |

|

|

|

10.2.1 |

Discrete Sensor Events ......................................................................................... |

65 |

|

11.0 |

Health Event Strings ......................................................................................................................... |

|

67 |

||

|

11.1 |

Syntax of Health Event Strings ........................................................................................... |

67 |

||

Technical Product Specification |

5 |

Intel® NetStructure™ ZT 7102 Chassis Management Module

Contents

|

|

11.1.1 “healthevents” Query Event Syntax ....................................................................... |

67 |

|

|

|

11.1.2 |

SEL Event Syntax .................................................................................................. |

67 |

|

|

11.1.3 SNMP Trap Event Syntax...................................................................................... |

68 |

|

|

11.2 |

Sensor Targets ................................................................................................................... |

|

68 |

|

11.3 |

Healthevents Queries ......................................................................................................... |

69 |

|

|

|

11.3.1 HealthEvents Queries for Individual Sensors ........................................................ |

69 |

|

|

|

11.3.2 HealthEvents Queries for All Sensors on a Location............................................. |

69 |

|

|

|

11.3.3 |

No Active Events ................................................................................................... |

69 |

|

|

11.3.4 Not Present or Non-IPMI Locations ....................................................................... |

70 |

|

|

11.4 |

List of Possible Health Event Strings.................................................................................. |

70 |

|

|

|

11.4.1 |

All Locations .......................................................................................................... |

71 |

|

|

11.4.2 PowerSupplyN Location (IPMI-Compliant Supplies Only) ..................................... |

71 |

|

|

|

11.4.3 |

CMM Location ........................................................................................................ |

72 |

|

|

11.4.4 |

Chassis Location ................................................................................................... |

73 |

12.0 |

Slot Power Control............................................................................................................................ |

|

77 |

|

|

12.1 |

Difference between a Board’s HEALTHY# Signal and a Board’s Health ........................... |

77 |

|

|

12.2 |

Slot Power-Up Sequence ................................................................................................... |

77 |

|

|

|

12.2.1 |

Assertion of BD _ SEL# ........................................................................................... |

77 |

|

|

|

System Master Boards........................................................................... |

77 |

|

|

|

Peripheral Boards .................................................................................. |

77 |

|

|

|

12.2.1.3 Fabric and PCI - Less Slots ..................................................................... |

78 |

|

|

|

Drone Mode Boards............................................................................... |

78 |

|

|

12.2.2 Assertion of HEALTHY# During Power-Up............................................................ |

78 |

|

|

12.3 |

Obtaining the Power State of a Board ................................................................................ |

78 |

|

|

12.4 |

Controlling the Power State of a Slot.................................................................................. |

79 |

|

|

|

12.4.1 Powering Off a Board ............................................................................................ |

79 |

|

|

|

12.4.2 Powering On a Board ............................................................................................ |

79 |

|

|

|

12.4.3 |

Resetting a Board .................................................................................................. |

79 |

|

12.5 |

Power Sequencing Commands and Policies...................................................................... |

79 |

|

|

|

12.5.1 Retrieving the Healthy# Ramp-Up Time ................................................................ |

80 |

|

|

|

12.5.2 Setting the Healthy# Ramp-Up Time ..................................................................... |

80 |

|

|

|

12.5.3 Retrieving the Maximum Power-Up Attempts........................................................ |

80 |

|

|

|

12.5.4 Setting the Maximum Power-Up Attempts............................................................. |

80 |

|

|

|

12.5.5 Power Sequencing SEL Events............................................................................. |

81 |

|

13.0 |

Power Supplies |

|

83 |

|

|

13.1 |

Power Supply .....................................................................................................Detection |

83 |

|

|

13.2 |

Inhibit, Degrade, .......................................................................................and Fail Signals |

83 |

|

|

13.3 |

Inhibiting ...................................................................................................Power Supplies |

83 |

|

|

13.4 |

Precautions .........................................................................For Inhibiting Power Supplies |

83 |

|

|

13.5 |

Inhibiting ...................................................................................................Power Supplies |

84 |

|

|

13.6 |

Enabling ....................................................................................................Power Supplies |

84 |

|

14.0 Drone Mode SBC .................................................................................................................Support |

|

85 |

||

|

|

14.0.1 .....................................................................Adding a Drone Mode Capable SBC |

85 |

|

|

|

14.0.2 ................................................................Removing a Drone Mode Capable SBC |

85 |

|

15.0 Active vs. Offline ......................................................................................................................Slots |

|

87 |

||

|

15.1 |

Determining ...........................................................................................the State of a Slot |

87 |

|

|

15.2 |

Setting .............................................................................................a Slot to Offline Mode |

87 |

|

6 |

Technical Product Specification |

Intel® NetStructure™ ZT 7102 Chassis Management Module

Contents

|

15.3 |

Setting a Slot to Active Mode .............................................................................................. |

87 |

|

15.4 |

Limitations of the Offline Mode ........................................................................................... |

87 |

16.0 |

Obtaining FRU Information ................................................................................................................ |

89 |

|

|

16.1 |

FRU Information ................................................................................................................. |

89 |

|

16.2 |

FRU Query Syntax .............................................................................................................. |

89 |

|

16.3 |

Chassis FRU Validity Check ............................................................................................... |

90 |

17.0 Fan Control and Monitoring ............................................................................................................... |

91 |

||

|

17.1 |

Setting Fan Speed .............................................................................................................. |

91 |

|

|

17.1.1 Considerations for Turning Off the Fans ................................................................ |

91 |

|

17.2 |

Automatic Fan Control ........................................................................................................ |

91 |

|

17.3 |

Querying Fan Tray Sensors ................................................................................................ |

92 |

18.0 |

CMM Scripting ................................................................................................................................. |

93 |

|

|

18.1 |

CLI Scripting ....................................................................................................................... |

93 |

|

|

18.1.1 Script Synchronization ........................................................................................... |

93 |

|

18.2 |

Associating Scripts to Event Severity ................................................................................. |

93 |

|

|

18.2.1 Listing Scripts Associated With Events .................................................................. |

94 |

|

|

18.2.2 Removing Scripts From an Associated Event ........................................................ |

94 |

|

18.3 |

Setting Scripts for Specific Individual Events ...................................................................... |

94 |

|

|

18.3.1 Event Codes .......................................................................................................... |

94 |

|

18.4 |

Setting Event Scripts .......................................................................................................... |

95 |

|

18.5 |

Slot Events .......................................................................................................................... |

95 |

19.0 |

SNMP |

............................................................................................................................................. |

97 |

|

19.1 ............................................................................................................................ |

CMM MIB |

98 |

|

19.2 ......................................................................................................................... |

MIB Design |

98 |

|

.................................................................................................. |

19.2.1 CMM MIB Objects |

98 |

|

.................................. |

19.2.2 Querying Non - IPMI Compliant Blades and Power Supplies |

98 |

|

19.3 ....................................................................................................................... |

SNMP Agent |

98 |

|

......................................................................... |

19.3.1 Configuring the SNMP Agent Port |

99 |

|

.................................... |

19.3.2 Configuring the Agent to Respond to SNMP v3 Requests |

99 |

|

............................................................... |

19.3.3 Configuring the Agent Back to SNMP v1 |

99 |

|

.................................................................... |

19.3.4 Setting up an SNMP v3 MIB Browser |

99 |

|

19.4 ............................................................................................................. |

SNMP Trap Utility |

100 |

|

......................................................................... |

19.4.1 Configuring the SNMP Trap Port |

100 |

|

................................................... |

19.4.2 Configuring the CMM to Send SNMP v3 Traps |

100 |

|

................................................... |

19.4.3 Configuring the CMM to Send SNMP v1 Traps |

100 |

|

19.5 ............................................................ |

Configuring and Enabling SNMP Trap Addresses |

100 |

|

.................................................................... |

19.5.1 Configuring an SNMP Trap Address |

100 |

|

................................................................... |

19.5.2 Enabling and Disabling SNMP Traps |

100 |

|

.......................................................................................... |

19.5.3 Alerts Using SNMPv3 |

101 |

|

.......................................................................................... |

19.5.4 Alert Using UDP Alert |

101 |

|

19.6 .................................................................................................................. |

Security Model |

101 |

|

........................ |

19.6.1 SNMPv3 Security: Authentication Protocol and Privacy Protocol |

101 |

|

19.7 ....................................................................................................................... |

snmpd.conf |

101 |

20.0 |

RPC.............................................................................................................................................. |

|

103 |

|

20.1 ........................................................................................... |

Setting Up the RPC Interface |

103 |

|

20.2 ................................................................................................... |

Using the RPC Interface |

103 |

Technical Product Specification |

7 |

Intel® NetStructure™ ZT 7102 Chassis Management Module

Contents

|

|

20.2.1 |

GetAuthCapability() ............................................................................................. |

104 |

|

|

|

20.2.2 |

ChassisManagementApi() ................................................................................... |

104 |

|

|

|

20.2.3 |

ChassisManagementApi() Threshold Response Format..................................... |

109 |

|

|

|

20.2.4 |

ChassisManagementApi() String Response Format ........................................... |

110 |

|

|

|

20.2.5 |

ChassisManagementApi() Integer Response Format.......................................... |

113 |

|

|

|

20.2.6 |

FRU String Response Format ............................................................................. |

114 |

|

|

20.3 |

RPC Sample Code ........................................................................................................... |

115 |

||

|

20.4 |

RPC Usage Examples ...................................................................................................... |

115 |

||

21.0 |

Command Logging ......................................................................................................................... |

|

119 |

||

22.0 |

Telco Alarm Sensors ...................................................................................................................... |

|

121 |

||

|

22.1 |

Configuring the Telco Alarm Connector Pins.................................................................... |

121 |

||

|

22.2 |

Obtaining the Configuration of the Telco Alarm Sensor Connector Pins.......................... |

121 |

||

|

22.3 |

Telco Alarm Connector Sensor Naming ........................................................................... |

121 |

||

|

|

22.3.1 |

Sensor Names using SNMP ................................................................................ |

122 |

|

|

22.4 |

Telco Alarm Sensors and Redundancy ............................................................................ |

122 |

||

23.0 |

Application Hosting......................................................................................................................... |

|

123 |

||

|

23.1 |

System Details.................................................................................................................. |

|

123 |

|

|

23.2 |

Startup and Shutdown Scripts .......................................................................................... |

123 |

||

|

23.3 |

System Resources Available to User Applications ........................................................... |

123 |

||

|

|

23.3.1 |

File System Storage Constraints ......................................................................... |

123 |

|

|

|

|

23.3.1.1 |

Flash Storage Locations ...................................................................... |

123 |

|

|

|

23.3.1.2 |

RAM-Disk Storage Locations............................................................... |

124 |

|

|

23.3.2 |

RAM Constraints.................................................................................................. |

124 |

|

|

|

23.3.3 |

Interrupt Constraints ............................................................................................ |

124 |

|

|

23.4 |

Ram Disk Directory Structure ........................................................................................... |

124 |

||

24.0 |

Busless Backplane Support |

............................................................................................................. |

125 |

||

25.0 |

Updating Software .......................................................................................................................... |

|

127 |

||

|

25.1 |

Key Features of the Firmware Update Process................................................................ |

127 |

||

|

25.2 |

Update Process Architecture ............................................................................................ |

127 |

||

|

25.3 |

Critical Software Update Files and Directories ................................................................. |

128 |

||

|

25.4 |

Update Package ............................................................................................................... |

|

128 |

|

|

|

25.4.1 |

Update Package File Validation........................................................................... |

129 |

|

|

|

25.4.2 |

Update Firmware Package Version ..................................................................... |

129 |

|

|

|

25.4.3 |

Component Versioning ........................................................................................ |

130 |

|

|

25.5 |

saveList and Data Preservation........................................................................................ |

130 |

||

|

25.6 |

Update Mode .................................................................................................................... |

|

131 |

|

|

25.7 |

Update_Metadata File ...................................................................................................... |

131 |

||

|

25.8 |

Synchronization ................................................................................................................ |

|

132 |

|

|

|

25.8.1 |

Updating to a Newer Synchronization Version .................................................... |

132 |

|

|

|

25.8.2 |

Updating to an Older Synchronization Version.................................................... |

132 |

|

|

|

25.8.3 |

Updating to the Same Synchronization Version .................................................. |

133 |

|

|

25.9 |

Single CMM System ......................................................................................................... |

133 |

||

|

25.10 |

Redundant CMM Systems................................................................................................ |

133 |

||

|

25.11 |

CLI Support....................................................................................................................... |

|

133 |

|

|

25.12 |

Hooks for User Scripts...................................................................................................... |

134 |

||

|

|

25.12.1 Update Mode User Scripts................................................................................... |

134 |

||

8 |

Technical Product Specification |

Intel® NetStructure™ ZT 7102 Chassis Management Module

Contents

25.12.2 Data Restore User Scripts. .................................................................................. |

134 |

25.12.3Example Task - Replace /home/scripts/myScript with a newer version if updating forward or an older version if updating backward135

|

25.13 |

Update Process ................................................................................................................ |

136 |

|

|

25.14 |

Update Process Status and Logging ................................................................................ |

137 |

|

|

25.15 |

DEBUG_UPDATE Variable .............................................................................................. |

137 |

|

|

25.16 |

Update Process Sensor and SEL Events ......................................................................... |

137 |

|

|

25.17 |

RedBoot Update Process ................................................................................................. |

138 |

|

|

|

25.17.1 Required Setup .................................................................................................... |

138 |

|

|

|

25.17.2 Update Procedure................................................................................................ |

138 |

|

D |

Example CLI Commands................................................................................................................. |

139 |

||

E |

Datasheet Reference ...................................................................................................................... |

141 |

||

|

E.1 |

Intel® CompactPCI* Product Information ......................................................................... |

141 |

|

|

E.2 |

CompactPCI ..................................................................................................................... |

141 |

|

|

E.3 |

IPMI .................................................................................................................................. |

|

141 |

|

E.4 |

Intel® |

IOP310 Processor Chipset ..................................................................................... |

141 |

F |

Warranty Information ...................................................................................................................... |

143 |

||

|

F.1 |

Intel® |

NetStructure™ Compute Boards & Platform Products |

|

|

|

Limited Warranty143 |

|

|

|

|

F.1.1 Returning a Defective Product (RMA).................................................................. |

143 |

|

|

|

F.1.2 |

For the Americas ................................................................................................. |

143 |

|

|

F.1.3 |

For EMEA ............................................................................................................ |

144 |

|

|

F.1.4 |

For APAC............................................................................................................. |

144 |

G |

Customer Support .......................................................................................................................... |

147 |

||

|

G.2 |

Technical Support and Return for Service Assistance ..................................................... |

147 |

|

|

G.3 |

Sales Assistance .............................................................................................................. |

147 |

|

H |

Agency Approvals........................................................................................................................... |

149 |

||

|

H.1 |

CE Certification................................................................................................................. |

149 |

|

|

H.2 |

Safety................................................................................................................................ |

149 |

|

|

H.3 |

Emissions Test Regulations ............................................................................................. |

149 |

|

|

|

H.3.5 |

EN 50081-1 Emissions ........................................................................................ |

149 |

|

|

H.3.6 |

EN 55024 Immunity ............................................................................................. |

149 |

|

H.4 |

Regulatory Information ..................................................................................................... |

150 |

|

|

|

H.4.7 |

FCC (USA)........................................................................................................... |

150 |

|

|

H.4.8 |

Industry Canada (Canada) .................................................................................. |

150 |

|

H.5 |

Product Safety Information ............................................................................................... |

150 |

|

Figures |

|

|

|

|

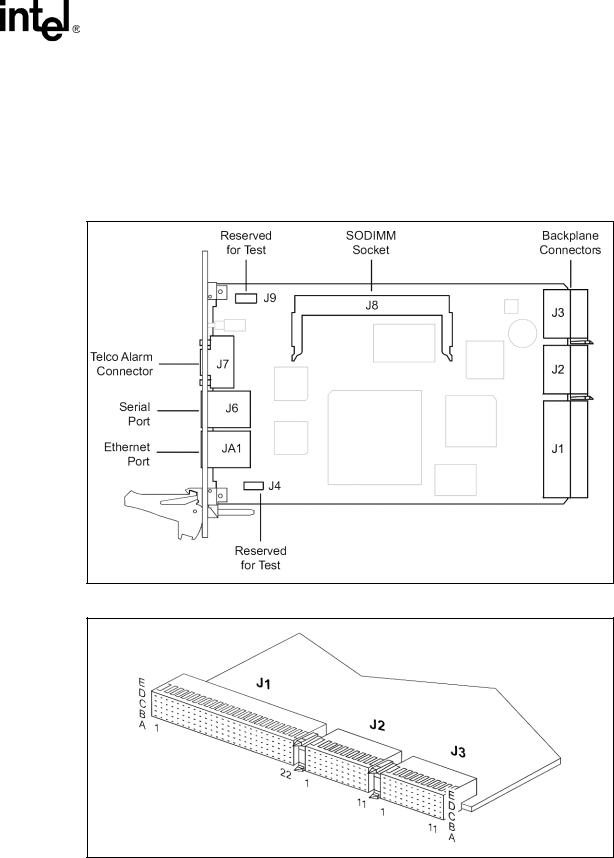

1 |

Functional Block Diagram........................................................................................................... |

14 |

||

2 |

System Management Architecture.............................................................................................. |

18 |

||

3 |

Face Plate................................................................................................................................... |

|

20 |

|

4 |

PCB Dimensions......................................................................................................................... |

22 |

||

5 |

Connector Locations................................................................................................................... |

23 |

||

6 |

Backplane Connectors - Pin Locations....................................................................................... |

23 |

||

7 |

Default Switch Configuration ...................................................................................................... |

31 |

||

8 |

Ejector Handle Operation ........................................................................................................... |

44 |

||

Technical Product Specification |

9 |

Intel® NetStructure™ ZT 7102 Chassis Management Module

Contents

9 |

BIST Flow Chart ......................................................................................................................... |

47 |

10 |

Timing of BIST Stages................................................................................................................ |

49 |

11 |

High Level SNMP/MIB Layout .................................................................................................... |

97 |

Tables |

|

|

1 |

Glossary ..................................................................................................................................... |

15 |

2 |

Faceplate Features..................................................................................................................... |

21 |

3 |

Board Dimensions and Weight ................................................................................................... |

22 |

4 |

Connector Assignments ............................................................................................................. |

22 |

5 |

J1 Connector Pinout ................................................................................................................... |

24 |

6 |

J2 Connector Pinout ................................................................................................................... |

25 |

7 |

J3 Connector Pinout ................................................................................................................... |

25 |

8 |

Pin Type Definitions.................................................................................................................... |

26 |

9 |

Pin Descriptions.......................................................................................................................... |

26 |

10 |

JA1 Ethernet Port Pinout ............................................................................................................ |

28 |

11 |

J6 Serial Port Pinout................................................................................................................... |

28 |

12 |

J7 Telco Alarm Connector Pinout............................................................................................... |

29 |

13 |

CMM Power Availability.............................................................................................................. |

29 |

14 |

Absolute Maximum Ratings........................................................................................................ |

30 |

15 |

DC Operating Characteristics..................................................................................................... |

31 |

16 |

Switch Cross Reference Table ................................................................................................... |

31 |

17 |

SW1-1 Functions ........................................................................................................................ |

32 |

18 |

Battery Characteristics ............................................................................................................... |

35 |

19 |

CMM Synchronization ................................................................................................................ |

40 |

20 |

BIST Implementation .................................................................................................................. |

48 |

21 |

Location (-l) Keywords................................................................................................................ |

57 |

22 |

Target (-t) Keywords................................................................................................................... |

58 |

23 |

dataitem (-d) Keywords for All Locations.................................................................................... |

58 |

24 |

dataitem (-d) Keywords for System location............................................................................... |

59 |

25 |

dataitem (-d) Keywords for BladeN Locations ............................................................................ |

59 |

26 |

dataitem (-d) Keywords for Chassis Location............................................................................. |

60 |

27 |

dataitem (-d) Keywords for CMM Location ................................................................................. |

60 |

28 |

CMM Sensor Targets ................................................................................................................. |

68 |

29 |

Threshold-Based Sensor Event Strings (Voltage, Temp, Current, Fan) .................................... |

71 |

30 |

Power Supply Event Strings (PowerSupplyN)............................................................................ |

71 |

31 |

BIST Event Strings (BIST).......................................................................................................... |

72 |

32 |

Telco Alarm Sensor Event Strings (TASensor[1,2]) ................................................................... |

73 |

33 |

LAN Sensor Event Strings (Eth[0,1,1:1] Interface) ..................................................................... |

73 |

34 |

Fan Tray Presence Event Strings (Fan Tray [1-3] Presence) .................................................... |

73 |

35 |

Chassis Power Supply Event Strings (Pwr Supply N) ................................................................ |

73 |

36 |

Slot Event Strings (Slot N Event)................................................................................................ |

74 |

37 |

CMM Redundancy Event Strings (CMM [1-2] Redundancy) ...................................................... |

74 |

38 |

CMM Failover Event Strings (CMM Failover) ............................................................................. |

74 |

39 |

CMM File Sync Event Strings (CMM File Sync) ......................................................................... |

75 |

40 |

Chassis Sensor Event Strings .................................................................................................... |

75 |

41 |

Dataitems Used With FRU Target (-t) to Obtain FRU Information ............................................. |

89 |

42 |

MIB II Objects - System Group................................................................................................... |

98 |

43 |

MIB II - Interface Group .............................................................................................................. |

98 |

44 |

SNMPv3 Security Fields........................................................................................................... |

101 |

45 |

Error and Return Codes for the RPC Interface......................................................................... |

106 |

10 |

Technical Product Specification |

Intel® NetStructure™ ZT 7102 Chassis Management Module

Contents

46 |

Threshold Response Formats .................................................................................................. |

110 |

47 |

String Response Formats ......................................................................................................... |

110 |

48 |

Integer Response Formats ....................................................................................................... |

113 |

49 |

FRU Data Items String Response Format ................................................................................ |

114 |

50 |

RPC Usage Examples .............................................................................................................. |

116 |

51 |

List of Critical Software Update Files and Directories............................................................... |

128 |

52 |

Contents of the Update Package.............................................................................................. |

128 |

53 |

saveList Items and Their Priorities............................................................................................ |

130 |

54 |

Synchronization Behavior for Differing Synch Versions ........................................................... |

132 |

55 |

Example CLI Commands.......................................................................................................... |

139 |

Technical Product Specification |

11 |

Intel® NetStructure™ ZT 7102 Chassis Management Module

Contents

Revision History

Date |

Revision |

Description |

|

|

|

|

|

|

|

Changes related to V4.11h firmware |

|

|

|

Added new BIST events for RTC and FRU checking. |

|

August 2004 |

017 |

Added new Chassis Slot event for IPMI capable |

|

|

|

Added information on /etc/version checking |

|

|

|

Added infomation on chassis FRU validity checking. |

|

|

|

|

|

April 2004 |

016 |

Changes related to V4.11c firmware |

|

Added rdate feature information |

|||

|

|

||

|

|

|

|

March 2004 |

015 |

Changes related to V4.11b frimware verison |

|

|

|

|

|

|

|

Changes related to V4.11a firmware version |

|

March 2004 |

014 |

Changes to Software Update section |

|

Slotcontrol description |

|||

|

|

||

|

|

Changes to Heatlh Event Strings |

|

|

|

|

|

|

|

Changes related to V4.0x firmware version |

|

|

|

New Password Reset Implementation |

|

October 2003 |

010 |

PSInhibit |

|

|

|

Power Sequencing Policies |

|

|

|

Updated Warranty and Customer Support information. |

|

|

|

|

|

April 2003 |

005 |

V3.00a Release |

|

|

|

|

12 |

Technical Product Specification |

Intel® NetStructureTMZT 7102 Chassis Management Module

Introduction

1.0Introduction

1.1Overview

The Intel® NetStructureTM ZT 7102 is a 3U, single-slot Chassis Management Module (CMM) intended for use with PICMG* 2.1, 2.16, and 2.9-compliant systems (the CompactPCI* Hot Swap, Packet Switching Backplane, and System Management specifications, respectively). This document details the features and specifications of the ZT 7102.

The ZT 7102 plugs into a dedicated slot in compatible systems. It provides centralized management and alarming for up to 21 node and/or fabric slots as well as for system power supplies and fans. The ZT 7102 may be paired with a backup for use in high-availability applications.

The ZT 7102 is a special purpose single board computer with its own CPU, memory, PCI bus, operating system, and peripherals. The ZT 7102 monitors and configures Intelligent Platform Management Interface (IPMI)-based components in the chassis. When thresholds such as temperature and voltage are crossed or a failure occurs, the CMM captures these events, stores them in an event log, sends SNMP traps, and drives the Telco alarm relays and alarm LEDs. The CMM can query FRU information (such as serial number, model number, manufacture date, etc.), detect presence of components (such as fan tray, CPU board, etc.), and perform health monitoring of each component. In addition, the CMM controls the power-up sequencing of each node board and the power to each slot via the BD_SEL# signal.

The ZT 7102 can also be used at a limited degree to manage non-IPMI based chassis components.

1.2ZT 7102 Features

•High-density 3U X 1-slot form factor

•Compatible with PICMG* 2.1, 2.16, and 2.9-compliant chassis and components

•Monitors via the Intelligent Platform Management Bus (IPMB) protocol

•Provides isolated IPMB signals for each slot for maximum security and reliability

•Manage through the command line interface, SNMP v1/v3, or Remote Procedure Call (RPC)

•Hot-add/hot-swap support for IPMI-based, field-replaceable components

•µDB15 Telco Alarm Interface at the front panel

•Critical, Major, and Minor alarm LEDs at the front panel

•CMM status and hot swap LEDs at the front panel

•Monitors backplane voltages and status for up to eight power supplies

•Monitors system temperature sensors

•Monitors system fan tray presence

•Monitors tachometers for up to 16 system fans

•Monitors sensors on PICMG 2.9 compliant single board computers

•Power state control for single board compute blades

Technical Product Specification |

13 |

Intel® NetStructureTMZT 7102 Chassis Management Module

Introduction

Figure 1. Functional Block Diagram

|

|

|

|

|

|

|

|

|

66 |

||

|

|||||

|

! |

|

|

||

|

|

|

|||

|

|

|

|

! |

|

|

|

|

' "/ |

||

( 7 3 |

|

(& ! 0 1 |

|

( !* |

|

8 9 , 3 |

!* "/+ |

|

/ !+ |

||

9 : ,, 3 |

|

|

|

||

* !* ! + |

|

|

|

||

|

|

"!# |

|

2 % |

|

|

|

$ # |

|

& |

|

% 2 |

|

% |

|||

% |

|

||||

(& ! |

3 |

|

|

||

|

|

||||

.%3 4 ) 3+ |

|

||||

|

|

|

|

5% |

|

|

|

|

|

/ "%% |

|

|

|

& ' |

|

|

|

. * ) |

(" !) ! |

|

|

||

|

|

!* |

|

|

|

|

! + |

|

|

||

|

|

|

|

||

|

|

|

|

|

|

. . |

|

|

|

||

,- , ! ! |

|

||||

|

|

||||

; / ! !* -!* - * , , 6 : |

|

||||

|

|

|

|

|

|

14 |

Technical Product Specification |

Intel® NetStructureTMZT 7102 Chassis Management Module

Introduction

1.3Terms Used in This Document

Table 1. Glossary

Acronym |

Description |

|

|

CMM |

Chassis Management Module |

|

|

CLI |

Command Line Interface |

|

|

FRU |

Field Replaceable Unit |

|

|

IPMI |

Intelligent Platform Management Interface |

|

|

IPMB |

Intelligent Platform Management Bus |

|

|

MIB |

Management Information Base |

|

|

MIB II |

RFC1213 - A standard Management Information Base for Network Management |

|

|

SEL |

System Event Log |

|

|

SBC |

Single Board Computer |

|

|

SNMP |

Simple Network Management Protocol |

|

|

SNMP v.1 |

SNMP version 1 |

|

|

SNMP v.3 |

SNMP version 3 |

|

|

SDR |

Sensor Data Record |

|

|

Technical Product Specification |

15 |

Intel® NetStructureTMZT 7102 Chassis Management Module

Introduction

16 |

Technical Product Specification |

Intel® NetStructureTMZT 7102 Chassis Management Module

Hardware Specifications

2.0Hardware Specifications

2.1Overview

The chassis management module (CMM) is intended to operate as a chassis management building block in a CompactPCI chassis. The CMM uses a unique backplane interface pinout and requires a dedicated slot within the chassis.

Caution: The ZT 7102 plugs into a dedicated chassis management slot. System components will be damaged if a standard 3U board is plugged into the chassis management slot.

Intelligent Platform Management Buses (IPMBs) are the primary management connection between components. A unique star topology radiating from the CMMs is used to provide reliability, flexibility and security. In some cases, direct logic is used to support non-intelligent devices and to eliminate active components on the backplane and chassis.

The CMM provides 30 master/slave two-wire serial bus (2WSB) interfaces. The 2WSBs are electrically equivalent to I2C*. As such, all outputs are open drain, so they are driven low and passively pulled high. The 2WSB interfaces support multi-master operation on the bus, however they do not support being the target of a read transaction from another master device. The 2WSB interfaces are used by the CMM as IPMBs or non-intelligent management busses. Refer to the individual sections for specific usage information. The 2WSB interfaces are used for:

•Up to 21 general-purpose slots (21 independent 2WSBs, 2WSB_S0 - 2SB_S20)

•Power supplies (two buses, 2WSB_PS0 and 2WSB_PS1)

•Fan trays (one bus, 2WSB_FT)

•Chassis sensors (one bus, 2WSB_CS)

•Chassis FRU modules (two independent buses, 2WSB_CF0 and 2WSB_CF1)

•Redundant CMM link (one bus for bi-directional communication, 2WSB_RCMM)

Technical Product Specification |

17 |

Intel® NetStructureTMZT 7102 Chassis Management Module

Hardware Specifications

2.2System Architecture

Figure 2. System Management Architecture

2.3Backplane Connections

2.3.1Slot Connections

The slots are connected to the CMM via an IPMB defined in the PICMG* 2.9 specification. The CMM also has connections for BD_SEL# and HEALTHY# signals to each slot. Each slot has an independent IPMB, BD_SEL#, and HEALTHY#. The CMM supports up to 21 general-purpose node slots.

The IPMB is used for IPMI management communication between the CMM and the board in the slot. Each board that is to be managed by the CMM is required to support the IPMB as a management channel.

BD_SEL# is used in CompactPCI slots to control board power and to detect board presence. The CMM provides a bi-directional open drain driver for each BD_SEL#. The board installed in the slot provides a pull-up resistor (1.2 KΩ ± 5% per PICMG* 2.0). The CMM provides a weak pulldown resistor (and a diode clamp). When not asserted, BD_SEL# can be read to determine if a board is present in the slot. If BD_SEL# is high, a board is present. If BD_SEL# is not asserted a board is not present. Asserting BD_SEL# allows the board to power up.

HEALTHY# is an input to the CMM. The CMM provides a pull-up resistor. The board in the slot asserts HEALTHY# based on board power being good and optionally other board-specific requirements. BD_SEL# must be asserted for HEALTHY# to be asserted. When BD_SEL# is asserted, and a board is removed, HEALTHY# will be deasserted.

18 |

Technical Product Specification |

Intel® NetStructureTMZT 7102 Chassis Management Module

Hardware Specifications

2.3.2Chassis Sensor Connections

Chassis sensors are connected to the CMM via one two-wire serial bus.

2.3.3Chassis FRU Device Connections

Chassis sensors are connected to the CMM via one two-wire serial bus. The CMM provides two 2WSB interfaces for chassis FRU modules. Each chassis FRU module is on a dedicated 2WSB in order to provide redundant access to vital chassis information (e.g., the physical location of the chassis). The backplane FRU storage device used MUST be an Atmel* AT24C16 or other 24C16-compatible device.

2.3.4Redundancy

The CMM supports redundant operation with automatic failover under hardware or software control. The following hardware interfaces exist for the support of redundancy and automatic failover:

•Cross-connected CMM present inputs (PRES_I#) and outputs (PRES_O#)

•Cross-connected CMM healthy inputs (HLY_I#) and outputs (HLY_O#)

•Cross-connected negotiation inputs (NEG_I) and outputs (NEG_O)

The active CMM monitors its PRES_I# and HLY_I# inputs to determine if it has a healthy, standby CMM. The active CMM deasserts its HLY_O# output to trigger a failover to the standby CMM.

The cross-connected negotiation signals are used to assure that only one CMM is active at a time. At anytime, the standby CMM can trigger a failover by driving its NEG_O output low.

2.4Power Modules