ICSI IC61LV256-10J, IC61LV256-10JI, IC61LV256-10T, IC61LV256-10TI, IC61LV256-12J Datasheet

...

IC61LV256

Document Title

32K x 8 Hight Speed SRAM with 3.3V

Revision History

Revision No |

History |

Draft Date |

Remark |

0A |

Initial Draft |

April 19,2002 |

|

The attached datasheets are provided by ICSI. Integrated Circuit Solution Inc reserve the right to change the specifications and products. ICSI will answer to your questions about device. If you have any questions, please contact the ICSI offices.

Integrated Circuit Solution Inc. |

1 |

AHSR027-0A 04/19/2002

IC61LV256

32K x 8 HIGH SPEED CMOS STATIC RAM

FEATURES

•High-speed access times:

--8, 10, 12, 15 ns

•Automatic power-down when chip is deselected

•CMOS low power operation

--345 mW (max.) operating

--7 mW (max.) CMOS standby

•TTL compatible interface levels

•Single 3.3V power supply

•Fully static operation: no clock or refresh required

•Three-state outputs

DESCRIPTION

The ICSI IC61LV256 is a very high-speed, low power, 32,768-word by 8-bit static RAM. It is fabricated using ICSI's high-performance CMOS technology. This highly reliable process coupled with innovative circuit design techniques, yields access times as fast as 8 ns maximum.

When CE is HIGH (deselected), the device assumes a standby mode at which the power dissipation is reduced to 600 µW (typical) with CMOS input levels.

Easy memory expansion is provided by using an active LOW Chip Enable (CE). The active LOW Write Enable (WE) controls both writing and reading of the memory.

The IC61LV256 is available in the JEDEC standard 28-pin, 300mil SOJ and the 8*13.4mm TSOP-1 package.

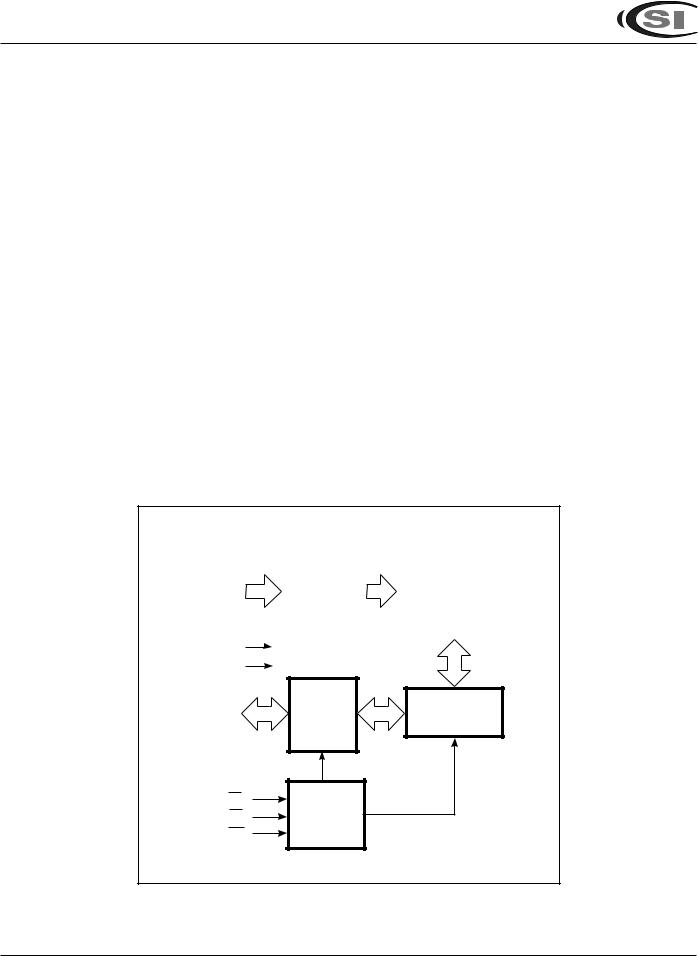

FUNCTIONAL BLOCK DIAGRAM

A0-A14 |

DECODER |

|

256 X 1024 |

|

MEMORY ARRAY |

||

|

|

|

|

|

|

|

|

VCC

GND

I/O

I/O0-I/O7 DATA COLUMN I/O

CIRCUIT

CE

CONTROL

OE CIRCUIT

WE

ICSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which may appear in this publication. © Copyright 2000, Integrated Circuit Solution Inc.

2 |

Integrated Circuit Solution Inc. |

|

AHSR027-0A 04/19/2002 |

IC61LV256

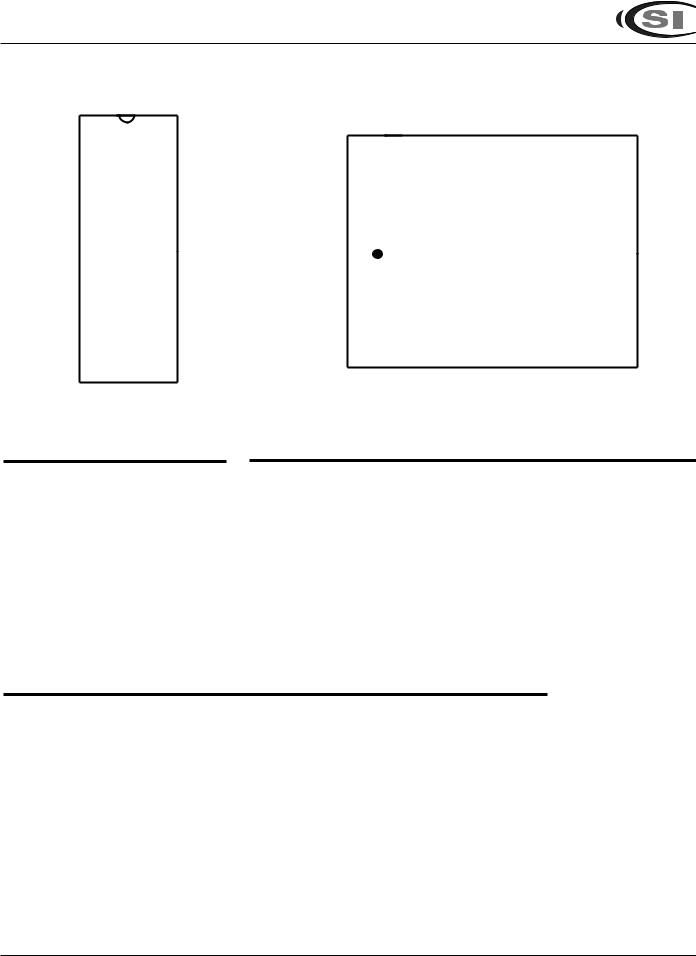

PIN CONFIGURATION |

|

|

|

|

|

|

|

|

PIN CONFIGURATION |

|

|

|

|

|

||||||||

28-Pin SOJ |

|

|

|

|

|

|

|

|

|

|

8x13.4mm TSOP-1 |

|

|

|

|

|

||||||

A14 |

|

1 |

28 |

|

VCC |

|

|

|

|

|

|

22 |

21 |

|

A10 |

|||||||

|

|

|

|

|

|

|

|

|

||||||||||||||

A12 |

|

2 |

27 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

WE |

|

|

|

|

OE |

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

A11 |

|

23 |

20 |

|

|

|

|

|||

A7 |

|

3 |

26 |

|

A13 |

|

|

|

|

CE |

|

|||||||||||

|

|

|||||||||||||||||||||

A6 |

|

4 |

25 |

|

A8 |

|

|

|

A9 |

|

24 |

19 |

|

I/O7 |

||||||||

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

A8 |

|

25 |

18 |

|

I/O6 |

||||||||||||

A5 |

|

5 |

24 |

|

A9 |

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

17 |

|

I/O5 |

|||||||||||

A4 |

|

6 |

23 |

|

A11 |

|

A13 |

26 |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

16 |

|

I/O4 |

|||||||||||

|

|

WE |

27 |

|

||||||||||||||||||

|

|

|

22 |

|

|

|

|

|

|

|

|

|

|

|||||||||

A3 |

|

7 |

|

|

OE |

|

|

|

|

|

|

|

|

15 |

|

I/O3 |

||||||

|

VCC |

28 |

|

|||||||||||||||||||

|

|

|

21 |

|

A10 |

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||

A2 |

|

8 |

|

|

A14 |

|

1 |

14 |

|

GND |

||||||||||||

|

|

|||||||||||||||||||||

|

|

|

20 |

|

|

|

|

|

|

|

|

A12 |

|

2 |

13 |

|

I/O2 |

|||||

A1 |

|

9 |

|

|

CE |

|

|

|

|

|||||||||||||

A0 |

|

10 |

19 |

|

I/O7 |

|

|

|

A7 |

|

3 |

12 |

|

I/O1 |

||||||||

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

A6 |

|

4 |

11 |

|

I/O0 |

||||||||||||

I/O0 |

|

11 |

18 |

|

I/O6 |

|

|

|

|

|

||||||||||||

|

|

|

|

|

A5 |

|

5 |

10 |

|

A0 |

||||||||||||

I/O1 |

|

12 |

17 |

|

I/O5 |

|

|

|

|

|

||||||||||||

|

|

|

|

|

A4 |

|

6 |

9 |

|

A1 |

||||||||||||

I/O2 |

|

13 |

16 |

|

I/O4 |

|

|

|

|

|

||||||||||||

|

|

|

|

|

A3 |

|

7 |

8 |

|

A2 |

||||||||||||

|

|

|

|

|

||||||||||||||||||

GND |

|

14 |

15 |

|

I/O3 |

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN DESCRIPTIONS

A0-A14 |

Address Inputs |

|

|

CE |

Chip Enable Input |

|

|

OE |

Output Enable Input |

|

|

WE |

Write Enable Input |

|

|

I/O0-I/O7 |

Input/Output |

|

|

Vcc |

Power |

|

|

GND |

Ground |

|

|

TRUTH TABLE

Mode |

WE |

CE |

OE |

I/O Operation |

Vcc Current |

Not Selected |

X |

H |

X |

High-Z |

ISB1, ISB2 |

(Power-down) |

|

|

|

|

|

Output Disabled |

H |

L |

H |

High-Z |

ICC |

|

|

|

|

|

|

Read |

H |

L |

L |

DOUT |

ICC |

|

|

|

|

|

|

Write |

L |

L |

X |

DIN |

ICC |

|

|

|

|

|

|

ABSOLUTE MAXIMUM RATINGS(1)

Symbol |

Parameter |

|

Value |

Unit |

VCC |

Power Supply Voltage Relative to GND |

|

–0.5 to +4.6 |

V |

|

|

|

|

|

VTERM |

Terminal Voltage with Respect to GND |

|

–0.5 to +4.6 |

V |

|

|

|

|

|

TBIAS |

Temperature Under Bias |

Com. |

–10 to +85 |

°C |

|

|

Ind. |

–45 to +90 |

|

|

|

|

|

|

TSTG |

Storage Temperature |

|

–65 to +150 |

°C |

|

|

|

|

|

PD |

Power Dissipation |

|

1 |

W |

|

|

|

|

|

IOUT |

DC Output Current |

|

±20 |

mA |

Notes:

1. Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

Integrated Circuit Solution Inc. |

3 |

AHSR027-0A 04/19/2002

Loading...

Loading...