IBM 750GX, 750GL User Manual

Title Page

IBM PowerPC 750GX and 750GL RISC Microprocessor

User’s Manual

Version 1.2

March 27, 2006

®

© Copyright International Business Machines Corporation 2004, 2006

All Rights Reserved

Printed in the United States of America March 2006.

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both:

IBM |

POWER |

PowerPC 750 |

IBM Logo |

PowerPC |

PowerPC Architecture |

|

|

PowerPC Logo |

IEEE is a registered trademark in the United States, owned by the Institute of Electrical and Electronics Engineers.

Other company, product, and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN “AS IS” BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Microelectronics Division

2070 Route 52, Bldg. 330

Hopewell Junction, NY 12533-6351

The IBM home page can be found at ibm.com

The IBM Microelectronics Division home page can be found at ibm.com/chips

gx_title.fm.(1.2) March 27, 2006

|

User’s Manual |

IBM PowerPC 750GX and 750GL RISC Microprocessor |

|

List of Figures .............................................................................................................. |

13 |

List of Tables ............................................................................................................... |

. 15 |

About This Manual ........................................................................................................ |

19 |

Who Should Read This Manual ................................................................................................... |

......... 19 |

Related Publications ............................................................................................................................. |

19 |

Conventions Used in This Manual ............................................................................................... |

......... 20 |

Using This Manual with the Programming Environments Manual ......................................................... |

22 |

1. PowerPC 750GX Overview ....................................................................................... |

23 |

1.1 750GX Microprocessor Overview ............................................................................................. |

...... 23 |

1.2 750GX Microprocessor Features ............................................................................................. |

....... 25 |

1.2.1 Instruction Flow ........................................................................................................ |

............. 29 |

1.2.1.1 Instruction Queue and Dispatch Unit .............................................................................. |

29 |

1.2.1.2 Branch Processing Unit (BPU) ....................................................................................... |

29 |

1.2.1.3 Completion Unit ....................................................................................................... |

....... 30 |

1.2.2 Independent Execution Units ............................................................................................. |

.... 31 |

1.2.2.1 Integer Units (IUs) ................................................................................................... |

....... 31 |

1.2.2.2 Floating-Point Unit (FPU) ............................................................................................. |

.. 31 |

1.2.2.3 Load/Store Unit (LSU) ................................................................................................. |

... 32 |

1.2.2.4 System Register Unit (SRU) ........................................................................................... |

32 |

1.2.3 Memory Management Units (MMUs) ..................................................................................... |

32 |

1.2.4 On-Chip Level 1 Instruction and Data Caches ...................................................................... |

33 |

1.2.5 On-Chip Level 2 Cache Implementation ................................................................................ |

35 |

1.2.6 System Interface/Bus Interface Unit (BIU) ............................................................................. |

35 |

1.2.7 Signals ................................................................................................................................... |

37 |

1.2.8 Signal Configuration .................................................................................................... |

.......... 38 |

1.2.9 Clocking ................................................................................................................................. |

40 |

1.3 750GX Microprocessor Implementation ....................................................................................... |

... 40 |

1.4 PowerPC Registers and Programming Model ................................................................................ |

42 |

1.5 Instruction Set ................................................................................................................................. |

45 |

1.5.1 PowerPC Instruction Set ................................................................................................. |

...... 45 |

1.5.2 750GX Microprocessor Instruction Set .................................................................................. |

47 |

1.6 On-Chip Cache Implementation .............................................................................................. |

........ 47 |

1.6.1 PowerPC Cache Model ..................................................................................................... |

.... 47 |

1.6.2 750GX Microprocessor Cache Implementation .................................................................... |

47 |

1.7 Exception Model .............................................................................................................................. |

48 |

1.7.1 PowerPC Exception Model ................................................................................................. |

... 48 |

1.7.2 750GX Microprocessor Exception Implementation ............................................................... |

49 |

1.8 Memory Management ......................................................................................................... |

............ 51 |

1.8.1 PowerPC Memory-Management Model ................................................................................ |

51 |

1.8.2 750GX Microprocessor Memory-Management Implementation ........................................... |

52 |

1.9 Instruction Timing ............................................................................................................................ |

52 |

1.10 Power Management ......................................................................................................... |

............. 54 |

1.11 Thermal Management ....................................................................................................... |

............ 55 |

1.12 Performance Monitor ..................................................................................................................... |

56 |

750gx_umTOC.fm.(1.2) |

|

March 27, 2006 |

Page 3 of 377 |

User’s Manual |

|

IBM PowerPC 750GX and 750GL RISC Microprocessor |

|

2. Programming Model .................................................................................................. |

57 |

2.1 PowerPC 750GX Processor Register Set ....................................................................................... |

57 |

2.1.1 Register Set ........................................................................................................................... |

57 |

2.1.2 PowerPC 750GX-Specific Registers ...................................................................................... |

64 |

2.1.2.1 Instruction Address Breakpoint Register (IABR) ............................................................ |

64 |

2.1.2.2 Hardware-Implementation-Dependent Register 0 (HID0) .............................................. |

65 |

2.1.2.3 Hardware-Implementation-Dependent Register 1 (HID1) .............................................. |

70 |

2.1.2.4 Hardware-Implementation-Dependent Register 2 (HID2) .............................................. |

71 |

2.1.2.5 Performance-Monitor Registers ...................................................................................... |

72 |

2.1.3 Instruction Cache Throttling Control Register (ICTC) ............................................................ |

77 |

2.1.4 Thermal-Management Registers (THRMn) ............................................................................ |

78 |

2.1.4.1 Thermal-Management Registers 1–2 (THRM1–THRM2) ............................................... |

78 |

2.1.4.2 Thermal-Management Register 3 (THRM3) ................................................................... |

79 |

2.1.4.3 Thermal-Management Register 4 (THRM4) ................................................................... |

80 |

2.1.5 L2 Cache Control Register (L2CR) ........................................................................................ |

81 |

2.2 Operand Conventions ..................................................................................................................... |

82 |

2.2.1 Data Organization in Memory and Data Transfers ................................................................ |

82 |

2.2.2 Alignment and Misaligned Accesses ..................................................................................... |

82 |

2.2.3 Floating-Point Operand and Execution Models—UISA ......................................................... |

83 |

2.2.3.1 Denormalized Number Support ...................................................................................... |

83 |

2.2.3.2 Non-IEEE Mode (Nondenormalized Mode) .................................................................... |

83 |

2.2.3.3 Time-Critical Floating-Point Operation ........................................................................... |

84 |

2.2.3.4 Floating-Point Storage Access Alignment ...................................................................... |

84 |

2.2.3.5 Optional Floating-Point Graphics Instructions ................................................................ |

84 |

2.3 Instruction Set Summary ................................................................................................................. |

86 |

2.3.1 Classes of Instructions ........................................................................................................... |

87 |

2.3.1.1 Definition of Boundedly Undefined ................................................................................. |

87 |

2.3.1.2 Defined Instruction Class ................................................................................................ |

87 |

2.3.1.3 Illegal Instruction Class ................................................................................................... |

88 |

2.3.1.4 Reserved Instruction Class ............................................................................................. |

89 |

2.3.2 Addressing Modes ................................................................................................................. |

89 |

2.3.2.1 Memory Addressing ........................................................................................................ |

89 |

2.3.2.2 Memory Operands .......................................................................................................... |

89 |

2.3.2.3 Effective Address Calculation ......................................................................................... |

90 |

2.3.2.4 Synchronization .............................................................................................................. |

90 |

2.3.3 Instruction Set Overview ........................................................................................................ |

91 |

2.3.4 PowerPC UISA Instructions ................................................................................................... |

92 |

2.3.4.1 Integer Instructions ......................................................................................................... |

92 |

2.3.4.2 Floating-Point Instructions .............................................................................................. |

95 |

2.3.4.3 Load-and-Store Instructions ........................................................................................... |

98 |

2.3.4.4 Branch and Flow-Control Instructions .......................................................................... |

106 |

2.3.4.5 System Linkage Instruction—UISA .............................................................................. |

108 |

2.3.4.6 Processor Control Instructions—UISA ......................................................................... |

108 |

2.3.4.7 Memory Synchronization Instructions—UISA ............................................................... |

113 |

2.3.5 PowerPC VEA Instructions .................................................................................................. |

113 |

2.3.5.1 Processor Control Instructions—VEA ........................................................................... |

113 |

2.3.5.2 Memory Synchronization Instructions—VEA ................................................................ |

114 |

2.3.5.3 Memory Control Instructions—VEA .............................................................................. |

115 |

2.3.5.4 Optional External Control Instructions .......................................................................... |

117 |

2.3.6 PowerPC OEA Instructions .................................................................................................. |

118 |

|

750gx_umTOC.fm.(1.2) |

Page 4 of 377 |

March 27, 2006 |

|

User’s Manual |

|

IBM PowerPC 750GX and 750GL RISC Microprocessor |

||

2.3.6.1 System Linkage Instructions—OEA ............................................................................. |

|

118 |

2.3.6.2 Processor Control Instructions—OEA .......................................................................... |

|

118 |

2.3.6.3 Memory Control Instructions—OEA ............................................................................. |

|

119 |

2.3.7 Recommended Simplified Mnemonics ................................................................................ |

|

120 |

3. Instruction-Cache and Data-Cache Operation .................................................... |

|

121 |

3.1 Data-Cache Organization ................................................................................................... |

........... |

123 |

3.2 Instruction-Cache Organization ............................................................................................ |

......... |

124 |

3.3 Memory and Cache Coherency ................................................................................................ |

.... |

125 |

3.3.1 Memory/Cache Access Attributes (WIMG Bits) ................................................................... |

|

125 |

3.3.2 MEI Protocol ............................................................................................................ |

............ |

126 |

3.3.2.1 MEI Hardware Considerations ..................................................................................... |

|

128 |

3.3.3 Coherency Precautions in Single-Processor Systems ........................................................ |

|

129 |

3.3.4 Coherency Precautions in Multiprocessor Systems ............................................................ |

|

129 |

3.3.5 PowerPC 750GX-Initiated Load/Store Operations .............................................................. |

|

130 |

3.3.5.1 Performed Loads and Stores ....................................................................................... |

|

130 |

3.3.5.2 Sequential Consistency of Memory Accesses ............................................................. |

|

130 |

3.3.5.3 Atomic Memory References ......................................................................................... |

|

130 |

3.4 Cache Control ............................................................................................................................... |

|

131 |

3.4.1 Cache-Control Parameters in HID0 ..................................................................................... |

|

131 |

3.4.1.1 Data-Cache Flash Invalidation ..................................................................................... |

|

132 |

3.4.1.2 Enabling and Disabling the Data Cache ....................................................................... |

|

132 |

3.4.1.3 Locking the Data Cache ............................................................................................... |

|

132 |

3.4.1.4 Instruction-Cache Flash Invalidation ............................................................................ |

|

133 |

3.4.1.5 Enabling and Disabling the Instruction Cache .............................................................. |

|

133 |

3.4.1.6 Locking the Instruction Cache ...................................................................................... |

|

133 |

3.4.2 Cache-Control Instructions .............................................................................................. |

.... |

133 |

3.4.2.1 Data Cache Block Touch (dcbt) and Data Cache Block Touch for Store (dcbtst) ...... |

134 |

|

3.4.2.2 Data Cache Block Zero (dcbz) ..................................................................................... |

|

134 |

3.4.2.3 Data Cache Block Store (dcbst) .................................................................................. |

|

135 |

3.4.2.4 Data Cache Block Flush (dcbf) .................................................................................... |

|

135 |

3.4.2.5 Data Cache Block Invalidate (dcbi) ............................................................................. |

|

135 |

3.4.2.6 Instruction Cache Block Invalidate (icbi) ...................................................................... |

|

136 |

3.5 Cache Operations ......................................................................................................................... |

|

136 |

3.5.1 Cache-Block-Replacement/Castout Operations .................................................................. |

|

136 |

3.5.2 Cache Flush Operations .................................................................................................. |

.... |

138 |

3.5.3 Data-Cache Block-Fill Operations ....................................................................................... |

|

139 |

3.5.4 Instruction-Cache Block-Fill Operations .............................................................................. |

|

139 |

3.5.5 Data-Cache Block-Push Operations .................................................................................... |

|

139 |

3.6 L1 Caches and 60x Bus Transactions ........................................................................................ |

.. |

139 |

3.6.1 Read Operations and the MEI Protocol ............................................................................... |

|

140 |

3.6.2 Bus Operations Caused by Cache-Control Instructions ...................................................... |

|

141 |

3.6.3 Snooping ............................................................................................................................. |

|

142 |

3.6.4 Snoop Response to 60x Bus Transactions ......................................................................... |

|

143 |

3.6.5 Transfer Attributes ..................................................................................................... |

.......... |

145 |

3.7 MEI State Transactions ................................................................................................................. |

|

147 |

4. Exceptions ............................................................................................................... |

|

151 |

4.1 PowerPC 750GX Microprocessor Exceptions ............................................................................... |

|

152 |

750gx_umTOC.fm.(1.2) |

|

|

March 27, 2006 |

Page 5 of 377 |

|

User’s Manual |

|

IBM PowerPC 750GX and 750GL RISC Microprocessor |

|

4.2 Exception Recognition and Priorities ............................................................................................. |

153 |

4.3 Exception Processing .................................................................................................................... |

156 |

4.3.1 Machine Status Save/Restore Register 0 (SRR0) ............................................................... |

156 |

4.3.2 Machine Status Save/Restore Register 1 (SRR1) ............................................................... |

157 |

4.3.3 Machine State Register (MSR) ............................................................................................ |

158 |

4.3.4 Enabling and Disabling Exceptions ...................................................................................... |

160 |

4.3.5 Steps for Exception Processing ........................................................................................... |

160 |

4.3.6 Setting MSR[RI] ................................................................................................................... |

161 |

4.3.7 Returning from an Exception Handler .................................................................................. |

161 |

4.4 Process Switching ......................................................................................................................... |

162 |

4.5 Exception Definitions ..................................................................................................................... |

162 |

4.5.1 System Reset Exception (0x00100) ..................................................................................... |

163 |

4.5.1.1 Soft Reset ..................................................................................................................... |

164 |

4.5.1.2 Hard Reset ................................................................................................................... |

164 |

4.5.2 Machine-Check Exception (0x00200) .................................................................................. |

167 |

4.5.2.1 Machine-Check Exception Enabled (MSR[ME] = 1) ..................................................... |

168 |

4.5.2.2 Checkstop State (MSR[ME] = 0) .................................................................................. |

169 |

4.5.3 DSI Exception (0x00300) ..................................................................................................... |

169 |

4.5.4 ISI Exception (0x00400) ....................................................................................................... |

169 |

4.5.5 External Interrupt Exception (0x00500) ............................................................................... |

169 |

4.5.6 Alignment Exception (0x00600) ........................................................................................... |

170 |

4.5.7 Program Exception (0x00700) ............................................................................................. |

170 |

4.5.8 Floating-Point Unavailable Exception (0x00800) ................................................................. |

171 |

4.5.9 Decrementer Exception (0x00900) ...................................................................................... |

171 |

4.5.10 System Call Exception (0x00C00) ..................................................................................... |

171 |

4.5.11 Trace Exception (0x00D00) ............................................................................................... |

171 |

4.5.12 Floating-Point Assist Exception (0x00E00) ........................................................................ |

171 |

4.5.13 Performance-Monitor Interrupt (0x00F00) ......................................................................... |

172 |

4.5.14 Instruction Address Breakpoint Exception (0x01300) ........................................................ |

173 |

4.5.15 System Management Interrupt (0x01400) ......................................................................... |

173 |

4.5.16 Thermal-Management Interrupt Exception (0x01700) ....................................................... |

174 |

4.5.17 Data Address Breakpoint Exception .................................................................................. |

175 |

4.5.17.1 Data Address Breakpoint Register (DABR) ................................................................ |

175 |

4.5.18 Soft Stops .......................................................................................................................... |

175 |

4.5.19 Exception Latencies ........................................................................................................... |

176 |

4.5.20 Summary of Front-End Exception Handling ....................................................................... |

176 |

4.5.21 Timer Facilities ................................................................................................................... |

177 |

4.5.22 External Access Instructions .............................................................................................. |

177 |

5. Memory Management .............................................................................................. |

179 |

5.1 MMU Overview .............................................................................................................................. |

179 |

5.1.1 Memory Addressing ............................................................................................................. |

181 |

5.1.2 MMU Organization ............................................................................................................... |

181 |

5.1.3 Address-Translation Mechanisms ........................................................................................ |

186 |

5.1.4 Memory-Protection Facilities ................................................................................................ |

187 |

5.1.5 Page History Information ..................................................................................................... |

188 |

5.1.6 General Flow of MMU Address Translation ......................................................................... |

189 |

5.1.6.1 Real-Addressing Mode and Block-Address-Translation Selection ............................... |

189 |

5.1.6.2 Page-Address-Translation Selection ............................................................................ |

190 |

5.1.7 MMU Exceptions Summary ................................................................................................. |

192 |

|

750gx_umTOC.fm.(1.2) |

Page 6 of 377 |

March 27, 2006 |

|

User’s Manual |

IBM PowerPC 750GX and 750GL RISC Microprocessor |

|

5.1.8 MMU Instructions and Register Summary ........................................................................... |

194 |

5.2 Real-Addressing Mode ...................................................................................................... |

............ 195 |

5.3 Block-Address Translation ................................................................................................. |

........... 196 |

5.4 Memory Segment Model ...................................................................................................... |

......... 196 |

5.4.1 Page History Recording .................................................................................................. |

..... 196 |

5.4.1.1 Referenced Bit ........................................................................................................ |

...... 197 |

5.4.1.2 Changed Bit ........................................................................................................... |

....... 198 |

5.4.1.3 Scenarios for Referenced and Changed Bit Recording ............................................... |

198 |

5.4.2 Page Memory Protection .................................................................................................. |

... 199 |

5.4.3 TLB Description ......................................................................................................... |

.......... 199 |

5.4.3.1 TLB Organization ...................................................................................................... |

... 199 |

5.4.3.2 TLB Invalidation ...................................................................................................... |

...... 201 |

5.4.4 Page-Address-Translation Summary .................................................................................. |

202 |

5.4.5 Page Table-Search Operation ............................................................................................. |

204 |

5.4.6 Page Table Updates ...................................................................................................... |

...... 207 |

5.4.7 Segment Register Updates ................................................................................................ |

. 207 |

6. Instruction Timing ................................................................................................... |

209 |

6.1 Terminology and Conventions ............................................................................................... |

....... 209 |

6.2 Instruction Timing Overview ............................................................................................... |

........... 211 |

6.3 Timing Considerations .................................................................................................................. |

215 |

6.3.1 General Instruction Flow ................................................................................................ |

...... 215 |

6.3.2 Instruction Fetch Timing ................................................................................................ |

...... 216 |

6.3.2.1 Cache Arbitration ..................................................................................................... |

..... 217 |

6.3.2.2 Cache Hit ............................................................................................................. |

......... 217 |

6.3.2.3 Cache Miss ............................................................................................................ |

....... 222 |

6.3.2.4 L2 Cache Access Timing Considerations ..................................................................... |

224 |

6.3.2.5 Instruction Dispatch and Completion Considerations ................................................... |

224 |

6.3.2.6 Rename Register Operation ......................................................................................... |

224 |

6.3.2.7 Instruction Serialization ............................................................................................. |

... 225 |

6.4 Execution-Unit Timings ................................................................................................................. |

225 |

6.4.1 Branch Processing Unit Execution Timing .......................................................................... |

225 |

6.4.1.1 Branch Folding ........................................................................................................ |

..... 226 |

6.4.1.2 Branch Instructions and Completion ............................................................................ |

227 |

6.4.1.3 Branch Prediction and Resolution ................................................................................ |

228 |

6.4.2 Integer Unit Execution Timing ........................................................................................... |

.. 232 |

6.4.3 Floating-Point Unit Execution Timing .................................................................................. |

232 |

6.4.4 Effect of Floating-Point Exceptions on Performance ........................................................... |

232 |

6.4.5 Load/Store Unit Execution Timing ....................................................................................... |

233 |

6.4.6 Effect of Operand Placement on Performance .................................................................... |

233 |

6.4.7 Integer Store Gathering ................................................................................................. |

...... 234 |

6.4.8 System Register Unit Execution Timing .............................................................................. |

234 |

6.5 Memory Performance Considerations ......................................................................................... |

.. 235 |

6.5.1 Caching and Memory Coherency ........................................................................................ |

235 |

6.5.2 Effect of TLB Miss ...................................................................................................... |

......... 236 |

6.6 Instruction Scheduling Guidelines ......................................................................................... |

........ 236 |

6.6.1 Branch, Dispatch, and Completion-Unit Resource Requirements ....................................... |

237 |

6.6.1.1 Branch-Resolution Resource Requirements ................................................................ |

237 |

6.6.1.2 Dispatch-Unit Resource Requirements ........................................................................ |

237 |

750gx_umTOC.fm.(1.2) |

|

March 27, 2006 |

Page 7 of 377 |

User’s Manual |

|

IBM PowerPC 750GX and 750GL RISC Microprocessor |

|

6.6.1.3 Completion-Unit Resource Requirements .................................................................... |

237 |

6.7 Instruction Latency Summary ........................................................................................................ |

238 |

7. Signal Descriptions ................................................................................................. |

249 |

7.1 Signal Configuration ...................................................................................................................... |

250 |

7.2 Signal Descriptions ........................................................................................................................ |

251 |

7.2.1 Address-Bus Arbitration Signals .......................................................................................... |

251 |

7.2.1.1 Bus Request (BR)—Output .......................................................................................... |

251 |

7.2.1.2 Bus Grant (BG)—Input ................................................................................................. |

252 |

7.2.1.3 Address Bus Busy (ABB) .............................................................................................. |

252 |

7.2.2 Address Transfer Start Signals ............................................................................................ |

253 |

7.2.2.1 Transfer Start (TS) ........................................................................................................ |

253 |

7.2.3 Address Transfer Signals ..................................................................................................... |

254 |

7.2.3.1 Address Bus (A[0–31]) ................................................................................................. |

254 |

7.2.3.2 Address-Bus Parity (AP[0–3]) ....................................................................................... |

255 |

7.2.4 Address Transfer Attribute Signals ...................................................................................... |

255 |

7.2.4.1 Transfer Type (TT[0–4]) ............................................................................................... |

256 |

7.2.4.2 Transfer Size (TSIZ[0–2])—Output ............................................................................... |

258 |

7.2.4.3 Transfer Burst (TBST) .................................................................................................. |

259 |

7.2.4.4 Cache Inhibit (CI)—Output ........................................................................................... |

260 |

7.2.4.5 Write-Through (WT)—Output ....................................................................................... |

260 |

7.2.4.6 Global (GBL) ................................................................................................................. |

261 |

7.2.5 Address Transfer Termination Signals ................................................................................. |

262 |

7.2.5.1 Address Acknowledge (AACK)—Input ......................................................................... |

262 |

7.2.5.2 Address Retry (ARTRY) ............................................................................................... |

263 |

7.2.6 Data-Bus Arbitration Signals ................................................................................................ |

264 |

7.2.6.1 Data-Bus Grant (DBG)—Input ...................................................................................... |

264 |

7.2.6.2 Data-Bus Write-Only (DBWO) ...................................................................................... |

265 |

7.2.6.3 Data Bus Busy (DBB) ................................................................................................... |

265 |

7.2.7 Data-Transfer Signals .......................................................................................................... |

266 |

7.2.7.1 Data Bus (DH[0–31], DL[0–31]) .................................................................................... |

266 |

7.2.7.2 Data-Bus Parity (DP[0–7]) ............................................................................................ |

267 |

7.2.7.3 Data Bus Disable (DBDIS)—Input ................................................................................ |

268 |

7.2.8 Data-Transfer Termination Signals ...................................................................................... |

268 |

7.2.8.1 Transfer Acknowledge (TA)—Input .............................................................................. |

268 |

7.2.8.2 Data Retry (DRTRY)—Input ......................................................................................... |

269 |

7.2.8.3 Transfer Error Acknowledge (TEA)—Input ................................................................... |

269 |

7.2.9 System Status Signals ......................................................................................................... |

270 |

7.2.9.1 Interrupt (INT)— Input .................................................................................................. |

270 |

7.2.9.2 System Management Interrupt (SMI)—Input ................................................................ |

270 |

7.2.9.3 Machine-Check Interrupt (MCP)—Input ....................................................................... |

271 |

7.2.9.4 Checkstop Input (CKSTP_IN)—Input ........................................................................... |

271 |

7.2.9.5 Checkstop Output (CKSTP_OUT)—Output ................................................................. |

271 |

7.2.10 Reset Signals ..................................................................................................................... |

272 |

7.2.10.1 Hard Reset (HRESET)—Input .................................................................................... |

272 |

7.2.10.2 Soft Reset (SRESET)—Input ..................................................................................... |

272 |

7.2.11 Processor Status Signals ................................................................................................... |

273 |

7.2.11.1 Quiescent Request (QREQ)—Output ......................................................................... |

273 |

7.2.11.2 Quiescent Acknowledge (QACK)—Input .................................................................... |

273 |

7.2.11.3 Reservation (RSRV)—Output ..................................................................................... |

273 |

|

750gx_umTOC.fm.(1.2) |

Page 8 of 377 |

March 27, 2006 |

|

User’s Manual |

IBM PowerPC 750GX and 750GL RISC Microprocessor |

|

7.2.11.4 Time Base Enable (TBEN)—Input ............................................................................. |

274 |

7.2.11.5 TLB Invalidate Synchronize (TLBISYNC)—Input ....................................................... |

274 |

7.2.12 Processor Mode Selection Signals .................................................................................... |

274 |

7.2.13 I/O Voltage Select Signals ............................................................................................. |

.... 275 |

7.2.14 Test Interface Signals ................................................................................................. |

....... 275 |

7.2.14.1 IEEE 1149.1a-1993 Interface Description .................................................................. |

275 |

7.2.14.2 LSSD_MODE ............................................................................................................. |

275 |

7.2.14.3 L1_TSTCLK ............................................................................................................ |

.... 276 |

7.2.14.4 L2_TSTCLK ............................................................................................................ |

.... 276 |

7.2.14.5 BVSEL ................................................................................................................ |

........ 276 |

7.2.15 Clock Signals .......................................................................................................... |

........... 276 |

7.2.15.1 System Clock (SYSCLK)—Input ................................................................................ |

277 |

7.2.15.2 Clock Out (CLK_OUT)—Output ................................................................................. |

277 |

7.2.15.3 PLL Configuration (PLL_CFG[0:4])—Input ................................................................. |

277 |

7.2.15.4 PLL Range (PLL_RNG[0:1])—Input ........................................................................... |

278 |

7.2.16 Power and Ground Signals ............................................................................................... |

. 278 |

8. Bus Interface Operation ......................................................................................... |

279 |

8.1 Bus Interface Overview ................................................................................................................. |

280 |

8.1.1 Operation of the Instruction and Data L1 Caches ............................................................... |

281 |

8.1.2 Operation of the Bus Interface .......................................................................................... |

... 282 |

8.1.3 Bus Signal Clocking ..................................................................................................... |

........ 282 |

8.1.4 Optional 32-Bit Data Bus Mode ........................................................................................... |

282 |

8.1.5 Direct-Store Accesses ................................................................................................... |

...... 283 |

8.2 Memory-Access Protocol .................................................................................................... |

.......... 284 |

8.2.1 Arbitration Signals ..................................................................................................... |

.......... 285 |

8.2.2 Miss-under-Miss ......................................................................................................... |

......... 286 |

8.2.2.1 Miss-under-Miss and System Performance ................................................................. |

287 |

8.2.2.2 Speculative Loads and Conditional Branches .............................................................. |

290 |

8.3 Address-Bus Tenure ..................................................................................................................... |

290 |

8.3.1 Address-Bus Arbitration ................................................................................................. |

...... 290 |

8.3.2 Address Transfer ........................................................................................................ |

......... 292 |

8.3.2.1 Address-Bus Parity .................................................................................................... |

... 294 |

8.3.2.2 Address Transfer Attribute Signals ............................................................................... |

294 |

8.3.2.3 Burst Ordering During Data Transfers .......................................................................... |

295 |

8.3.2.4 Effect of Alignment in Data Transfers ........................................................................... |

296 |

8.3.2.5 Alignment of External Control Instructions ................................................................... |

300 |

8.3.3 Address Transfer Termination ............................................................................................ |

. 300 |

8.4 Data-Bus Tenure ........................................................................................................................... |

301 |

8.4.1 Data-Bus Arbitration .................................................................................................... |

........ 301 |

8.4.1.1 Using the DBB Signal ................................................................................................... |

302 |

8.4.2 Data-Bus Write-Only ..................................................................................................... |

....... 303 |

8.4.3 Data Transfer ........................................................................................................... |

............ 303 |

8.4.4 Data-Transfer Termination ............................................................................................... |

... 303 |

8.4.4.1 Normal Single-Beat Termination .................................................................................. |

304 |

8.4.4.2 Data-Transfer Termination Due to a Bus Error ............................................................ |

307 |

8.4.5 Memory Coherency—MEI Protocol ..................................................................................... |

308 |

8.5 Timing Examples ........................................................................................................................... |

309 |

8.6 Optional Bus Configuration ................................................................................................ |

........... 316 |

8.6.1 32-Bit Data Bus Mode .................................................................................................... |

..... 316 |

750gx_umTOC.fm.(1.2) |

|

March 27, 2006 |

Page 9 of 377 |

User’s Manual |

|

|

IBM PowerPC 750GX and 750GL RISC Microprocessor |

|

|

|

8.6.2 No-DRTRY Mode ................................................................................................................. |

318 |

8.7 |

Processor State Signals ................................................................................................................ |

319 |

|

8.7.1 Support for the lwarx and stwcx. Instruction Pair ............................................................... |

319 |

|

8.7.2 TLBISYNC Input .................................................................................................................. |

319 |

8.8 |

IEEE 1149.1a-1993 Compliant Interface ....................................................................................... |

319 |

|

8.8.1 JTAG/COP Interface ............................................................................................................ |

319 |

8.9 |

Using Data-Bus Write-Only ........................................................................................................... |

320 |

9. L2 Cache ................................................................................................................... |

323 |

|

9.1 |

L2 Cache Overview ....................................................................................................................... |

323 |

9.2 |

L2 Cache Operation ...................................................................................................................... |

323 |

9.3 |

L2 Cache Control Register (L2CR) ............................................................................................... |

329 |

9.4 |

L2 Cache Initialization ................................................................................................................... |

329 |

9.5 |

L2 Cache Global Invalidation ........................................................................................................ |

329 |

9.6 |

L2 Cache Used as On-Chip Memory ............................................................................................ |

330 |

|

9.6.1 Locking the L2 Cache .......................................................................................................... |

330 |

|

9.6.1.1 Loading the Locked L2 Cache ...................................................................................... |

331 |

|

9.6.1.2 Locked Cache Operation .............................................................................................. |

331 |

9.7 |

Data-Only and Instruction-Only Modes ......................................................................................... |

332 |

9.8 |

L2 Cache Test Features and Methods .......................................................................................... |

332 |

|

9.8.1 L2CR Support for L2 Cache Testing .................................................................................... |

332 |

|

9.8.2 L2 Cache Testing ................................................................................................................. |

333 |

9.9 |

L2 Cache Timing ........................................................................................................................... |

333 |

10. Power and Thermal Management ........................................................................ |

335 |

|

10.1 Dynamic Power Management ..................................................................................................... |

335 |

|

10.2 Programmable Power Modes ...................................................................................................... |

335 |

|

|

10.2.1 Power Management Modes ............................................................................................... |

337 |

|

10.2.1.1 Full On Mode .............................................................................................................. |

337 |

|

10.2.1.2 Doze Mode ................................................................................................................. |

337 |

|

10.2.1.3 Nap Mode ................................................................................................................... |

337 |

|

10.2.1.4 Sleep Mode ................................................................................................................ |

339 |

|

10.2.1.5 Dynamic Power Reduction ......................................................................................... |

339 |

|

10.2.2 Power Management Software Considerations ................................................................... |

340 |

10.3 750GX Dual PLL Feature ............................................................................................................ |

340 |

|

|

10.3.1 Overview ............................................................................................................................ |

340 |

|

10.3.2 Configuration Restriction on Frequency Transitions .......................................................... |

341 |

|

10.3.3 Dual PLL Implementation ................................................................................................... |

342 |

10.4 Thermal Assist Unit ..................................................................................................................... |

343 |

|

|

10.4.1 Thermal Assist Unit Overview ............................................................................................ |

343 |

|

10.4.2 Thermal Assist Unit Operation ........................................................................................... |

344 |

|

10.4.2.1 TAU Single-Threshold Mode ...................................................................................... |

345 |

|

10.4.2.2 TAU Dual-Threshold Mode ......................................................................................... |

346 |

|

10.4.2.3 750GX Junction Temperature Determination ............................................................. |

346 |

|

10.4.2.4 Power Saving Modes and TAU Operation .................................................................. |

347 |

10.5 Instruction-Cache Throttling ........................................................................................................ |

347 |

|

11. Performance Monitor and System Related Features ......................................... |

349 |

|

|

|

750gx_umTOC.fm.(1.2) |

Page 10 of 377 |

March 27, 2006 |

|

|

|

User’s Manual |

|

IBM PowerPC 750GX and 750GL RISC Microprocessor |

|

11.1 |

Performance-Monitor Interrupt ............................................................................................ |

........ 349 |

11.2 |

Special-Purpose Registers Used by Performance Monitor ......................................................... |

350 |

11.2.1 Performance-Monitor Registers ......................................................................................... |

351 |

|

|

11.2.1.1 Monitor Mode Control Register 0 (MMCR0) ............................................................... |

351 |

|

11.2.1.2 User Monitor Mode Control Register 0 (UMMCR0) .................................................... |

351 |

|

11.2.1.3 Monitor Mode Control Register 1 (MMCR1) ............................................................... |

351 |

|

11.2.1.4 User Monitor Mode Control Register 1 (UMMCR1) .................................................... |

351 |

|

11.2.1.5 Performance-Monitor Counter Registers (PMCn) ...................................................... |

351 |

|

11.2.1.6 User Performance-Monitor Counter Registers (UPMC1–UPMC4) ............................ |

354 |

|

11.2.1.7 Sampled Instruction Address Register (SIA) .............................................................. |

355 |

|

11.2.1.8 User Sampled Instruction Address Register (USIA) ................................................... |

355 |

11.3 |

Event Counting ............................................................................................................................ |

355 |

11.4 |

Event Selection ........................................................................................................................... |

356 |

11.5 |

Notes ........................................................................................................................................... |

356 |

11.6 |

Debug Support ............................................................................................................................ |

357 |

11.6.1 Overview ............................................................................................................................ |

357 |

|

11.6.2 Data-Address Breakpoint ................................................................................................ |

.. 357 |

|

11.7 |

JTAG/COP Functions ....................................................................................................... |

........... 357 |

11.7.1 Introduction ........................................................................................................................ |

357 |

|

11.7.2 Processor Resources Available through JTAG/COP Serial Interface ............................... |

357 |

|

11.8 |

Resets ......................................................................................................................................... |

359 |

11.8.1 Hard Reset ............................................................................................................. |

........... 359 |

|

11.8.2 Soft Reset .......................................................................................................................... |

359 |

|

11.8.3 Reset Sequence ......................................................................................................... |

....... 360 |

|

11.9 |

Checkstops ................................................................................................................................. |

361 |

11.9.1 Checkstop Sources ...................................................................................................... |

..... 361 |

|

11.9.2 Checkstop Control Bits ................................................................................................. |

..... 361 |

|

11.9.3 Open-Collector-Driver States during Checkstop ............................................................... |

362 |

|

11.9.4 Vacancy Slot Application ............................................................................................... |

.... 362 |

|

11.10 750GX Parity ............................................................................................................................. |

363 |

|

11.10.1 Parity Control and Status ............................................................................................. |

.... 364 |

|

11.10.2 Enabling Parity Error Detection ....................................................................................... |

364 |

|

11.10.3 Parity Errors ......................................................................................................... |

............ 364 |

|

Acronyms and Abbreviations ................................................................................... |

365 |

|

Index |

........................................................................................................................ |

.... 369 |

Revision Log .............................................................................................................. |

377 |

|

750gx_umTOC.fm.(1.2) |

|

March 27, 2006 |

Page 11 of 377 |

User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

|

750gx_umTOC.fm.(1.2) |

Page 12 of 377 |

March 27, 2006 |

|

|

User’s Manual |

|

IBM PowerPC 750GX and 750GL RISC Microprocessor |

|

List of Figures |

|

|

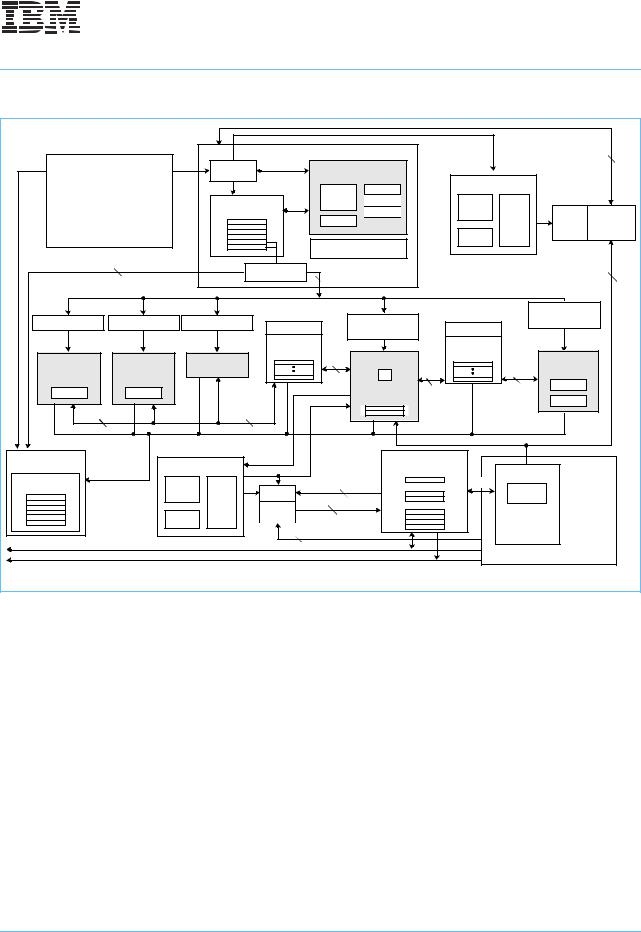

Figure 1-1. |

750GX Microprocessor Block Diagram .................................................................................. |

25 |

Figure 1-2. |

L1 Cache Organization .......................................................................................................... |

34 |

Figure 1-3. |

System Interface .................................................................................................................... |

37 |

Figure 1-4. |

750GX Microprocessor Signal Groups ................................................................................... |

39 |

Figure 1-5. |

Pipeline Diagram .................................................................................................................... |

53 |

Figure 2-1. |

PowerPC 750GX Microprocessor Programming Model—Registers ...................................... |

58 |

Figure 3-1. |

Cache Integration ................................................................................................................. |

122 |

Figure 3-2. |

Data-Cache Organization ..................................................................................................... |

123 |

Figure 3-3. |

Instruction-Cache Organization ............................................................................................ |

125 |

Figure 3-4. |

MEI Cache-Coherency Protocol—State Diagram (WIM = 001) ........................................... |

128 |

Figure 3-5. |

PLRU Replacement Algorithm ............................................................................................. |

137 |

Figure 3-6. |

750GX Cache Addresses ..................................................................................................... |

140 |

Figure 4-1. |

SRESET Asserted During HRESET .................................................................................... |

164 |

Figure 5-1. |

MMU Conceptual Block Diagram ......................................................................................... |

183 |

Figure 5-2. |

PowerPC 750GX Microprocessor IMMU Block Diagram ..................................................... |

184 |

Figure 5-3. |

750GX Microprocessor DMMU Block Diagram .................................................................... |

185 |

Figure 5-4. |

Address-Translation Types .................................................................................................. |

187 |

Figure 5-5. |

General Flow of Address Translation (Real-Addressing Mode and Block) .......................... |

189 |

Figure 5-6. |

General Flow of Page and Direct-Store Interface Address Translation ............................... |

191 |

Figure 5-7. |

Segment Register and DTLB Organization .......................................................................... |

200 |

Figure 5-8. |

Page-Address-Translation Flow—TLB Hit ........................................................................... |

203 |

Figure 5-9. |

Primary Page Table Search ................................................................................................. |

205 |

Figure 5-10. |

Secondary Page-Table-Search Flow ................................................................................... |

206 |

Figure 6-1. |

Pipelined Execution Unit ...................................................................................................... |

212 |

Figure 6-2. |

Superscalar/Pipeline Diagram .............................................................................................. |

212 |

Figure 6-3. |

PowerPC 750GX Microprocessor Pipeline Stages .............................................................. |

214 |

Figure 6-4. |

Instruction Flow Diagram ..................................................................................................... |

218 |

Figure 6-5. |

Instruction Timing—Cache Hit ............................................................................................. |

220 |

Figure 6-6. |

Instruction Timing—Cache Miss .......................................................................................... |

223 |

Figure 6-7. |

Branch Taken ....................................................................................................................... |

227 |

Figure 6-8. |

Removal of Fall-Through Branch Instruction ........................................................................ |

227 |

Figure 6-9. |

Branch Completion ............................................................................................................... |

228 |

Figure 6-10. |

Branch Instruction Timing .................................................................................................... |

231 |

Figure 7-1. |

750GX Signal Groups .......................................................................................................... |

250 |

Figure 8-1. |

Bus Interface Address Buffers ............................................................................................. |

280 |

Figure 8-2. |

Timing Diagram Legend ....................................................................................................... |

283 |

Figure 8-3. |

Overlapping Tenures on the 750GX Bus for a Single-Beat Transfer ................................... |

284 |

Figure 8-4. |

Cache Diagram for Miss-under-Miss Feature ...................................................................... |

286 |

750gx_umLOF.fm.(1.2) |

List of Figures |

|

March 27, 2006 |

|

Page 13 of 377 |

User’s Manual |

|

|

IBM PowerPC 750GX and 750GL RISC Microprocessor |

|

|

Figure 8-5. |

First Level Address Pipelining .............................................................................................. |

287 |

Figure 8-6. |

Address-Bus Arbitration ........................................................................................................ |

290 |

Figure 8-7. |

Address-Bus Arbitration Showing Bus Parking .................................................................... |

291 |

Figure 8-8. |

Address-Bus Transfer ........................................................................................................... |

293 |

Figure 8-9. |

Snooped Address Cycle with ARTRY .................................................................................. |

301 |

Figure 8-10. |

Data-Bus Arbitration ............................................................................................................. |

302 |

Figure 8-11. |

Normal Single-Beat Read Termination ................................................................................. |

304 |

Figure 8-12. |

Normal Single-Beat Write Termination ................................................................................. |

305 |

Figure 8-13. |

Normal Burst Transaction ..................................................................................................... |

305 |

Figure 8-14. |

Termination with DRTRY ...................................................................................................... |

306 |

Figure 8-15. |

Read Burst with TA Wait States and DRTRY ....................................................................... |

307 |

Figure 8-16. |

MEI Cache-Coherency Protocol—State Diagram (WIM = 001) ........................................... |

309 |

Figure 8-17. |

Fastest Single-Beat Reads ................................................................................................... |

310 |

Figure 8-18. |

Fastest Single-Beat Writes ................................................................................................... |

311 |

Figure 8-19. |

Single-Beat Reads Showing Data-Delay Controls ............................................................... |

312 |

Figure 8-20. |

Single-Beat Writes Showing Data-Delay Controls ................................................................ |

313 |

Figure 8-21. |

Burst Transfers with Data-Delay Controls ............................................................................ |

314 |

Figure 8-22. |

Use of Transfer Error Acknowledge (TEA) ........................................................................... |

315 |

Figure 8-23. |

32-Bit Data-Bus Transfer (8-Beat Burst) .............................................................................. |

317 |

Figure 8-24. |

32-Bit Data-Bus Transfer (2-Beat Burst with DRTRY) .......................................................... |

317 |

Figure 8-25. |

IEEE 1149.1a-1993 Compliant Boundary-Scan Interface .................................................... |

320 |

Figure 8-26. |

Data-Bus Write-Only Transaction ......................................................................................... |

320 |

Figure 9-1. |

L2 Cache .............................................................................................................................. |

327 |

Figure 10-1. |

750GX Power States ............................................................................................................ |

336 |

Figure 10-2. |

Dual PLL Block Diagram ...................................................................................................... |

342 |

Figure 10-3. |

Dual PLL Switching Example, 3X to 4X ................................................................................ |

343 |

Figure 10-4. |

Thermal Assist Unit Block Diagram ...................................................................................... |

344 |

Figure 10-5. |

Instruction Cache Throttling Control SPR Diagram .............................................................. |

347 |

Figure 11-1. |

750GX IEEE 1149.1a-1993/COP Organization .................................................................... |

358 |

Figure 11-2. |

Reset Sequence ................................................................................................................... |

360 |

List of Figures |

750gx_umLOF.fm.(1.2) |

Page 14 of 377 |

March 27, 2006 |

|

|

User’s Manual |

|

IBM PowerPC 750GX and 750GL RISC Microprocessor |

|

List of Tables |

|

|

Table 1-1. |

Architecture-Defined Registers (Excluding SPRs) ................................................................. |

42 |

Table 1-2. |

Architecture-Defined SPRs Implemented .............................................................................. |

43 |

Table 1-3. |

Implementation-Specific Registers ......................................................................................... |

44 |

Table 1-4. |

750GX Microprocessor Exception Classifications .................................................................. |

49 |

Table 1-5. |

Exceptions and Conditions ..................................................................................................... |

50 |

Table 2-1. |

Additional MSR Bits ............................................................................................................... |

60 |

Table 2-2. |

Additional SRR1 Bits .............................................................................................................. |

62 |

Table 2-3. |

Valid THRM1/THRM2 Bit Settings ......................................................................................... |

79 |

Table 2-4. |

Memory Operands ................................................................................................................. |

82 |

Table 2-5. |

Floating-Point Operand Data-Type Behavior ......................................................................... |

84 |

Table 2-6. |

Floating-Point Result Data-Type Behavior ............................................................................. |

85 |

Table 2-7. |

Integer Arithmetic Instructions ................................................................................................ |

92 |

Table 2-8. |