Explay Atom Service Manual

C142

8.2pF

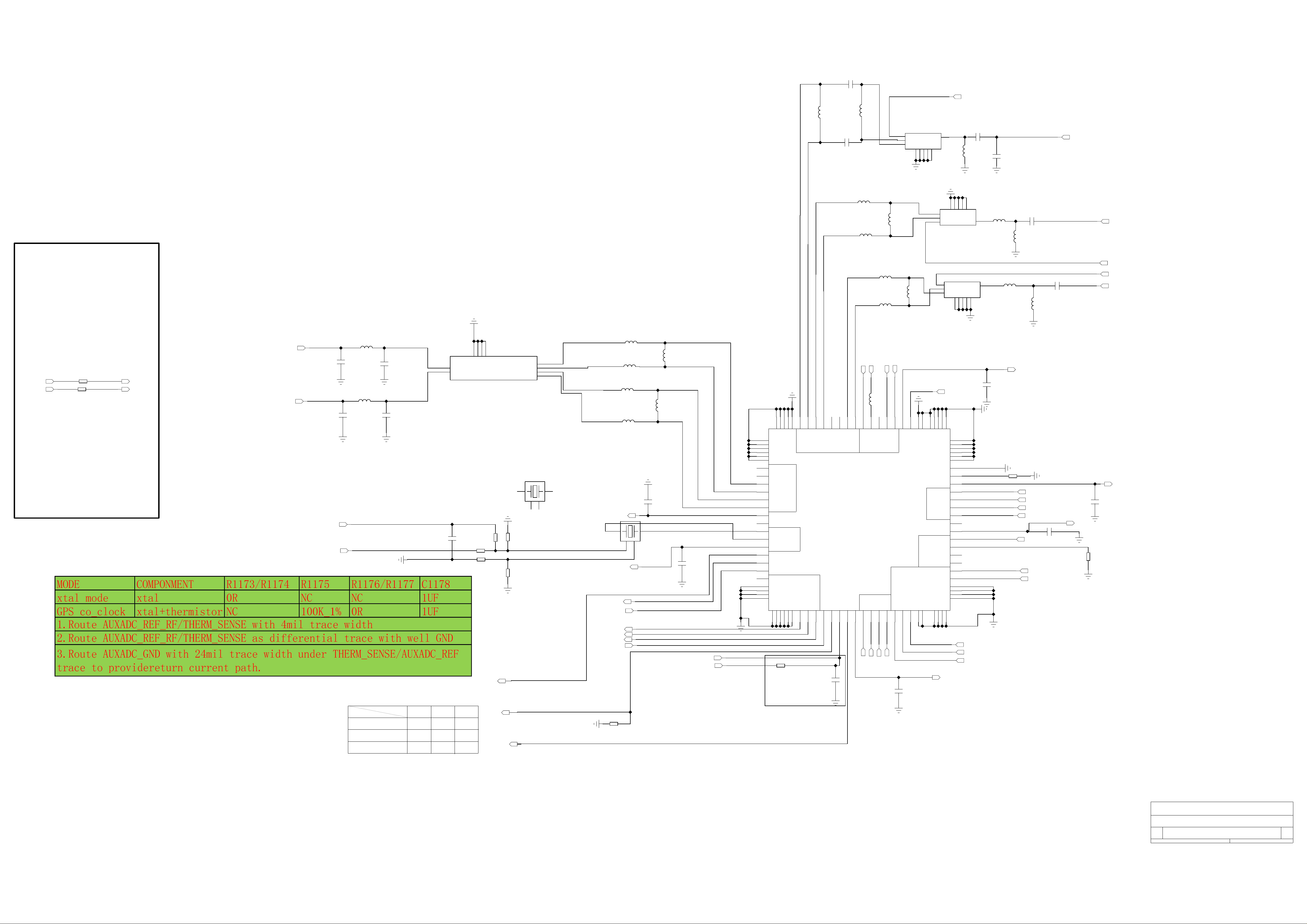

W_PA_OUT_B1

BPI0~4 and 10~11 are 2G+3G mode both

BPI5~9 and 12~14 are 3G mode only

(suggest BPI5~9 = 1.8V)

L161

4.7nH

C141

L140

4.7nH

8.2pF

LNA matching

and common mode trap

IND0402#1NH

1nH

L148

IND0402#1NH

L147

1nH

IND0402#1NH

L149

IND0402#1NH

L150

WCDMA_DP(S)_B1

3

TX

1

RX

8

RX

L146

33nH

IND0402#33NH

1nH

1nH

IND0402#33NH

MURATA

U104

GND

GND

GND

GND

9

7

5

2

4

L151

33nH

ANT

GND

8

1

3

2NH

10pF

L139

3NH

7

5

2

GND

GND

U105

U106

GND

GND

7

5

2

L138

0402

2.2nH

9

WCDMA_DP(S)_B5

GND

6

ANT

6

ANT

GND

GND

9

WCDMA_DP(S)_B8

C137

NC 0402

L145

1.2nH

0402

NC

L144

L152

1.5NH

1.2nH

0402

6.8nH

C143

L153

0402

56pF

6.8nH

C154

56pF

47PF

0402

WCDMA_TRX_B1

WCDMA_TRX_B5

W_PA_OUT_B5

W_PA_OUT_B8

WCDMA_TRX_B8

6

4

RX

GND

GND

RX

TX

3

TX

1

RX

8

RX

GND

4

3.9NH

VTCXO_PMU

VRF18_PMU

R117

R116

0R

0R

VTCXO28-1

VRF18-1

OTHER_RX

IND0402#2.2NH

L129

2G_LB

C128

0402

NC

2G_HB

C125

0402

NC

AUXADC_REF

THERM_ADC

GND_AUXADC

connect pin2 GND to MT6223 pin B2 first then connect to GND near B2.

2.2nH

0402

IND0402#3.3NH

L126

3.3nH

0402

C130

NC

C127

NC

Footprint compatible with 3225 footprint

0402

GND

1

UNBALANCED_PORT(L)

4

UNBALANCED_PORT(H)

RX_BALUN_SAW_MT6255

U103

C1178

1uF6.3V

GND3GND

R1176

R1177

2

5

10

GND

GND

0R

0R

VTCXO28-1

BALANCDE_PORT(L)

BALANCDE_PORT(L)

BALANCED_PORT(H)

BALANCED_PORT(H)

NC

100K_1%

R1174

R1175

NC

R1173

9

8

7

6

U108

1 3

GND

GND

4

2

26M_MT6166_2.5X2.0

VRF18-1

VTCXO28-1

SRCLKENA

SRCLKENA

CLK4_AUDIO

SYSCLK_WCN

CLK1_BB

DCXO_32K

C136

12nH

0402

C135

12nH

0402

C133

6.2nH

0402

C132

6.2nH

0402

0402

U102

1 3

GND

GND

4

2

L159

39nH

IND0402#39NH

L158

7.5nH

IND0402#7.5NH

GND

C124

0.47uF

26M_MT6253_3.2X2.5

0402

C115

0.47uF

GND

VDD1V8_LC

VDD1V8_PMU

VRF18-1

VTCXO28-1

SRCLKENA

SRCLKENA

MT6166

GND

U101

D3

E3

C2

J2

C3

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

B40_RXP

B40_RXN

LB_RXP

LB_RXN

HB_RXP

HB_RXN

VRXHF

RFVCO_MON

XTAL1

XTAL2

VTCXO28

32K_EN

EN_BB

CLK_SEL

XO3

GND

GND

GND

GND

GNDC5GNDD5GNDE5GND

J4

0R

TDD RX

26M output

GND

GND

F5

D7

CLK4_AUDIO

G3

H3

C4

D4

A1

B1

C1

D1

E1

G2

H2

K1

G1

K2

E4

G4

H4

F3

J3

F1

F2

J1

L1

L2

F4

R108

Reserved LC filter

A2

A3

B3

3GB1_RXP

3GB5_RXP

3GB1_RXN

XO

XO4

XO2L4XO1

K4

K3

SYSCLK_WCN

CLK1_BB

DCXO_32K

B4

A5

B5

3GB2_RXP

3GB5_RXN

MT6166

OUT32K

XMODEK7VXODIG

L5

K6

K5

C107

1uF10V

GGE_PA_HB_IN

C156

IND0402#2NH

B8

A6

B6

2GHB_TX

3GB8_RXP

3GB2_RXN

3GB8_RXN

MT6166

RX(I/Q)

VRXLF

AVDD_VIO18

RX_IPK8RX_IN

L7

L8

VRF18-1

RX_I_P

W_PA_LB_IN

W_PA_B1_IN

2nH

A8

A10

3GL5_TX

3GH1_TXA93GH2_TX

TXOFDD RX

RX_QPK9RX_QN

K10

RX_I_N

RX_Q_P

RX_Q_N

GGE_PA_LB_IN

B11

A11

VTXHF

2GLB_TX

TX(I/Q)

Test pin

BSI

BSI_ENH6BSI_CLK

G6

C106

B10

C10

D11

DET

GND

GNDC7GND

BSI_DATA0

GNDJ5GND

F8

E7

J7

C8

GNDC9GND

GNDJ8GND

GND

GND

GND

GND

GND

GND

DETGND

TMEAS

V28

3GTX_IP

3GTX_IN

3GTX_QP

3GTX_QN

TXVCO_MON

VTXLF

TXBPI

RCAL

TST2

TST1

BSI_DATA2

BSI_DATA1

GND

GND

GND

GND

GNDD6GNDE6GNDF6GND

C6

VRF18-1

PDET

D9

E9

F9

G9

H9

J9

D10

C11

E10

G10

G11

F10

F11

L11

J11

H10

J10

K11

L10

G8

H8

B7

J6

D8

E8

TMEAS

VRF18-1

BSI-A_DAT0

BSI-A_CK

BSI-A_EN

C157

0.47uF

0R

VRF18-1

R101

TXBPI

TX_I_P

TX_I_N

TX_Q_P

TX_Q_N

BSI-A_DAT2

BSI-A_DAT1

C104

VTCXO28-1

C103

0.47uF

VRF18-1

0.47uF

2K

R105

MODE

Logic

DCXO + 32K XO

DCXO + 32K-Less

DCXO_

32K_EN

0(GND)

1(VTXCO28)

XMODE

VXODIG

1(VIO18)1(VIO18)

1(VTXCO28)1(VTXCO28)

VTCXO28-1

VTCXO28-1

R160

NC

0.47uF

Title

RF-2G

Size Document Number Rev

A1

Date: Sheet of 91

Wednesday, January 02, 2013

MT6572 REF PHONE

V1.0

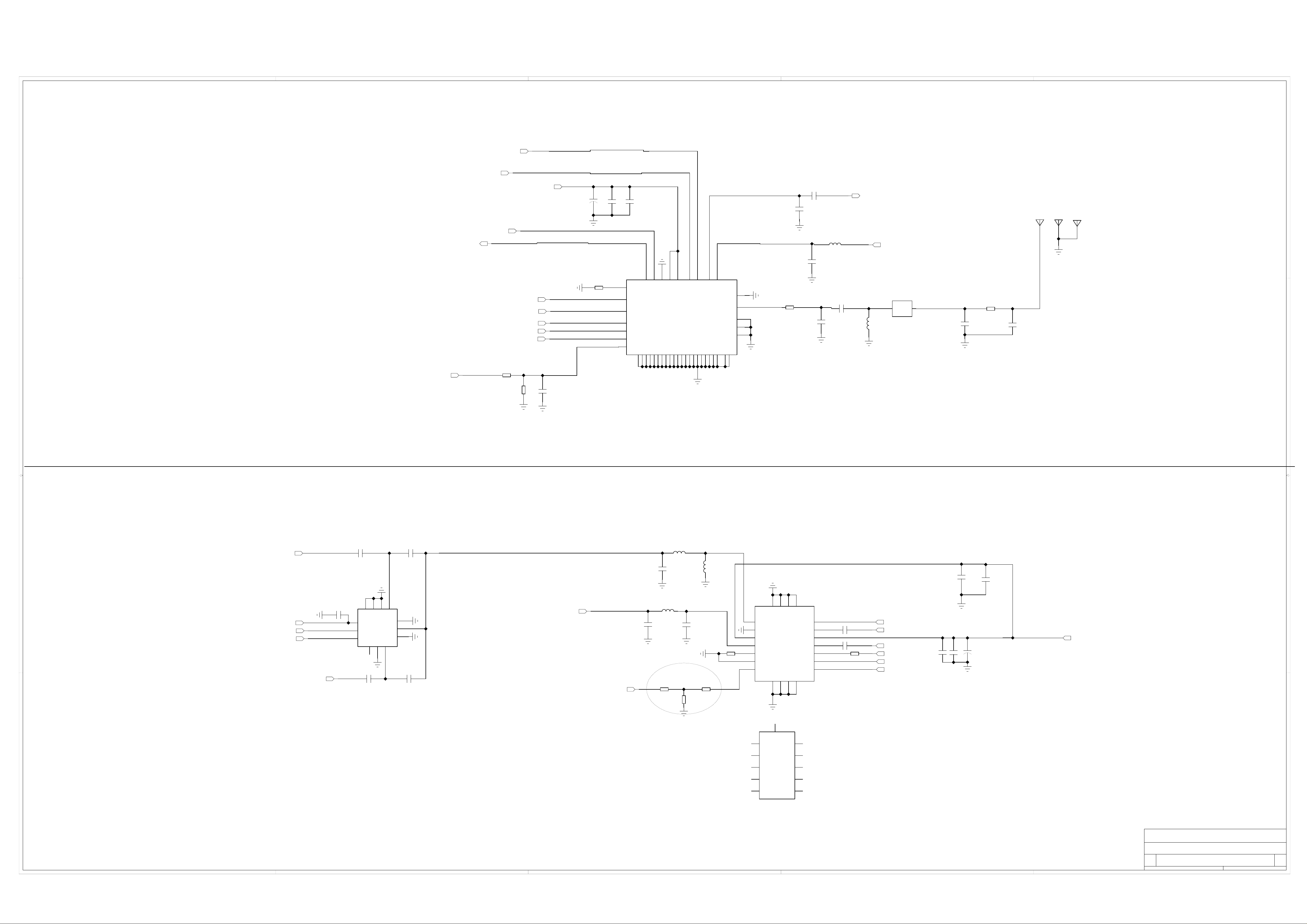

ASM_VCTRL_A

ASM_VCTRL_B

WG_GGE_PA_ENABLE

ASM_VCTRL_C

WCDMA_TRX_B8

WCDMA_TRX_B5

WCDMA_TRX_B1

2G_LB

2G_HB

VBAT_RF

+

R222

C219

0402

10uF

51R

C218

1uf_25V

24

23

22

21

20

19

18

C217

33pF

14

15

16

17

VCC

TRX6

TRX5

TRX4

TRX3

TRX2

TRX1

VRAMP

GND31GND32GND33GND34GND35GND36GND37GND38GND39GND40GND41GND42GND43GND44GND

30

GND

TXEN

MODE

U201

GSM_PA_SKY77589_QB

13

VBATT

12

BS1

11

BS2

GND2GND

1

9

10

TX_LB_IN

GND6GND7GND8GND

5

GND

TX_HB_IN

ANT

GND

GND

GND

GND4GND

3

C213

18pF

C212

0402

NC

C210

4.7nH

0.5pF

0402

25

26

27

28

29

R208

0R

C209

0402

C207

NC

CAP0402#22PF

L206

0402

GGE_PA_LB_IN

22pF

IND0402#18NH

L205

GGE_PA_HB_IN

RF_CONN_MM8430-2600

U202

IN

OUT

1

18nH

ANT201

4

0402

R201

C203

NC

0R

0402

C202

NC

ANT202

ANT203

WG_GGE_PA_VRAMP

R225

10K

R224

24K

0402

C223

220pF

W_PA_OUT_B8

VDD2V8_PMU

W_PA_B5_EN

W_PA_B8_EN

RF_WCDMA_SP2T_2.0X2.0

W_PA_OUT_B5

C254

0402

1uF6.3V

6

5

4

C252

VDD

V2

V1

0402

C257

56pF

13

GND

0402

N/C

GND

U204

3

7

GND

56pF

GND

GND

RFC

GND

1J12

C244

NC

L241

1nH

0402

27R

0402

L245

1nH

33R

C240

NC

R237

R236

L243

22nH

27R

0402

R239

51R

WCDMA_PA_SKY77758_QB

18

GND17GND16GND15GND

14

REOUT_LB

13

GND

12

VCC

11

RFOUT_HB

10

CPL_IN

9

GND

8

CPL_OUT

GND21GND20GND19GND

22

U203

VEN_LB

RFIN_LB

VBATT

RFIN_HB

NC

VMODE

VEN_HB

C232

1000pf

C246

0603

1000pF

C233

+

10uF

0402

1

C230

2

3

C234

4

5

6

7

18pF

0402

R235

56pF

NC

W_PA_LB_EN

W_PA_LB_IN

W_PA_B1_IN

VM1

VM0

W_PA_B1_EN

0402

C231

0201

22pF

C247

2.2uF

VBAT_RF

NC

C250

0402

9J28

10

11

12

NC

C255

0402

W_PA_OUT_B1

PDET

0402

0402

C242

0.5pF

place near U203

R238

11

10

9

8

7

6

GND

VCC2

RF_OUT

CPL_IN

GND

CPL_OUT

VMODE1

VMODE0

WCDMA_PA_SKY77761_B1

VCC1

RF_IN

VEN

U205

1

2

3

4

5

Footprint compatible with single PA

A1 V1.0

Friday, April 29, 2011

11

2 9ofSheetDate:

RevDocument NumberSize

RX_I_P

RX_I_N

RX_Q_P

RX_Q_N

TX_I_P

TX_I_N

TX_Q_P

TX_Q_N

VM0

VM1

TXBPI

WG_GGE_PA_VRAMP

D2

DL_I_P

C2

DL_I_N

B1

DL_Q_P

C1

DL_Q_N

A2

UL_I_P

B2

UL_I_N

B4

UL_Q_P

B3

UL_Q_N

A8

VM0

A7

VM1

D5

TXBPI

F2

APC

F3

VBIAS

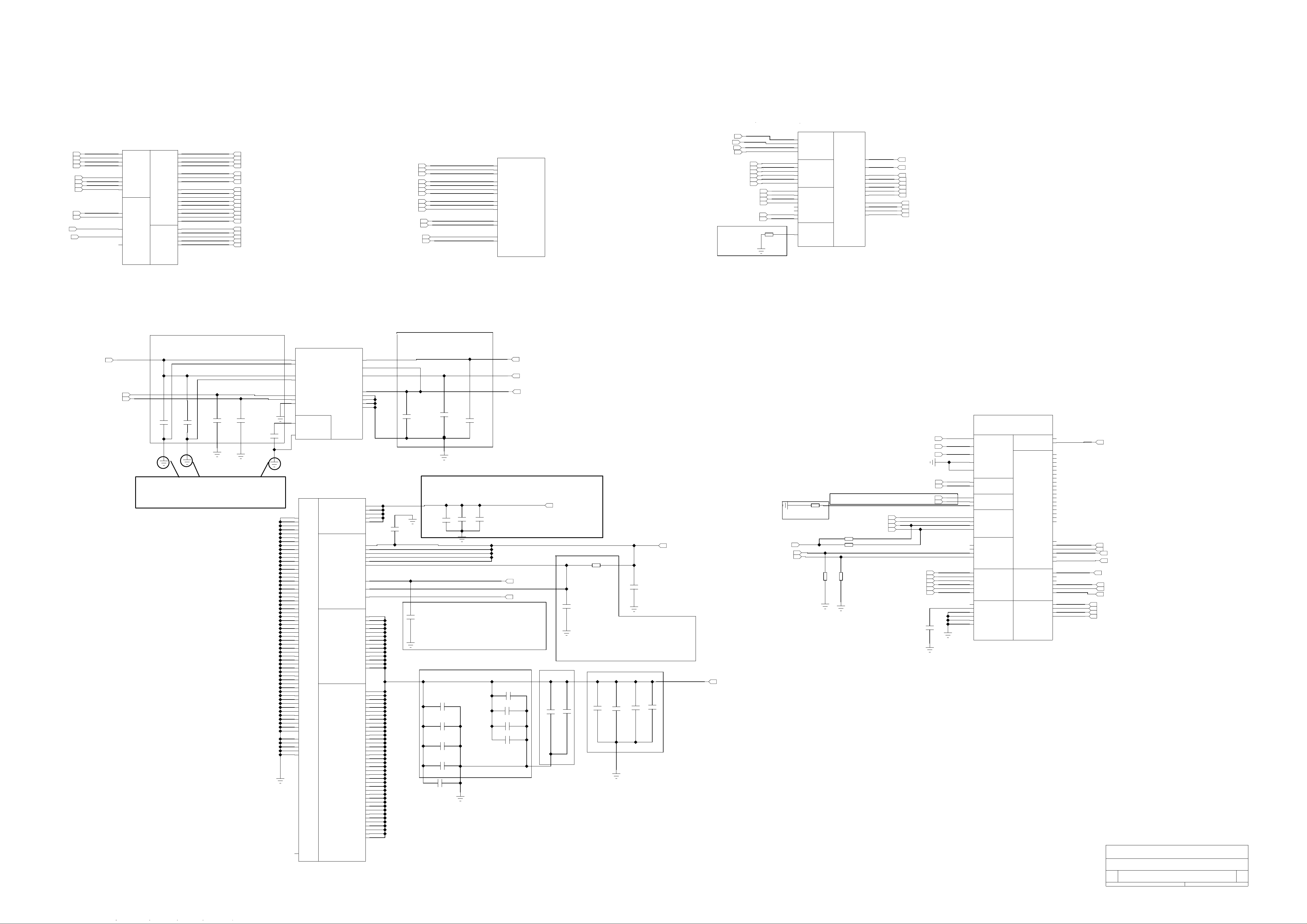

MT6572_LPDDR2

U301-A

BPI_BUS0

BPI_BUS1

BPI_BUS2

BPI_BUS3

BPI_BUS4

BPI_BUS5

BPI_BUS6

BPI_BUS7

BPI_BUS8

BPI_BUS9

BPI_BUS10

BPI_BUS11

BPI_BUS12

BPI_BUS13

BPI_BUS14

BPI_BUS15

BSI_DATA2

BSI_DATA1

BSI_DATA0

BSI_EN

BSI_CLK

B12

B11

C12

A11

D11

C11

A13

A10

B10

D10

E9

E8

B9

B8

E7

D7

D6

C7

F9

F11

G11

ASM_VCTRL_A

ASM_VCTRL_B

ASM_VCTRL_C

WG_GGE_PA_ENABLE

GPIO_I2C_SDA

CTP_RST_2V8

GPIO_I2C_SCL

W_PA_B1_EN

W_PA_LB_EN

W_PA_B5_EN

W_PA_B8_EN

KP_LED_EN

SIM_I2C_SDA

EINT_ALSPS

SIM_I2C_SCL

BL_EN

BSI-A_DAT2

BSI-A_DAT1

BSI-A_DAT0

BSI-A_EN

BSI-A_CK

AUD_MISO

AUD_CLK

AUD_MOSI

PMIC_SPI_MOSI

PMIC_SPI_MISO

PMIC_SPI_SCK

PMIC_SPI_CS

WATCHDOG

SRCLKENA

EINT_PMIC

SIM1_SCLK

SIM1_SIO

SIM2_SCLK

SIM2_SIO

U301-D

J1

AUD_DAT_MISO

K5

AUD_CLK_MOSI

K1

AUD_DAT_MOSI

L2

PMIC_SPI_MOSI

L5

PMIC_SPI_MISO

L4

PMIC_SPI_SCK

K2

PMIC_SPI_CSN

G2

WATCHDOG

H4

SRCLKENA

J2

EINTX

H5

SIM1_SCLK

M3

SIM1_SIO

J5

SIM2_SCLK

M1

SIM2_SIO

MT6572_LPDDR2

SIM2_SRST

SIM1_SRST

FRONT_CMPDN

FRONT_CMRST

MIPI_RDN0

MIPI_RDP0

MIPI_RDN1

MIPI_RDP1

MIPI_RCN

MIPI_RCP

MIPI_TDN0

MIPI_TDP0

MIPI_TDN1

MIPI_TDP1

MIPI_TCN

MIPI_TCP

close to BB

R301

1.5K

U301-G

L25

CMPDN2

K25

CMRST2

H22

CMPDN

J22

CMRST

R24

RDN0

R23

RDP0

R22

RDN1

R21

RDP1

R26

RCN

T26

RCP

P19

TDN0

P20

TDP0

N25

TDN1

N26

TDP1

P23

TDN2

P24

TDP2

N20

TCN

N19

TCP

P26

VRT

MT6572_LPDDR2

MIPI_CAM

MIPI_LCD

MIPI_2nd_CAM

Parallel 8-bit

CMMCLK

CMPCLK

RCN_A

RCP_A

RDN1_A

RDP1_A

RDN0_A

RDP0_A

CMDAT3

CMDAT2

CMDAT1

CMDAT0

Y22

Y23

V25

W25

V24

V23

U22

U21

Y26

Y25

AA25

AB25

CMMCLK_BB

CMPCLK_BB

CMVREF

CMHREF

CMDAT7

CMDAT6

CMDAT5

CMDAT4

CMDAT3

CMDAT2

CMDAT1

CMDAT0

VDD1V8_PMU

VDD1V8_PMU

VUSB_PMU

cap Close to BB IC

C324

0402

0.1uF

dedicate VSS ball, must return to cap then to main GND:

1. REFN(G6) => C109

2. DVSS18_MIPIRX(U25) => C107

3. DVSS18_MIPITX(P25) => C101

C320

0402

0.1uF

C325

0402

0.1uF

C326

1uF6.3V

C327

1uF6.3V

T25

DVDD18_MIPIRX

U25

DVSS18_MIPIRX

R25

DVDD18_MIPITX

P25

DVSS18_MIPITX

H23

AVDD18_USB

G24

AVDD33_USB

G23

AVSS33_USB

F6

REFP

G6

REFN

MT6572_LPDDR2

AC21

GND

AD11

GND

AF13

GND

AB11

GND

AC8

GND

AB5

GND

AB14

GND

W26

GND

T15

GND

W23

GND

T14

GND

AF26

GND

G3

GND

K21

GND

L11

GND

L12

GND

L14

GND

L15

GND

L16

GND

M5

GND

M11

GND

M12

GND

M13

GND

M14

GND

M15

GND

M16

GND

N10

GND

N8

GND

N9

GND

N11

GND

N12

GND

N13

GND

N14

GND

N15

GND

N16

GND

P10

GND

N22

GND

P11

GND

P12

GND

P13

GND

P14

GND

P15

GND

P16

GND

R10

GND

R11

GND

R12

GND

R13

GND

R14

GND

R15

GND

R16

GND

T10

GND

T11

GND

T12

GND

T13

GND

AF1

VSS

U10

VSS

U11

VSS

V13

VSS

W11

VSS

Y21

VSS

U301-B

BG

U301-H

DVDD18_PLLGP

VCC

Memory

DVDD

Peripheral

VCC

CPU

VCC

Core

AVDD28_DAC

AVDD18_AP

AVDD18_MD

AVSS18_MD

AVSS18_MD

AVSS18_MD

AVSS18_MD

VCCIO_EMI

VCCIO_EMI

VCCIO_EMI

VCCIO_EMI

VCCIO_EMI

DVDD18_MC0

DVDD18_CAM

DVDD18_VIO_1

DVDD18_VIO_2

DVDD18_VIO_3

DVDD18_LCD

DVDD3_MC1

DVDD3_LCD

DVDD28_BPI

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK_CPU

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

VCCK

F1

E5

U9

D3

A1

A4

C3

E2

W9

W12

W14

W16

W19

AA1

K20

L3

J19

H13

AB24

K24

W24

C10

P6

T7

P7

P8

P9

R6

R7

R8

R9

T6

U6

T9

T8

U7

J9

J15

M9

K6

K7

K8

K9

K11

K14

K15

M10

K16

K17

U17

M17

L7

L8

L9

L17

M6

M7

M8

J17

J16

R17

T16

L6

K12

T17

J10

J11

U12

U13

U14

U15

U16

J8

J14

0402

cap Close to BB IC

C321

0402

0.1uF

C329

0.1uF

C306

1uF6.3V

Close to BB IC, recommand < 150mil

VTCXO_PMU

VDD1V8_PMU

VDD1V8_PMU

C322

0402

0.1uF

C323

0402

0.1uF

If double-sided SMT, put C301 & C302 below BB.

If single-sided SMT, put C301 & C302 around memory.

DVDD_EMI

C303

C307

C308

C309

C331

0201

0402

0402

0402

0402

0402

C332

100nf

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

C301

0201

100nf

0201

C302

100nf

C310

C311

C312

C313

VMC_PMU

VDD2V8_PMU

1uF6.3V

1uF6.3V

1uF6.3V

1uF6.3V

C314

2.2uF

C305

1uF6.3V

C315

2.2uF

0R

R307

C304

1uF6.3V

Based on your system level

design , if better FM performance

is needed on your system ,

please refer to FM desense

performance enhance proposal

C316

4.7uF

C317

10UF6.3V

C318

10UF6.3V

C319

10UF6.3V

VDD1V8_PMU

120MIL

VPROC_PMU

VDD1V8_PMU

BACK_CMPDN

BACK_CMRST

R302

close to BB

5.1K

100K

R308

90-ohm differential

2.2K

2.2K

R305

R306

100K

R309

SCL_0

SDA_0

SCL_1

SDA_1

CLK1_BB

CLK32K_BB

RESETB

CHD_DP

CHD_DM

USB_DM

USB_DP

MSDC1_CMD

MSDC1_CLK

MSDC1_DAT0

MSDC1_DAT1

MSDC1_DAT2

MSDC1_DAT3

0402

C330

100pF

U301-E

E1

CLK26M

H2

CLK32K_IN

M2

SYSRSTB

G4

TESTMODE

AC24

FSOURCE

J26

CHD_DP

J25

CHD_DM

G26

USB_DM

G25

USB_DP

H25

USB_VRT

C25

SCL_0

C26

SDA_0

B24

SCL_1

B23

SDA_1

F24

SPI_MISO

F25

SPI_MOSI

F23

SPI_SCK

E23

SPI_CS

K23

MC1_CMD

L21

MC1_CK

K22

MC1_DAT0

M22

MC1_DAT1

M25

MC1_DAT2

L26

MC1_DAT3

B7

AUX_IN0

B6

AUX_IN1

C5

AUX_IN2_XP

B5

AUX_IN3_YP

C4

AUX_IN4_XM

A5

AUX_IN5_YM

MT6572_LPDDR2

SYSTEM

BC 1.1

USB 2.0

i2C

SPI

T-flash

ADC

PWM

LCD

Parallel

KP

UART

PWM_A

PWM_B

LPD17

LPD16

LPD15

LPD14

LPD13

LPD12

LPD11

LPD10

LPD9

LPD8

LPD7

LPD6

LPD5

LPD4

LPD3

LPD2

LPD1

LPD0

LPCE0B

LPTE

LRSTB

LPRDB

LPA0

LPWRB

KROW0

KROW1

KROW2

KCOL0

KCOL1

KCOL2

UTXD1

URXD1

UTXD2

URXD2

D12

E12

N1

N2

N3

P2

N4

R2

N5

R1

P5

T1

R5

T2

T5

U2

T3

U5

T4

V2

AD25

AB26

AC26

AA22

AB23

AC25

B25

A24

B26

C24

D24

A25

E25

D25

E26

F26

CTP_EINT_1V8

LPTE

LCM_RST

EINT_HP

CTP_RST_1V8

KROW0

KCOL0

KCOL1

AUDIO_PA_EN

UTXD1

URXD1

UTXD2

URXD2

A26

DUMMY

MT6572_LPDDR2

Title

BB- Power

Size Document Number Rev

A1

Date: Sheet of 93

Wednesday, January 02, 2013

MT6572 REF PHONE

1

V1.0

Loading...

Loading...