Casio JD5000 Service Manual

(without price)

JD-5000(LX-171)

JUL. 1993

JD-5000(BU)

INDEX

R

CONTENTS

1. |

SCHEMATIC DIAGRAM................................................................................................ |

1 |

2. |

SPECIFICATIONS ......................................................................................................... |

3 |

3. |

LSI PIN FUNCTION ....................................................................................................... |

4 |

4. |

OPERATION CHECK .................................................................................................... |

7 |

5. |

TO SAVE THE DATA TO OTHER MACHINE ............................................................... |

8 |

6. |

EXPLODED VIEW ....................................................................................................... |

11 |

7. |

PARTS LIST ................................................................................................................ |

13 |

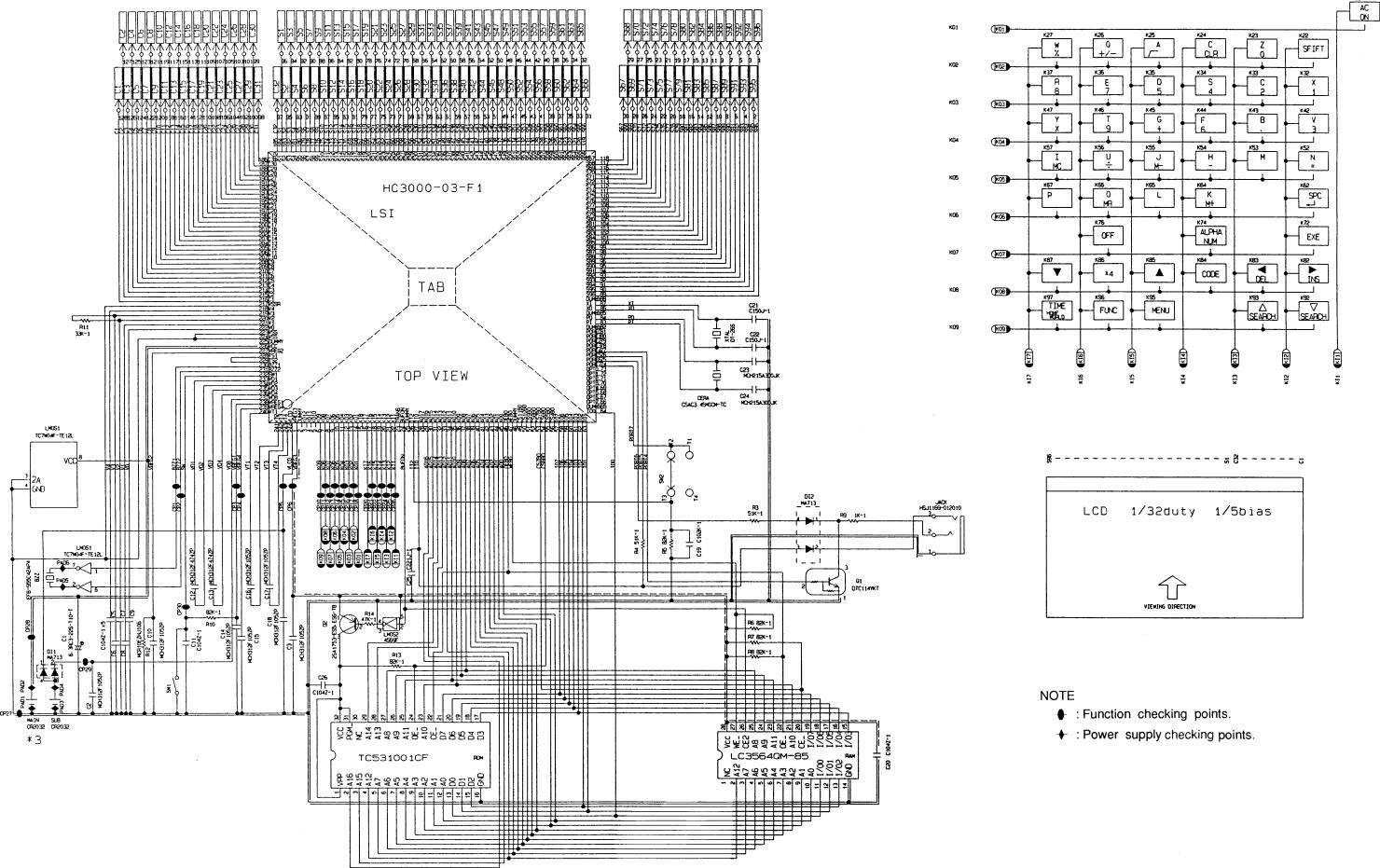

1.SCHEMATIC DIAGRAM

2. SPECIFICATIONS

Display: |

Liquid crystal display |

|

Memory Capacity: |

6,144 bytes |

|

Power Supply: |

Two lithium batteries (CR2032) ... Main and Back-up |

|

Power Consumption: |

0.05W |

|

Battery Life: |

Main battery: |

Approximately 7,000 hours (1 hour use per |

|

|

day) |

|

Back-up battery: Approximately 3 years after the low main |

|

|

|

battery warning appears on the display |

Auto Power Off: |

Approximately 6 minutes after last key operation |

|

Ambient Temperature |

0°C ~ 40°C (32°F ~ 104°F) |

|

Range: |

||

Dimensions: |

Open: |

9.3(H) × 145(W) × 163(D) mm |

|

|

(3/8"(H) × 5 3/4"(W) × 6 3/8"(D)) |

|

Closed: |

13.9(H) × 145(W) × 84(D) mm |

|

|

(1/2"(H) × 5 3/4 "(W) × 3 1/4"(D)) |

Weight: |

112 g(4 oz) including batteries |

|

— 3 —

3.LSI PIN FUNCTION

1. CPU (HC3000-03-F1)

Pin No. |

Signal |

In/Out |

Function |

|

|

|

|

|

|

|

1 |

VREG3 |

Out |

Power supply for RAM / 3(V) |

|

|

|

|

|

|

2 |

DMY |

– |

Not used |

|

|

|

|

|

3 |

~ 5 |

KO10 ~ 12 |

Out |

Not used |

|

|

|

|

|

6 ~ 14 |

KO1 ~ 9 |

Out |

Key scan signal |

|

|

|

|

|

|

|

15 |

KI8 |

In |

Not used |

|

|

|

|

|

16 |

~ 22 |

KI1~7 |

In |

Key input signal |

|

|

|

|

|

23 , 25 |

TRANS, DUMMY |

– |

Not used |

|

|

|

|

|

|

|

24 |

DUFON |

Out |

Power supply control for ROM |

|

|

|

|

|

|

26 |

IT2 |

In |

Battery switch position sensor |

|

|

|

|

|

|

27 |

IT0 |

In |

Reception data input |

|

|

|

|

|

|

28 |

AO17 |

Out |

Not used |

|

|

|

|

|

29 |

~ 45 |

A0 ~ A16 |

Out |

Address bus |

|

|

|

|

|

|

46 |

OEB0 |

Out |

Output enable signal for RAM and ROM |

|

|

|

|

|

|

47 |

WEB0 |

Out |

Write enable signal for RAM |

|

|

|

|

|

48 |

~ 52 |

|

– |

Not used |

|

|

|

|

|

|

53 |

CS7B0 |

Out |

Chip enable signal for RAM |

|

|

|

|

|

|

54 |

CS6 |

Out |

Chip enable signal for ROM |

|

|

|

|

|

55, 56 |

|

Out |

Not used |

|

|

|

|

|

|

57 |

~ 64 |

IO0 ~ IO7 |

In/Out |

Data bus |

|

|

|

|

|

65 |

~ 73 |

|

– |

Not used |

|

|

|

|

|

|

74 |

PORT7 |

– |

Battery switch on: "L" / 0[V] |

|

|

|

|

off: "H" / 5[V] |

|

|

|

|

|

— 4 —

Loading...

Loading...