BOSCH E-Ray User Manual

E-Ray |

User’s Manual |

Revision 1.2.5 |

E-Ray

FlexRay IP-Module

User’s Manual

Revision 1.2.5

15.12.2006

manual_cover.fm

Robert Bosch GmbH

Automotive Electronics

- 1/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

Copyright Notice

Copyright © 2002-2006 Robert Bosch GmbH. All rights reserved. This manual is owned by Robert Bosch GmbH. No part of this publication may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Robert Bosch GmbH, or as expressly provided by the license agreement.

Disclaimer

ROBERT BOSCH GMBH, MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

ROBERT BOSCH GMBH, RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO THE PRODUCTS DESCRIBED HEREIN. ROBERT BOSCH GMBH DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN.

manual_cover.fm

- 2/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

manualTOC.fm

Contents

1. About this Document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.1 Change Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.1.1 Current Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.1.2 Change History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.2 Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.3 Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.4 Scope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.5 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.6 Terms and Abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3. Generic Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4. Programmer’s Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.1 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.2 Customer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

4.3 Special Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.3.1 Lock Register (LCK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.4 Interrupt Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.4.1 Error Interrupt Register (EIR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 4.4.2 Status Interrupt Register (SIR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

4.4.3 Error Interrupt Line Select (EILS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 4.4.4 Status Interrupt Line Select (SILS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 4.4.5 Error Interrupt Enable Set / Reset (EIES, EIER) . . . . . . . . . . . . . . . . . . . . 33 4.4.6 Status Interrupt Enable Set / Reset (SIES, SIER) . . . . . . . . . . . . . . . . . . . 34 4.4.7 Interrupt Line Enable (ILE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 4.4.8 Timer 0 Configuration (T0C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

4.4.9 Timer 1 Configuration (T1C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.4.10 Stop Watch Register 1 (STPW1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 4.4.11 Stop Watch Register 2 (STPW2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

4.5 CC Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

4.5.1 SUC Configuration Register 1 (SUCC1) . . . . . . . . . . . . . . . . . . . . . . . . . . . 40 4.5.2 SUC Configuration Register 2 (SUCC2) . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

4.5.3 SUC Configuration Register 3 (SUCC3) . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

4.5.4 NEM Configuration Register (NEMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

4.5.5 PRT Configuration Register 1 (PRTC1) . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

4.5.6 PRT Configuration Register 2 (PRTC2) . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

- 3/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

manualTOC.fm

4.5.7 MHD Configuration Register (MHDC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

49 |

|

4.5.8 GTU Configuration Register 1 (GTUC1) . . . . . . . . . . . . . . . . . . . . . . . . . . . |

50 |

|

4.5.9 GTU Configuration Register 2 (GTUC2) . . . . . . . . . . . . . . . . . . . . . . . . . . . |

50 |

|

4.5.10 GTU Configuration Register 3 (GTUC3) . . . . . . . . . . . . . . . . . . . . . . . . . . |

51 |

|

4.5.11 GTU Configuration Register 4 (GTUC4) . . . . . . . . . . . . . . . . . . . . . . . . . . |

52 |

|

4.5.12 GTU Configuration Register 5 (GTUC5) . . . . . . . . . . . . . . . . . . . . . . . . . . |

53 |

|

4.5.13 GTU Configuration Register 6 (GTUC6) . . . . . . . . . . . . . . . . . . . . . . . . . . |

53 |

|

4.5.14 GTU Configuration Register 7 (GTUC7) . . . . . . . . . . . . . . . . . . . . . . . . . . |

54 |

|

4.5.15 GTU Configuration Register 8 (GTUC8) . . . . . . . . . . . . . . . . . . . . . . . . . . |

54 |

|

4.5.16 GTU Configuration Register 9 (GTUC9) . . . . . . . . . . . . . . . . . . . . . . . . . . |

55 |

|

4.5.17 GTU Configuration Register 10 (GTUC10) . . . . . . . . . . . . . . . . . . . . . . . . |

55 |

|

4.5.18 GTU Configuration Register 11 (GTUC11) . . . . . . . . . . . . . . . . . . . . . . . . |

56 |

|

4.6 CC Status Registers . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

57 |

4.6.1 CC Status Vector (CCSV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

57 |

|

4.6.2 CC Error Vector (CCEV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

60 |

|

4.6.3 Slot Counter Value (SCV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

61 |

|

4.6.4 Macrotick and Cycle Counter Value (MTCCV) . . . . . . . . . . . . . . . . . . . . . . |

61 |

|

4.6.5 Rate Correction Value (RCV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

62 |

|

4.6.6 Offset Correction Value (OCV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

62 |

|

4.6.7 Sync Frame Status (SFS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

63 |

|

4.6.8 Symbol Window and NIT Status (SWNIT) . . . . . . . . . . . . . . . . . . . . . . . . . |

64 |

|

4.6.9 Aggregated Channel Status (ACS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

66 |

|

4.6.10 Even Sync ID [1… |

15] (ESIDn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

68 |

4.6.11 Odd Sync ID [1… |

15] (OSIDn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

69 |

4.6.12 Network Management Vector [1… 3] (NMVn) . . . . . . . . . . . . . . . . . . . . . . |

70 |

|

4.7 Message Buffer Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

71 |

|

4.7.1 Message RAM Configuration (MRC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71 4.7.2 FIFO Rejection Filter (FRF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73 4.7.3 FIFO Rejection Filter Mask (FRFM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74 4.7.4 FIFO Critical Level (FCL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

4.8 Message Buffer Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

4.8.1 Message Handler Status (MHDS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75 4.8.2 Last Dynamic Transmit Slot (LDTS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76 4.8.3 FIFO Status Register (FSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77 4.8.4 Message Handler Constraints Flags (MHDF) . . . . . . . . . . . . . . . . . . . . . . . 78

4.8.5 Transmission Request 1/2/3/4 (TXRQ1/2/3/4) . . . . . . . . . . . . . . . . . . . . . . 80

4.8.6 New Data 1/2/3/4 (NDAT1/2/3/4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81 4.8.7 Message Buffer Status Changed 1/2/3/4 (MBSC1/2/3/4) . . . . . . . . . . . . . . 82

4.9 Identification Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

83 |

4.9.1 Core Release Register (CREL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

83 |

4.9.2 Endian Register (ENDN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

83 |

- 4/165 - |

15.12.2006 |

manualTOC.fm

E-Ray |

User’s Manual |

Revision 1.2.5 |

4.10 Input Buffer . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . 84 |

4.10.1 Write Data Section [1… 64] (WRDSn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84 4.10.2 Write Header Section 1 (WRHS1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85 4.10.3 Write Header Section 2 (WRHS2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86 4.10.4 Write Header Section 3 (WRHS3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86 4.10.5 Input Buffer Command Mask (IBCM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

4.10.6 Input Buffer Command Request (IBCR) . . . . . . . . . . . . . . . . . . . . . . . . . . 88

4.11 Output Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

4.11.1 Read Data Section [1… 64] (RDDSn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

89 |

4.11.2 Read Header Section 1 (RDHS1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

90 |

4.11.3 Read Header Section 2 (RDHS2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

91 |

4.11.4 Read Header Section 3 (RDHS3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

92 |

4.11.5 Message Buffer Status (MBS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

93 |

4.11.6 Output Buffer Command Mask (OBCM) . . . . . . . . . . . . . . . . . . . . . . . . . . |

96 |

4.11.7 Output Buffer Command Request (OBCR) . . . . . . . . . . . . . . . . . . . . . . . |

97 |

5. Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

5.1 Communication Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

5.1.1 Static Segment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

5.1.2 Dynamic Segment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

5.1.3 Symbol Window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

5.1.4 Network Idle Time (NIT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

5.1.5 Configuration of NIT Start and Offset Correction Start . . . . . . . . . . . . . . . 100

5.2 Communication Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.2.1 Time-triggered Distributed (TT-D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.3 Clock Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

5.3.1 Global Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

5.3.2 Local Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

5.3.3 Synchronization Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

5.3.3.1 Offset (phase) Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

5.3.3.2 Rate (frequency) Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

5.3.3.3 Sync Frame Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

5.3.4 External Clock Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

5.4 Error Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

5.4.1 Clock Correction Failed Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

104 |

5.4.2 Passive to Active Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

105 |

5.4.3 HALT Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

105 |

5.4.4 FREEZE Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

105 |

5.5 Communication Controller States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

5.5.1 Communication Controller State Diagram . . . . . . . . . . . . . . . . . . . . . . . . 106

5.5.2 DEFAULT_CONFIG State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

- 5/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

manualTOC.fm

5.5.3 CONFIG State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

5.5.4 MONITOR_MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

5.5.5 READY State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

5.5.6 WAKEUP State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

5.5.6.1 Host activities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112 5.5.6.2 Wakeup pattern (WUP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

5.5.7 STARTUP State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

5.5.7.1 Coldstart Inhibit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116 5.5.7.2 Startup Timeouts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116 5.5.7.3 Path of leading Coldstart Node (initiating coldstart) . . . . . . . . . . . . . . . . . 117 5.5.7.4 Path of following Coldstart Node (responding to leading Coldstart Node) 118 5.5.7.5 Path of Non-coldstart Node . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

5.5.8 NORMAL_ACTIVE State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

5.5.9 NORMAL_PASSIVE State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

5.5.10 HALT State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

5.6 Network Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

5.7 Filtering and Masking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

5.7.1 Slot Counter Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

5.7.2 Cycle Counter Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

5.7.3 Channel ID Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

5.7.4 FIFO Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

5.8 Transmit Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

5.8.1 Static Segment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

5.8.2 Dynamic Segment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

5.8.3 Transmit Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

5.8.4 Frame Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

5.8.5 Null Frame Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

5.9 Receive Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

5.9.1 Dedicated Receive Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

5.9.2 Frame Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

5.9.3 Null Frame Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

5.10 FIFO Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

5.10.1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129 5.10.2 Configuration of the FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

5.10.3 Access to the FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

5.11 Message Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

5.11.1 |

Reconfiguration of Message Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . |

131 |

5.11.2 |

Host access to Message RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

133 |

5.11.2.1 Data Transfer from Input Buffer to Message RAM . . . . . . . . . . . . . . . . . 134 5.11.2.2 Data Transfer from Message RAM to Output Buffer . . . . . . . . . . . . . . . 136

5.11.3 FlexRay Protocol Controller access to Message RAM . . . . . . . . . . . . . . 139

5.12 Message RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

- 6/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

5.12.1 Header Partition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

5.12.2 Data Partition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

5.12.3 Parity Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

5.13 Module Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

6. Appendix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

6.1 Register Bit Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150 6.2 Assignment of FlexRay Configuration Parameters . . . . . . . . . . . . . . . . . . . . . 162

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

manualTOC.fm

- 7/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

manual_about.fm

1. About this Document

1.1Change Control

1.1.1Current Status

Revision 1.2.5

1.1.2 Change History |

|

|

|

Issue |

Date |

By |

Change |

Revision 1.0 |

29.10.04 |

C. Horst |

First complete revision |

Revision 1.0.1 |

16.11.04 |

C. Horst |

Message Buffer Status bits PLE, MLST, ES |

|

|

|

replaced by bits ESA, ESB, MLST |

Revision 1.0.2 |

28.01.05 |

C. Horst |

IBCR, IBCM, OBCR, OBCM: addresses changed |

|

|

|

MHDC2: register removed |

|

|

|

MHDC1: renamed to MHDC |

|

|

|

Message buffer 0 dedicated to hold key slot ID |

|

|

|

SFS: description updated |

|

|

|

ESIDn, OSIDn: description updated |

|

|

|

EIR: bit SCE removed |

|

|

|

EILS: bit SCEL removed |

|

|

|

EIES, EIER: bit SCEE removed |

Revision 1.1 |

29.04.05 |

C. Horst |

State DEFAULT_CONFIG added to POC |

working |

|

|

CCSV: assignment of states to POCS[5:0] changed: |

|

|

|

POCS[5:0] = 00 0000 = DEFAULT_CONFIG |

|

|

|

POCS[5:0] = 00 1111 = CONFIG |

|

|

|

CCSV: bit DCREQ removed |

|

|

|

SIR: bit MBSI added |

|

|

|

SILS: bit MBSIL added |

|

|

|

SIES, SIER: bit MBSIE added |

|

|

|

Register BGSC removed |

|

|

|

EIR: bits SMEB, SMEA removed |

|

|

|

EILS: bits SMEBL, SMEAL removed |

|

|

|

EIES, EIER: bits SMEBE, SMEAE removed |

|

|

|

Registers TXRQ3, TXRQ4, NDAT3, NDAT4, |

|

|

|

MBSC3, MBSC4 added |

|

|

|

Bus guardian related pins eray_arm, eray_bgt, |

|

|

|

eray_mt, eray_bge1, and eray_bge2 have no function |

|

|

|

PRTC1: Configuration parameter CASM[6:0] added |

|

|

|

WRHS1: Bit NME changed to PPIT |

|

|

|

RDHS1: Bit NME changed to PPIT |

|

|

|

Pin eray_scanmode for scan mode control added |

Revision 1.1 |

04.08.05 |

C. Horst |

EIR: Flags CCL, EFA, IIBA, IOBA, TABA, |

|

|

|

TABB added |

|

|

|

SIR: Flag SDS added |

EILS: Control bits CCLL, EFAL, IIBAL, IOBAL,

TABAL, TABBL added

SILS: Control bit SDSL added

- 8/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

manual_about.fm

|

|

EIES: Control bits CCLE, EFAE, IIBAE, IOBAE, |

|

|

TABAE, TABBE added |

|

|

EIER: Control bits CCLE, EFAE, IIBAE, IOBAE, |

|

|

TABAE, TABBE added |

|

|

SIES: Control bit SDSE added |

|

|

SIER: Control bit SDSE added |

|

|

SUCC2: LT[20:0] range modified |

|

|

PRTC1: TSST[3:0] range modified, SPP[1:0] added, |

|

|

configuration of BRP[1:0] for 1.25 MBit/s removed |

|

|

PRTC2: RXL[5:0] range modified |

|

|

MHDC: SLT[12:0] range modified |

|

|

GTUC1: UT[19:0] range modified |

|

|

GTUC2: MPC[13:0] range modified |

|

|

GTUC3: Configuration parameter MTIO[5:0] replaced |

|

|

by MIOA[6:0] and MIOB[6:0] |

|

|

GTUC4: NIT[13:0] and OCS[13:0] range modified |

|

|

GTUC5: DEC[7:0] range modified |

|

|

GTUC7: SSL[9:0] range modified |

|

|

GTUC8: NMS[12:0] range modified |

|

|

GTUC9: APO[5:0] and DSI[1:0] range modified |

|

|

GTUC10: MOC[13:0] range modified |

|

|

GTUC11: Configuration parameter ECC[1:0] replaced |

|

|

by EOCC[1:0] and ERCC[1:0] |

|

|

OCV: OCV[18:0] range modified |

|

|

SCV: SCCA[10:0], SCCB[10:0] range modified |

|

|

ACS: Flags can only be reset |

|

|

MRC: Configuration bits SEC[1:0] added |

|

|

Register LDTS added |

|

|

Bus guardian related pins eray_arm, eray_bgt, |

|

|

eray_mt, eray_bge1, and eray_bge2 removed from |

|

|

physical layer interface |

|

|

Chapter 6. Restrictions removed. Description of timing |

|

|

requirements for data transfers between Message RAM |

|

|

and IBF / OBF moved to "Addendum to E-Ray |

|

|

FlexRay IP-Module Specification Revision 1.1" |

Revision 1.2 |

09.12.05 C. Horst |

Section 3.2 renamed from "Interrupt Flag Interface" to |

|

|

"Internal Signal and Flag Interface" |

|

|

With this revision it is possible to use message buffer 1 |

|

|

for sync frame transmission in addition to message |

|

|

buffer 0 if sync frames should have different payloads |

|

|

on channel A and B |

|

|

EIR: Handling of bits PERR and RFO same as for |

|

|

other bits, bit MHF added |

|

|

SIR: Bit RFF renamed to RFCL, handling of bits |

|

|

RFNE, RFCL same as for other bits |

|

|

EILS: Bit MHFL added |

|

|

SILS: Bit RFFL renamed to RFCLL |

|

|

EIES, EIER: Bit MHFE added |

|

|

SIES, SIER: Bit RFFE renamed to RFCLE |

- 9/165 - |

15.12.2006 |

E-Ray |

|

|

User’s Manual |

Revision 1.2.5 |

|

|

|

Register STPW renamed to STPW1 |

|

|

|

|

STPW2: Register added |

|

|

|

|

CCSV: Bits PSL[5:0] added |

|

|

|

|

SWNIT: Bits MTSA, MTSB added |

|

|

|

|

MRC: Bit SPLM added |

|

|

|

|

FCL: Register added |

|

|

|

|

FSR: Register added |

|

|

|

|

MHDF: Register added |

|

|

|

|

MBSC1/2/3/4: Naming of bits changed from MBS to |

|

|

|

|

MBC to distinguish between message buffer status flag |

|

|

|

|

(MBC) and message buffer status register (MBS) |

|

|

|

|

CREL: Register added |

|

|

|

|

ENDN: Register added |

|

|

|

|

Message buffers in Message RAM: |

|

|

|

|

Header 2 and 3 updated from received data frames only |

|

|

|

|

MBS: Bits FTA, FTB, CCS[5:0], RCIS, SFIS, SYNS, |

|

|

|

|

NFIS, PPIS, RESS added |

|

Revision 1.2.1 |

17.03.06 |

C. Horst |

All changes to previous release are described in |

|

|

|

|

detail in [5]. |

|

Revision 1.2.2 |

19.05.06 |

C. Horst |

All changes to previous release are described in |

|

|

|

|

detail in [6]. |

|

Revision 1.2.3 |

15.08.06 |

C. Horst |

All changes to previous release are described in |

|

|

|

|

detail in [7]. |

|

Revision 1.2.4 |

|

|

Not published. |

|

Revision 1.2.5 |

15.12.06 |

C. Horst |

All changes to previous release are described in |

|

|

|

|

detail in [8], [9]. |

|

manual_about.fm

- 10/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

manual_about.fm

1.2 Conventions

The following conventions are used within this document:

Times bold Names of bits and signals

CAPITALS POC states and CHI commands

1.3 Definitions

FlexRay Frame: Header Segment + Payload Segment

Message Buffer: Header Section + Data Section

Message RAM: Header Partition + Data Partition

Data Frame: |

FlexRay frame that is not a null frame |

1.4 Scope

This document describes the E-Ray FlexRay IP-module and its features from the application programmer’s point of view. All information necessary to integrate the E-Ray module into an user-defined ASIC is located in the Module Integration Guide. Information about a specific Customer CPU Interface can be found in the respective Customer CPU Interface Specification document.

1.5 References

This document refers to the following E-Ray release:

Revision 1.0.1

This document refers to the following documents:

Ref |

Author(s) |

Title |

[1] |

FlexRay Group |

FlexRay Communication System Protocol Specification v2.1 (05/05/12) |

[2] |

FlexRay Group |

FlexRay Communication System Protocol Specification v2.1 Revision A |

|

|

Errata Sheet Version 1 (06/03/29) |

[3] |

FlexRay Group |

FlexRay Data Link Layer Conformance Test Specification v2.1 (06/03/27) |

[4] |

AE/EIP |

Addendum to E-Ray FlexRay IP-Module Specification Revision 1.2.2 |

[5] |

AE/EIP |

Changes E-Ray FlexRay IP-Module Specification v1.2 to v1.2.1 |

[6] |

AE/EIP |

Changes E-Ray FlexRay IP-Module Specification v1.2.1 to v1.2.2 |

[7] |

AE/EIP |

Changes E-Ray FlexRay IP-Module Specification v1.2.2 to v1.2.3 |

[8] |

AE/EIP |

Changes E-Ray FlexRay IP-Module Specification v1.2.3 to v1.2.4 |

[9] |

AE/EIP |

Changes E-Ray FlexRay IP-Module Specification v1.2.4 to v1.2.5 |

- 11/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

manual_about.fm

1.6 Terms and Abbreviations

This document uses the following terms and abbreviations:

Term |

Meaning |

AP |

Action Point |

BD |

Bus Driver |

BSS |

Byte Start Sequence |

CAS |

Collision Avoidance Symbol |

CC |

Communication Controller |

CHI |

Controller Host Interface |

CIF |

Customer Interface Block |

CRC |

Cyclic Redundancy Check |

FES |

Frame End Sequence |

FSS |

Frame Start Sequence |

FIFO |

First In First Out (message buffer structure) |

FSM |

Finite State Machine |

FSP |

Frame and Symbol Processing Block |

FTM |

Fault Tolerant Midpoint |

GIF |

Generic Interface Block |

GTU |

Global Time Unit Block |

IBF |

Input Buffer |

INT |

Interrupt Control Block |

MHD |

Message Handler Block |

MT |

Macrotick |

MTS |

Media Access Test Symbol |

NCT |

Network Communication Time |

NEM |

Network Management Block |

NIT |

Network Idle Time |

NM |

Network Management |

OBF |

Output Buffer |

POC |

Protocol Operation Control |

PRT |

Protocol Controller Block |

SDL |

Specification and Description Language |

SUC |

System Universal Control Block |

TBF |

Transient Buffer |

TDMA |

Time Division Multiple Access (media access method) |

- 12/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

TSS |

Transmission Start Sequence |

|

TT-D |

Time Triggered Distributed Synchronization |

|

T |

Microtick |

|

WUP |

Wakeup Pattern |

|

WUS |

Wakeup Symbol |

|

manual_about.fm

- 13/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

manual_overview.fm

2. Overview

The E-Ray module is a FlexRay IP-module that can be integrated as stand-alone device or as part of an ASIC. It is described in VHDL on RTL level, prepared for synthesis. The E-Ray IP-module performs communication according to the FlexRay protocol specification v2.1. With maximum specified sample clock the bitrate is 10 MBit/s. Additional bus driver (BD) hardware is required for connection to the physical layer.

For communication on a FlexRay network, individual message buffers with up to 254 data bytes are configurable. The message storage consists of a single-ported Message RAM that holds up to 128 message buffers. All functions concerning the handling of messages are implemented in the Message Handler. Those functions are the acceptance filtering, the transfer of messages between the two FlexRay Channel Protocol Controllers and the Message RAM, maintaining the transmission schedule as well as providing message status information.

The register set of the E-Ray IP-module can be accessed directly by an external Host via the module’s Host interface. These registers are used to control/configure/monitor the FlexRay Channel Protocol Controllers, Message Handler, Global Time Unit, System Universal Control, Frame and Symbol Processing, Network Management, Interrupt Control, and to access the Message RAM via Input / Output Buffer.

The E-Ray IP-module can be connected to a wide range of customer-specific Host CPUs via its 8/16/32-bit Generic CPU Interface.

The E-Ray IP-module supports the following features:

•Conformance with FlexRay protocol specification v2.1

•Data rates of up to 10 Mbit/s on each channel

•Up to 128 message buffers configurable

•8 Kbyte of Message RAM for storage of e.g. 128 message buffers with max. 48 byte data section or up to 30 message buffers with 254 byte data section

•Configuration of message buffers with different payload lengths possible

•One configurable receive FIFO

•Each message buffer can be configured as receive buffer, as transmit buffer or as part of the receive FIFO

•Host access to message buffers via Input and Output Buffer

Input Buffer: |

Holds message to be transferred to the Message RAM |

Output Buffer: |

Holds message read from the Message RAM |

•Filtering for slot counter, cycle counter, and channel

•Maskable module interrupts

•Network Management supported

•8/16/32-bit Generic CPU Interface, connectable to a wide range of customer-specific Host CPUs

- 14/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

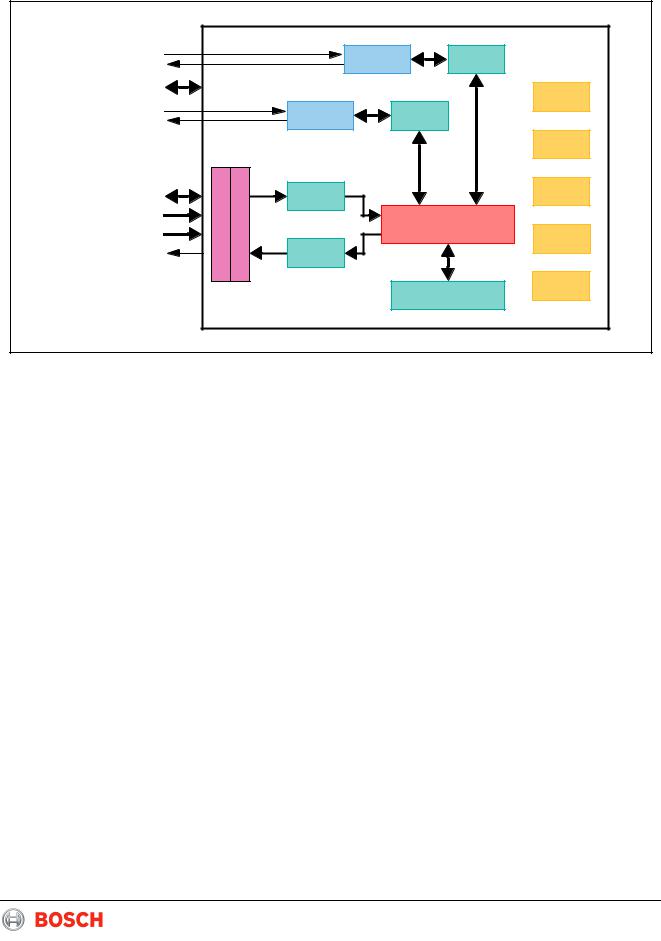

2.1 Block Diagram

|

Rx_A |

|

PRT A |

TBF A |

|

|

Tx_A |

|

|||

Physical |

|

|

|

||

Control |

|

|

|

||

Layer |

|

|

GTU |

||

Rx_B |

|

|

|||

|

|

|

|||

|

|

PRT B |

TBF B |

||

|

Tx_B |

|

|||

|

|

|

|

||

|

|

|

|

SUC |

|

|

Data |

Customer CPU IF |

IBF |

FSP |

|

Host |

Addr |

Message Handler |

|||

CPU |

Control |

||||

|

NEM |

||||

|

Interrupt |

OBF |

|||

|

|

||||

|

|

GenericCPUIF |

INT |

||

|

|

|

|

Message RAM |

|

manual_overview.fm

Figure 1: E-Ray block diagram

Customer CPU Interface (CIF)

Connects a customer specific Host CPU to the E-Ray IP-module via the Generic CPU Interface.

Generic CPU Interface (GIF)

The E-Ray IP-module is provided with an 8/16/32-bit Generic CPU Interface prepared for the connection to a wide range of customer-specific Host CPUs. Configuration registers, status registers, and interrupt registers are attached to the respective blocks and can be accesssed via the Generic CPU Interface.

Input Buffer (IBF)

For write access to the message buffers configured in the Message RAM, the Host can write the header and data section for a specific message buffer to the Input Buffer. The Message Handler then transfers the data from the Input Buffer to the selected message buffer in the Message RAM.

Output Buffer (OBF)

For read access to a message buffer configured in the Message RAM the Message Handler transfers the selected message buffer to the Output Buffer. After the transfer has completed, the Host can read the header and data section of the transferred message buffer from the Output Buffer.

Message Handler (MHD)

The E-Ray Message Handler controls data transfers between the following components:

•Input / Output Buffer and Message RAM

•Transient Buffer RAMs of the two FlexRay Protocol Controllers and Message RAM

- 15/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

manual_overview.fm

Message RAM (MRAM)

The Message RAM consists of a single-ported RAM that stores up to 128 FlexRay message buffers together with the related configuration data (header and data partition).

Transient Buffer RAM (TBF A/B)

Stores the data section of two complete messages.

FlexRay Channel Protocol Controller (PRT A/B)

The FlexRay Channel Protocol Controllers consist of shift register and FlexRay protocol FSM. They are connected to the Transient Buffer RAMs for intermediate message storage and to the physical layer via bus driver BD.

They perform the following functionality:

•Control and check of bit timing

•Reception / transmission of FlexRay frames and symbols

•Check of header CRC

•Generation / check of frame CRC

•Interfacing to bus driver

The FlexRay Channel Protocol Controllers have interfaces to:

•Physical Layer (bus driver)

•Transient Buffer RAM

•Message Handler

•Global Time Unit

•System Universal Control

•Frame and Symbol Processing

•Network Management

•Interrupt Control

Global Time Unit (GTU)

The Global Time Unit performs the following functions:

•Generation of microtick

•Generation of macrotick

•Fault tolerant clock synchronization by FTM algorithm

-rate correction

-offset correction

•Cycle counter

•Timing control of static segment

•Timing control of dynamic segment (minislotting)

•Support of external clock correction

- 16/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

System Universal Control (SUC)

The System Universal Control controls the following functions:

•Configuration

•Wakeup

•Startup

•Normal Operation

•Passive Operation

•Monitor Mode

Frame and Symbol Processing (FSP)

The Frame and Symbol Processing controls the following functions:

•Checks the correct timing of frames and symbols

•Tests the syntactical and semantical correctness of received frames

•Sets the slot status flags

Network Management (NEM)

Handles the network management vector.

Interrupt Control (INT)

The Interrupt Controller performs the following functions:

•Provides error and status interrupt flags

•Enable / disable interrupt sources

•Assignment of interrupt sources to one of the two module interrupt lines

•Enable / disable module interrupt lines

•Manages the two interrupt timers

•Stop watch time capturing

manual_overview.fm

- 17/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

3. Generic Interface

The Generic Interface encapsulates the synthesizable code of the E-Ray design (E-Ray core). All customer specific components like Customer CPU Interfaces and RAM blocks are connected to the Generic Interface.

The Generic CPU Interface connects the E-Ray module to a customer specific Host CPU via the Customer CPU Interface. It supports 8/16/32-bit access modes.

manual_generic_if.fm

- 18/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

manual_programmers_model.fm

4. Programmer’s Model

4.1 Register Map

The E-Ray module allocates an address space of 2 Kbytes (0x0000 to 0x07FF). The registers are organized as 32-bit registers. 8/16-bit accesses are also supported. Host access to the Message RAM is done via the Input and Output Buffers. They buffer data to be transferred to and from the Message RAM under control of the Message Handler, avoiding conflicts between Host accesses and message reception / transmission. Addresses 0x0000 to 0x000F are reserved for customer specific purposes. All functions related to these addresses are located in the Customer CPU Interface.

The assignment of the message buffers is done according to the scheme shown in Table 1 below. The number N of available message buffers depends on the payload length of the configured message buffers. The maximum number of message buffers is 128. The maximum payload length supported is 254 bytes.

The message buffers are separated into three consecutive groups:

• Static Buffers |

- Transmit / receive buffers assigned to static segment |

• Static + Dynamic Buffers - Transmit / receive buffers assigned to static or dynamic segment

• FIFO |

- Receive FIFO |

The message buffer separation configuration can be changed only in DEFAULT_CONFIG or CONFIG state only by programming register MRC (see 4.7.1 Message RAM Configuration (MRC)).

The first group starts with message buffer 0 and consists of static message buffers only. Message buffer 0 is dedicated to hold the startup / sync frame or the single slot frame, if the node transmits one, as configured by SUCC1.TXST, SUCC1.TXSY, and SUCC1.TSM. In addition, message buffer 1 may be used for sync frame transmission in case that sync frames or single-slot frames should have different payloads on the two channels. In this case bit MRC.SPLM has to be programmed to ’1’ and message buffers 0 and 1 have to be configured with the key slot ID and can be (re)configured in DEFAULT_CONFIG or CONFIG state only.

The second group consists of message buffers assigned to the static or to the dynamic segment. Message buffers belonging to this group may be reconfigured during run time from dynamic to static or vice versa depending on the state of MRC.SEC[1:0].

The message buffers belonging to the third group are concatenated to a single receive FIFO.

Message Buffer 0 |

|

Static Buffers |

|

|

Message Buffer 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

… |

|

Static + Dynamic |

FDB |

|

|

Buffers |

|

|

|

|

|

|

|

|

|

|

FIFO |

FFB |

|

Message Buffer N-1 |

|

|

|

|

|

|

|

|

LCB |

Message Buffer N |

|

|

||

|

|

|

|

|

Table 1: Assignment of message buffers

- 19/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

|

Address |

Symbol |

Name |

Page |

Reset |

Acc |

Block |

|

|

|

|

|

|

|

|

|

|

|

|

|

Customer Registers |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0000 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0004 |

|

see Customer CPU Interface Specification |

|

|

CIF |

||

|

|

|

|

|

||||

|

0x0008 |

|

|

|

||||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

0x000C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Special Registers |

|

|

|

|

|

|

0x0010- |

|

reserved (3) |

|

0000 0000 |

r |

|

|

|

0x0018 |

|

|

|

||||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

0x001C |

LCK |

Lock Register |

24 |

0000 0000 |

r/w |

GIF |

|

|

|

|

|

|

|

|

|

|

|

|

|

Interrupt Registers |

|

|

|

|

|

|

0x0020 |

EIR |

Error Interrupt Register |

25 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

0x0024 |

SIR |

Status Interrupt Register |

28 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

0x0028 |

EILS |

Error Interrupt Line Select |

31 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

0x002C |

SILS |

Status Interrupt Line Select |

32 |

0303 FFFF |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

0x0030 |

EIES |

Error Interrupt Enable Set |

33 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

0x0034 |

EIER |

Error Interrupt Enable Reset |

33 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

0x0038 |

SIES |

Status Interrupt Enable Set |

34 |

0000 0000 |

r/w |

INT |

|

|

|

|

|

|

|

|

|

|

|

0x003C |

SIER |

Status Interrupt Enable Reset |

34 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

0x0040 |

ILE |

Interrupt Line Enable |

35 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

0x0044 |

T0C |

Timer 0 Configuration |

36 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

0x0048 |

T1C |

Timer 1 Configuration |

37 |

0002 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

0x004C |

STPW1 |

Stop Watch Register 1 |

38 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

0x0050 |

STPW2 |

Stop Watch Register 2 |

39 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

0x0054 - |

|

reserved (11) |

|

0000 0000 |

r |

|

|

|

0x007C |

|

|

|

||||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

CC Control Registers |

|

|

|

|

|

|

0x0080 |

SUCC1 |

SUC Configuration Register 1 |

40 |

0C40 1080 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

0x0084 |

SUCC2 |

SUC Configuration Register 2 |

45 |

0100 0504 |

r/w |

SUC |

|

|

|

|

|

|

|

|

|

|

model.fm |

0x0088 |

SUCC3 |

SUC Configuration Register 3 |

45 |

0000 0011 |

r/w |

|

|

|

|

|

|

|

|

|

||

0x008C |

NEMC |

NEM Configuration Register |

46 |

0000 0000 |

r/w |

NEM |

||

|

||||||||

|

|

|

|

|

|

|

|

|

programmers |

0x0090 |

PRTC1 |

PRT Configuration Register 1 |

47 |

084C 0633 |

r/w |

PRT |

|

|

|

|

|

|

|

|||

|

0x0094 |

PRTC2 |

PRT Configuration Register 2 |

48 |

0F2D 0A0E |

r/w |

||

|

|

|||||||

|

|

|

|

|

|

|

|

|

manual |

0x0098 |

MHDC |

MHD Configuration Register |

49 |

0000 0000 |

r/w |

MHD |

|

|

|

|

|

|

|

|

||

0x009C |

|

reserved (1) |

|

0000 0000 |

r |

|

||

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

- 20/165 - |

15.12.2006 |

|

E-Ray |

|

User’s Manual |

|

|

Revision 1.2.5 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Address |

Symbol |

Name |

|

Page |

Reset |

|

Acc |

Block |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00A0 |

GTUC1 |

GTU Configuration Register 1 |

50 |

0000 0280 |

|

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00A4 |

GTUC2 |

GTU Configuration Register 2 |

50 |

0002 000A |

|

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00A8 |

GTUC3 |

GTU Configuration Register 3 |

51 |

0202 0000 |

|

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00AC |

GTUC4 |

GTU Configuration Register 4 |

52 |

0008 0007 |

|

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00B0 |

GTUC5 |

GTU Configuration Register 5 |

53 |

0E00 0000 |

|

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00B4 |

GTUC6 |

GTU Configuration Register 6 |

53 |

0002 0000 |

|

r/w |

GTU |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00B8 |

GTUC7 |

GTU Configuration Register 7 |

54 |

0002 0004 |

|

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00BC |

GTUC8 |

GTU Configuration Register 8 |

54 |

0000 0002 |

|

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00C0 |

GTUC9 |

GTU Configuration Register 9 |

55 |

0000 0101 |

|

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00C4 |

GTUC10 |

GTU Configuration Register 10 |

55 |

0002 0005 |

|

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00C8 |

GTUC11 |

GTU Configuration Register 11 |

56 |

0000 0000 |

|

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00CC - |

|

reserved (13) |

|

|

0000 0000 |

|

r |

|

|

|

|

0x00FC |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CC Status Registers |

|

|

|

|

|

|

|

|

|

0x0100 |

CCSV |

CC Status Vector |

57 |

0010 4000 |

|

r |

SUC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0104 |

CCEV |

CC Error Vector |

60 |

0000 0000 |

|

r |

|

||

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0108 - |

|

reserved (2) |

|

|

0000 0000 |

|

r |

|

|

|

|

0x010C |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0110 |

SCV |

Slot Counter Value |

61 |

0000 0000 |

|

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0114 |

MTCCV |

Macrotick and Cycle Counter Value |

61 |

0000 0000 |

|

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0118 |

RCV |

Rate Correction Value |

62 |

0000 0000 |

|

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x011C |

OCV |

Offset Correction Value |

62 |

0000 0000 |

|

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0120 |

SFS |

Sync Frame Status |

63 |

0000 0000 |

|

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0124 |

SWNIT |

Symbol Window and NIT Status |

64 |

0000 0000 |

|

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

GTU |

|

|

|

0x0128 |

ACS |

Aggregated Channel Status |

66 |

0000 0000 |

|

r/w |

|

||

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x012C |

|

reserved (1) |

|

|

0000 0000 |

|

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0130 - |

ESIDn |

Even Sync ID [1… |

15] |

68 |

0000 0000 |

|

r |

|

|

|

|

0x0168 |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x016C |

|

reserved (1) |

|

|

0000 0000 |

|

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0170 - |

OSIDn |

Odd Sync ID [1… |

15] |

69 |

0000 0000 |

|

r |

|

|

|

|

0x01A8 |

|

|

|

||||||

model.fm |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x01AC |

|

reserved (1) |

|

|

0000 0000 |

|

r |

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

programmers |

|

0x01B0 - |

NMVn |

Network Management Vector [1… 3] |

70 |

0000 0000 |

|

r |

NEM |

|

|

|

0x01BC - |

|

|

||||||||

|

|

0x01B8 |

|

|

|

|

|

|

|

|

|

manual |

|

0x02FC |

|

reserved (81) |

|

|

0000 0000 |

|

r |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Message Buffer Control Registers |

|

|

|

|

|

|

|

|

|

0x0300 |

MRC |

Message RAM Configuration |

71 |

0180 0000 |

|

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0304 |

FRF |

FIFO Rejection Filter |

73 |

0180 0000 |

|

r/w |

MHD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0308 |

FRFM |

FIFO Rejection Filter Mask |

74 |

0000 0000 |

|

r/w |

|

||

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x030C |

FCL |

FIFO Critical Level |

74 |

0000 0080 |

|

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- 21/165 - |

15.12.2006 |

|

E-Ray |

|

|

User’s Manual |

|

Revision 1.2.5 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Address |

Symbol |

|

Name |

Page |

Reset |

Acc |

Block |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Message Buffer Status Registers |

|

|

|

|

|

|

|

0x0310 |

MHDS |

|

Message Handler Status |

75 |

0000 0080 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0314 |

LDTS |

|

Last Dynamic Transmit Slot |

76 |

0000 0000 |

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0318 |

FSR |

|

FIFO Status Register |

77 |

0000 0000 |

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x031C |

MHDF |

|

Message Handler Constraints Flags |

78 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0320 |

TXRQ1 |

|

Transmission Request 1 |

80 |

0000 0000 |

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0324 |

TXRQ2 |

|

Transmission Request 2 |

80 |

0000 0000 |

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0328 |

TXRQ3 |

|

Transmission Request 3 |

80 |

0000 0000 |

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x032C |

TXRQ4 |

|

Transmission Request 4 |

80 |

0000 0000 |

r |

MHD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0330 |

NDAT1 |

|

New Data 1 |

81 |

0000 0000 |

r |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0334 |

NDAT2 |

|

New Data 2 |

81 |

0000 0000 |

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0338 |

NDAT3 |

|

New Data 3 |

81 |

0000 0000 |

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x033C |

NDAT4 |

|

New Data 4 |

81 |

0000 0000 |

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0340 |

MBSC1 |

|

Message Buffer Status Changed 1 |

82 |

0000 0000 |

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0344 |

MBSC2 |

|

Message Buffer Status Changed 2 |

82 |

0000 0000 |

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0348 |

MBSC3 |

|

Message Buffer Status Changed 3 |

82 |

0000 0000 |

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x034C |

MBSC4 |

|

Message Buffer Status Changed 4 |

82 |

0000 0000 |

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0350 - |

|

|

reserved (40) |

|

0000 0000 |

r |

|

|

|

|

0x03EC |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Identification Registers |

|

|

|

|

|

|

|

0x03F0 |

CREL |

|

Core Release Register |

83 |

[release info] |

r |

GIF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x03F4 |

ENDN |

|

Endian Register |

83 |

8765 4321 |

r |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

0x03F8 - |

|

|

reserved (2) |

|

0000 0000 |

r |

|

|

|

|

0x03FC |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Buffer |

|

|

|

|

|

|

|

0x0400 - |

WRDSn |

|

Write Data Section [1… 64] |

84 |

0000 0000 |

r/w |

|

|

|

|

0x04FC |

|

|

|

|

|

|

|

|

|

|

0x0500 |

WRHS1 |

|

Write Header Section 1 |

85 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0504 |

WRHS2 |

|

Write Header Section 2 |

86 |

0000 0000 |

r/w |

IBF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0508 |

WRHS3 |

|

Write Header Section 3 |

86 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

model.fm |

|

0x050C |

|

|

reserved (1) |

|

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0510 |

IBCM |

|

Input Buffer Command Mask |

87 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

programmers |

|

0x0514 |

IBCR |

|

Input Buffer Command Request |

88 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x05FC |

|

|

reserved (58) |

|

0000 0000 |

r |

|

|

|

|

|

0x0518 - |

|

|

|

|

|

|

|

|

manual |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Buffer |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0600 - |

RDDSn |

|

Read Data Section [1… 64] |

89 |

0000 0000 |

r |

|

|

|

|

0x06FC |

|

|

|

|

|

|

|

|

|

|

0x0700 |

RDHS1 |

|

Read Header Section 1 |

90 |

0000 0000 |

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0704 |

RDHS2 |

|

Read Header Section 2 |

91 |

0000 0000 |

r |

OBF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0708 |

RDHS3 |

|

Read Header Section 3 |

92 |

0000 0000 |

r |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

0x070C |

MBS |

|

Message Buffer Status |

93 |

0000 0000 |

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0710 |

OBCM |

|

Output Buffer Command Mask |

96 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0714 |

OBCR |

|

Output Buffer Command Request |

97 |

0000 0000 |

r/w |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x0718 - |

|

|

reserved (58) |

|

0000 0000 |

r |

|

|

|

|

0x07FC |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Table 2: E-Ray register map |

|

|

|

|

|

|

||

- 22/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

4.2 Customer Registers

The address space from 0x0000 to 0x000F is reserved for customer-specific registers. These registers, if implemented, are located in the Customer CPU Interface block. A description can be found in the specific Customer CPU Interface specification document.

manual_programmers_model.fm

- 23/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

4.3Special Registers

4.3.1Lock Register (LCK)

The Lock Register is write-only. Reading the register will return 0x0000 0000.

Bit |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

|

LCK |

R |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x001C |

W |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Reset |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Bit |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

W |

|

|

|

|

|

|

|

|

CLK7 |

CLK6 |

CLK5 |

CLK4 |

CLK3 |

CLK2 |

CLK1 |

CLK0 |

Reset |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

CLK[7:0] Configuration Lock Key

To leave CONFIG state by writing SUCC1.CMD[3:0] (commands READY, MONITOR_MODE, ATM, LOOP_BACK), the write operation has to be directly preceded by two write accesses to the Configuration Lock Key (unlock sequence). If the write sequence below is interrupted by other write accesses between the second write to the Configuration Lock Key and the write access to the SUCC1 register, the CC remains in CONFIG state and the sequence has to be repeated.

First write: |

LCK.CLK[7:0] |

= "1100 1110" |

(0xCE) |

Second write: LCK.CLK[7:0] |

= "0011 0001" |

(0x31) |

|

Third write: |

SUCC1.CMD[3:0] |

|

|

Note: In case that the Host uses 8/16-bit accesses to write CLK[7:0], the programmer has to ensure that no "dummy accesses" e.g. to the remaining register bytes / words are inserted by the compiler.

manual_programmers_model.fm

- 24/165 - |

15.12.2006 |

E-Ray |

User’s Manual |

Revision 1.2.5 |

manual_programmers_model.fm

4.4Interrupt Registers

4.4.1Error Interrupt Register (EIR)

The flags are set when the CC detects one of the listed error conditions. The flags remain set until the Host clears them. A flag is cleared by writing a ’1’ to the corresponding bit position. Writing a ’0’ has no effect on the flag. A hard reset will also clear the register.

Bit |

|

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

|

EIR |

R |

0 |

|

0 |

0 |

0 |

0 |

TABB |

LTVB |

EDB |

0 |

0 |

0 |

0 |

0 |

TABA |

LTVA |

EDA |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

0x0020 |

W |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Reset |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

Bit |

|

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |