ATMEL AT34C02N-10SI-2.7, AT34C02N-10SI-1.8, AT34C02N-10SI, AT34C02N-10SC-2.7, AT34C02N-10SC-1.8 Datasheet

...

Features

•

Permanent Software Write Protection for the First-Half of the Array

– Software Procedure to Verify Write Protect Status

•

Hardware Write Protection for the Entire Array

•

Low Voltage and S tandard Voltage Operation

– 5.0 (VCC = 4.5V to 5.5V)

– 2.7 (VCC = 2.7V to 5.5V)

– 1.8 (VCC = 1.8V to 5.5V)

•

Internally Organized 256 x 8

•

2-Wire Serial Interface

•

Schmitt Trigger, Filtered Inputs for Noise Suppression

•

Bidirectional Data Transfer Protocol

•

100 KHz (1.8V and 2.7V) and 400 KHz (5.0V) Compatibility

•

16-Byte Page Wri te Modes

•

Partial Page Writes Are Allowed

•

Self-Timed Write Cycle (10 ms max)

•

High Reliability

– Endurance: 1 Million Write Cycles

– Data Retention: 100 Years

– ESD Protection: >3,000V

•

Automotive Grade and Extended Temperature Devices Available

•

8-Pin PDIP, 8-Pin JEDEC SOIC and 8-Pin TSSOP Packages

Description

The AT34C02 provides 2048 bits of serial electrically erasable and programmable

read only memory ( EEPRO M ) or gan iz ed as 25 6 wo rds of 8 bi ts ea ch . The fi rst- hal f o f

the device incorporates a software write protection feature while hardware write protection for the entire array is available via an external pin as well. Once the software

write protection is enabled, by s end ing a special comm and t o the device, it ca nnot b e

reversed. The hardware write protection is controlled with the WP pin and can be used

to protect the entire array, whether or not the software write protection has been

enabled. This allows the user to protect none, first-half, or all of the array depending

on the applica tion . The device is opti mi zed for u se in ma ny i nd us tri al a nd c om mer cial

applications where low power and low voltage operations are essential. The AT34C02

is available in space sa ving 8-pin PDIP, 8-pi n JEDEC SOIC, and 8-pin TSSO P packages and is accessed via a 2-wire se rial interface. In addition, it is av ailable in 5.0V

(4.5V to 5.5V), 2.7V (2.7V to 5.5V), and 1.8V (1.8V to 5.5V) versions.

2-Wire Serial

EEPROM

with Permanent

Software Write

Protect

2K (256 x 8)

AT34C02

2-Wire Serial

Pin Configurations

Pin Name Function

A0 to A2 Address Inputs

SDA Serial Data

SCL Serial Clock Input

WP Write Protect

8-Pin TSSOP

A0

A1

A2

GND

1

2

3

4

8

7

6

5

VCC

WP

SCL

SDA

A0

A1

A2

GND

GND

A0

A1

A2

8-Pin SOIC

1

2

3

4

8-Pin PDIP

1

2

3

4

EEPROM with

VCC

8

WP

7

SCL

6

SDA

5

Permanent

Software Write

Protec

8

VCC

7

WP

6

SCL

5

SDA

Rev. 0958D–07/98

1

Absolute Maximum Ratings*

Operating Temperature .................................. -55°C to +125 °C

Storage Temperature.....................................-65°C to +150°C

Voltage on Any Pin

with Respect to Ground.....................................-1.0V to +7.0V

Maximum Operating Voltage........................................... 6.25V

DC Output Current........................................................5.0 mA

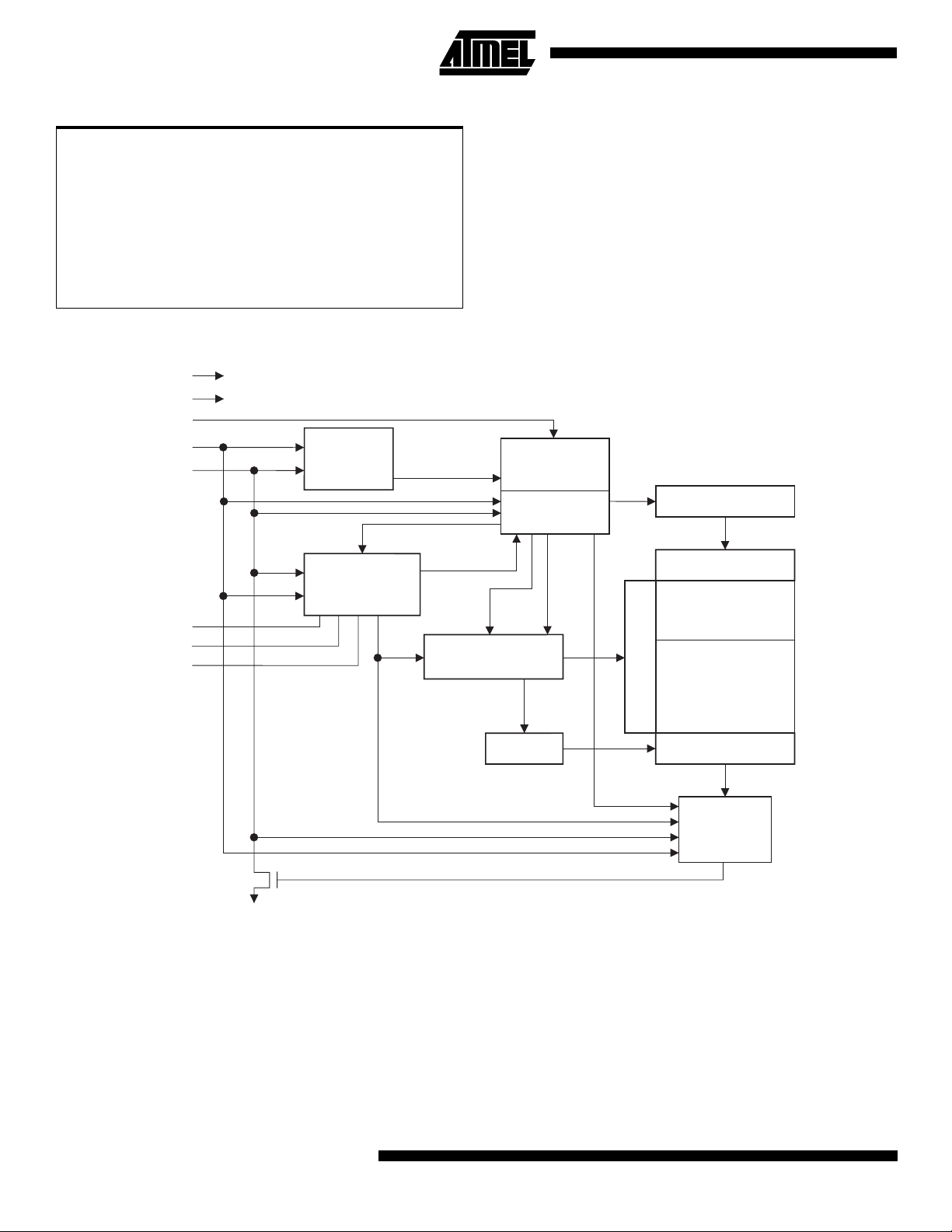

Block Diagram

V

CC

GND

WP

SCL

SDA

A

2

A

1

A

0

START

STOP

LOGIC

LOAD

DEVICE

ADDRESS

COMPARATOR

R/W

*NOTICE: Stresses beyond those listed under “Absolute

SERIAL

CONTROL

WRITE PROTECT

CIRCUITRY

COMP

DATA WORD

ADDR/COUNTER

LOGIC

INCLOAD

Maximum Ratings” may cause permanent damage to the de vic e. T his is a stres s rat ing onl y and

functional oper a tion of the device at these o r any

other conditions beyond those indicated in the

operational sections of this specification is not

implied. Exposure to absolute maximu m rating

conditions f or ex tended periods ma y aff ect dev ice

reliability.

EN

H.V. PUMP/TIMING

DATA RECOVERY

SOFTWARE WRITE

PROTECTED AREA

(00H - 7FH)

X DEC

2

E

PROM

D

IN

D

OUT

Pin Description

SERIAL CLOCK (SCL):

edge clock data into each EEPROM device and negative

edge clock data out of each device.

SERIAL DATA (SDA):

serial data transfer. This pin is open-drain driven and may

be wire-ORed with any number of other open-drain or open

collector devices.

2

The SCL input is used to positive

The SDA pin is bidirectional for

AT34C02

Y DEC

DEVICE/PAGE ADDRESSES (A2 , A1, A0):

SERIAL MUX

D

/ACK

OUT

LOGIC

The A2, A1

and A0 pins are device address inputs that are hard wired

for the AT34C02. As many as eight 2K devices may be

addressed on a single bus system (device addressin g is

discussed in detail under the Device Addressing section).

WRITE PROTECT (WP):

The AT34C02 has a Write Protect pin that provides hardware data protection. The Write

Protect pin allows normal read/write operations when con-

AT34C02

nected to ground (GND) or when left floating. When the

Write Protect pin is connected to V

, the write protection

CC

feature is enabled for the entire array. The write protection

modes are shown in the following table.

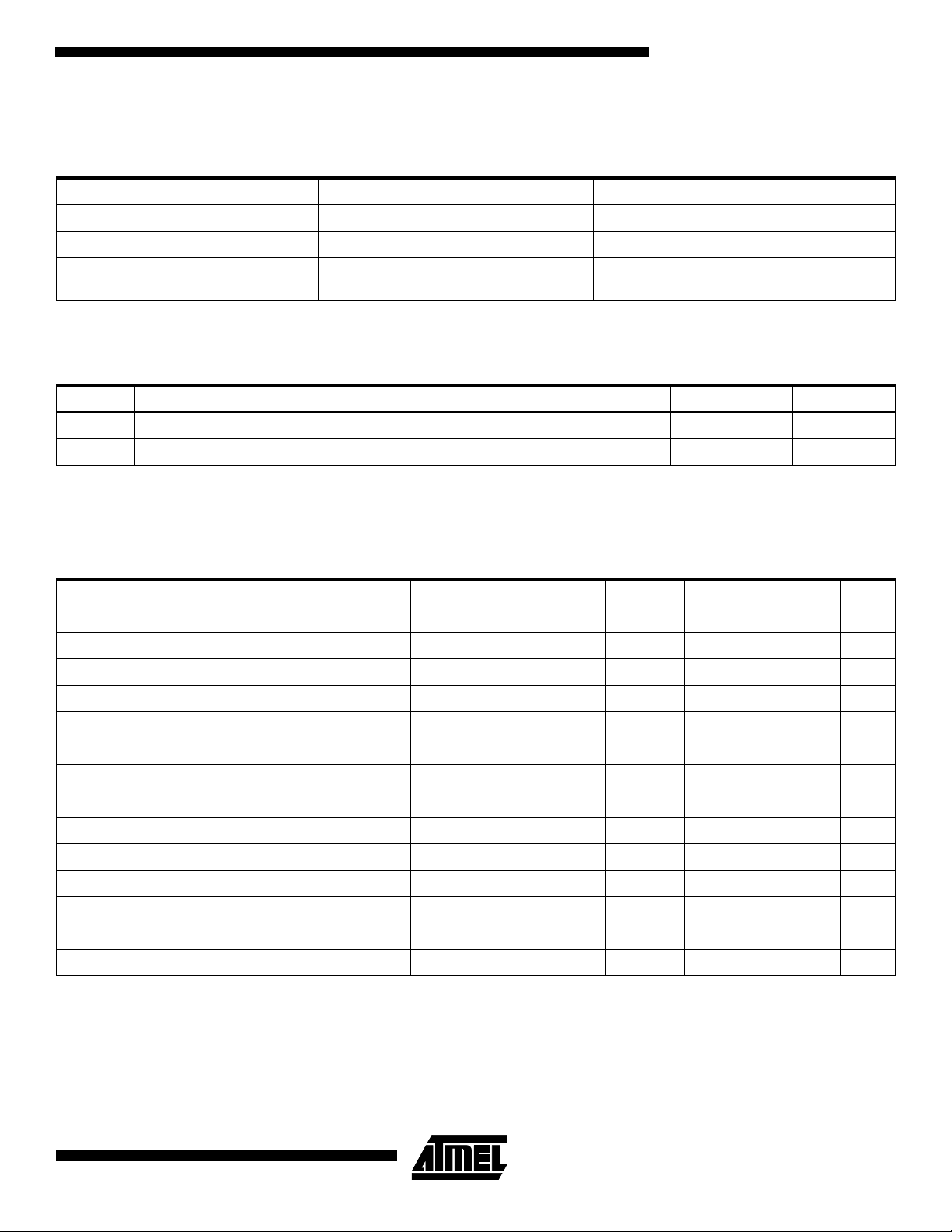

AT34C02 Write Protection Modes

WP Pin Status Write Protect Register Part of the Array Write Protected

V

CC

— Full Array (2K)

GND or Floating Not Programmed Normal Read/Write

GND or Floating Programmed

Pin Capacitance

(1)

First-Half of Array

(1K: 00H - 7FH)

Applicable over recommended operating range from TA = 25°C, f = 1.0 MHz, VCC = +1.8V

Symbol Test Condition Max Units Conditions

C

I/O

C

IN

Input/Output Capacitance (SDA) 8 pF V

Input Capacitance (A0, A1, A2, SCL) 6 pF VIN = 0V

Note: 1. This parameter is characterized and is not 100% tested

I/O

= 0V

DC Characteristics

Applicable over recommended operating range from: TAI = -40°C to +85°C, V

= +1.8V to +5.5V (unless otherwise noted).

V

CC

Symbol Parameter Test Condition Min Typ Max Units

V

CC1

V

CC2

V

CC3

I

CC

I

CC

I

SB1

I

SB2

I

SB3

I

LI

I

LO

V

IL

V

IH

V

OL2

V

OL1

Note: 1. VIL min and VIH max are reference only and are not tested.

Supply Voltage 1.8 5.5 V

Supply Voltage 2.7 5.5 V

Supply Voltage 4.5 5.5 V

Supply Current VCC = 5.0V READ at 100 KHz 0.4 1.0 mA

Supply Current VCC = 5.0V WRITE at 100 KHz 2.0 3.0 mA

Standby Current VCC = 1.8V VIN = VCC or V

Standby Current VCC = 2.7V VIN = VCC or V

Standby Current VCC = 5.0V VIN = VCC or V

Input Leakage Current VIN = VCC or V

Output Leakage Current V

Input Low Level

Input High Level

(1)

(1)

OUT

= V

CC

or V

SS

SS

SS

SS

SS

Output Low Level VCC = 3.0V IOL = 2.1 mA 0.4 V

Output Low Level VCC = 1.8V IOL = 0.15 mA 0.2 V

= +1.8V to +5.5V, TAC = 0°C to +70°C,

CC

0.6 3.0

1.6 4.0

8.0 18.0

0.10 3.0

0.05 3.0

-0.6 VCC x 0.3 V

VCC x 0.7 VCC + 0.5 V

A

µ

A

µ

A

µ

A

µ

A

µ

3

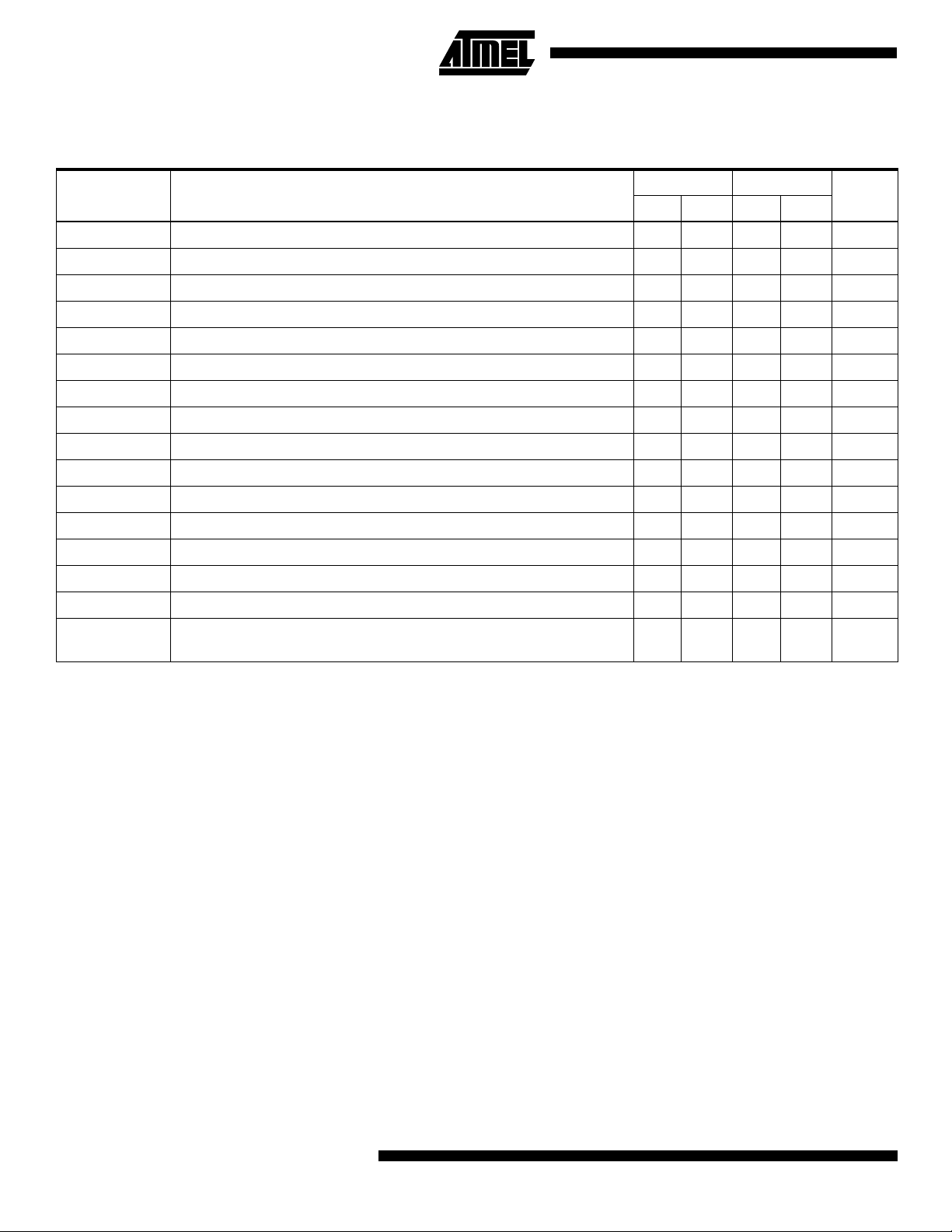

AC Characteristics

Applicable over recommended operating range from TA = -40°C to +85°C, VCC = +1.8V to +5.5V,

= 1 TTL Gate and 100 pF (unless otherwise noted).

C

L

1.8V, 2.7V 5.0V

Symbol Parameter

f

SCL

t

LOW

t

HIGH

t

I

t

AA

t

BUF

t

HD.STA

t

SU.STA

t

HD.DAT

t

SU.DAT

t

R

t

F

t

SU.STO

t

DH

t

WR

Endurance

Note: 1. This parameter is characterized and is not 100% tested.

(1)

Clock Frequency, SCL 100 400 kHz

Clock Pulse Width Low 4.7 1.2

Clock Pulse Width High 4.0 0.6

Noise Suppression Time

Clock Low to Data Out Valid 0.1 4.5 0.1 0.9

Time the bus must be free before a new transmission can start

Start Hold Time 4.0 0.6

Start Set-up Time 4.7 0.6

Data In Hold Time 0 0

Data In Set-up Time 200 100 ns

Inputs Rise Time

Inputs Fall Time

Stop Set-up Time 4.7 0.6

Data Out Hold Time 100 50 ns

Write Cycle Time 10 10 ms

5.0V, 25°C, Page Mode 1M 1M

(1)

(1)

(1)

UnitsMinMaxMinMax

µ

s

µ

s

100 50 ns

µ

s

(1)

4.7 1.2

1.0 0.3

300 300 ns

µ

s

µ

s

µ

s

µ

s

µ

s

µ

s

Write

Cycles

Memory Organization

AT34C02, 2K Serial EEPROM:

nized with 256 pages of 1 byte each. Random word

addressing requires a 8-bit data word address.

The 2K is internally orga-

Device Operation

CLOCK and DATA TRANSITIONS:

mally pulled high with an external de vice . Data on th e SDA

pin may chan ge only dur ing SC L lo w ti me p eri ods (re fer to

Data Validity timing diagram). Data changes during SCL

high periods will indicate a start or stop condition as defined

below.

START CONDITION:

A high-to-low transition of SDA with

SCL high is a start condition which must precede any other

command (refer to Start and Stop Definition timing diagram).

STOP CONDITION:

A low-to-high transition of SDA with

SCL high is a stop condition. After a read sequence, the

4

AT34C02

The SDA pin is nor-

stop command will pla ce the EEP ROM in a stan dby power

mode (refer to Start and Stop Definition timing diagram).

ACKNOWLEDGE:

All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words.

The EEPROM sends a z ero to acknowledge that it has

received each word. This happens during the ninth clock

cycle.

STANDBY MODE:

The AT34C02 features a low power

standby mode which is enabled: (a) up on power-up or (b)

after the receipt of th e STO P bit and th e co mpleti on of any

internal operations.

MEMORY RESET:

After an interruption in protocol, power

loss or system reset, any 2-wire part can be reset by following these steps:

(a) Clock up to 9 cycles, (b) look for SDA high in each cycle

while SCL is high and then (c) create a start condition as

SDA is high.

Loading...

Loading...