ATMEL AT24C21-10PI-2.5, AT24C21-10PC-2.5, AT24C21-10SI-2.5, AT24C21-10SC-2.5 Datasheet

Features

•2-Wire Serial Interface

•Schmitt Trigger, Filtered Inputs For Noise Suppression

•DDC1™/ DDC2™ Interface Compliant for Monitor Identification

•Low Voltage Operation

–2.5 (V CC = 2.5V to 5.5V)

•Internally Organized 128 x 8

•100 kHz (2.5V) Compatibility

•8-Byte Page Write Mode

•Write Protection Available

•Self-timed Write Cycle (10 ms max)

•High Reliability

–Endurance: 1 Million Write Cycles

–Data Retention: 100 Years

–ESD Protection: >3000V

•8-Pin PDIP and JEDEC SOIC Packages

Description

The AT24C21 provides 1024 bits of serial electrically erasable and programmable read only memory (EEPROM) organized as 128 words of 8 bits each. The device is optimized for use in applications requiring data storage and serial transmission of configuration and control information. The AT24C21 features two modes of operation: Transmit-Only Mode and Bidirectional Mode. Upon power-up, the AT24C21 will be in the Transmit-Only Mode, sending a serial-bit stream of the entire memory contents, clocked via the VCLK pin. The Bidirectional Mode is selected by a valid high-to-low transition on the SCL pin and offers byte selectable read/write capability of the entire memory array. The AT24C21 is available in space saving 8-pin PDIP and 8-pin SOIC packages.

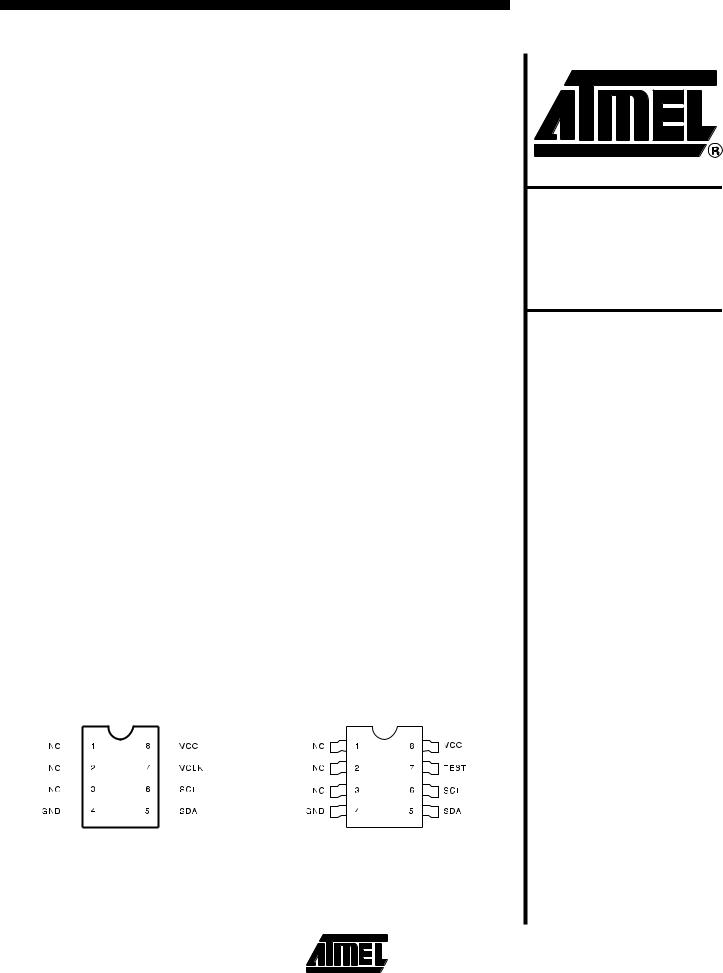

Pin Configurations

Pin Name |

Function |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

NC |

No Connect |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

SDA |

Serial Data |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

SCL |

Serial Clock Input |

|

|

|

|

|

||||

|

|

(Bidirectional Mode) |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

VCLK |

Serial Clock Input |

|

|

|

|

|

||||

|

|

(Transmit-Only Mode) |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|||

|

|

|

8-Pin PDIP |

8-Pin SOIC |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2-Wire Serial |

EEPROM |

1K (128 x 8) |

AT24C21 |

Rev. 0405E–07/98 |

1 |

Absolute Maximum Ratings*

Operating Temperature |

° |

° |

*NOTICE: Stresses beyond those listed under “Absolute |

-55 C to +125 C |

Maximum Ratings” may cause permanent dam- |

||

|

|

|

|

Storage Temperature .................................... |

-65°C to +150°C |

age to the device. This is a stress rating only and |

|

|

|

|

functional operation of the device at these or any |

Voltage on Any Pin |

|

|

other conditions beyond those indicated in the |

with Respect to Ground ..................................... |

-1.0V to +7.0V |

operational sections of this specification is not |

|

Maximum Operating Voltage |

|

6.25V |

implied. Exposure to absolute maximum rating |

|

conditions for extended periods may affect device |

||

DC Output Current |

|

5.0 mA |

reliability. |

|

|

||

|

|

|

|

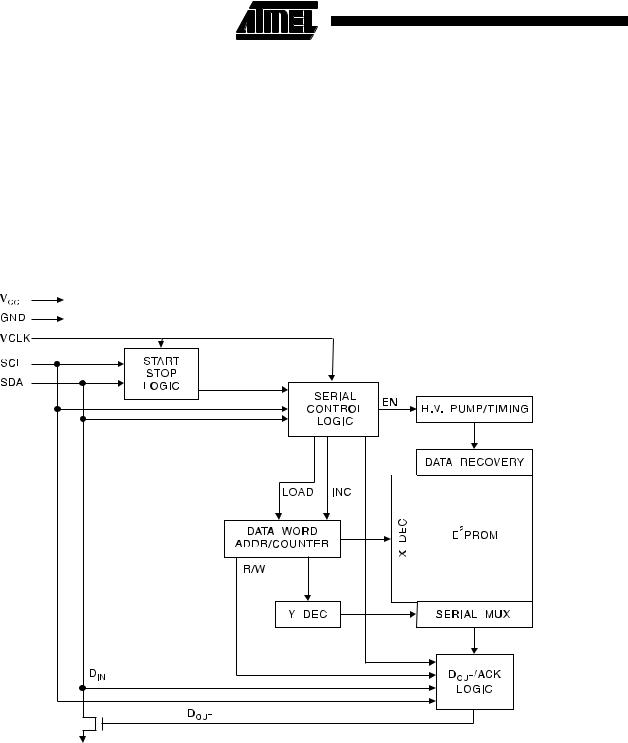

Block Diagram

Pin Description

SERIAL CLOCK (SCL): The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.

SERIAL DATA (SDA): The SDA pin is bidirectional for serial data transfer. This pin is open-drain driven and may be wire-ORed with any number of other open drain or open collector devices.

SERIAL CLOCK (VCLK): Upon power-up, the device is in the Transmit-Only mode and will transmit the entire memory contents via the SDA pin with positive signals on the VCLK pin.

Memory Organization

AT24C21, 1K SERIAL EEPROM: Internally organized with 128 pages of one byte each. The 1K requires a 7-bit data word address for random word addressing.

2 |

AT24C21 |

|

|

||

|

AT24C21

DC Characteristics

Applicable over recommended operating range from: TAI = -40°C to +85°C, TAC = 0°C to +70°C, VCC = +2.5V to +5.5V (unless otherwise noted).

Symbol |

|

Parameter |

Test Condition |

|

Min |

Typ |

|

Max |

Units |

|||

|

|

|

|

|

|

|

|

|

|

|

||

VCC |

|

Supply Voltage |

|

|

2.5 |

|

|

|

5.5 |

V |

||

ICC |

|

Supply Current VCC = 5.0V |

READ at 100 KHz |

|

|

|

0.4 |

|

1.0 |

mA |

||

ICC |

|

Supply Current VCC = 5.0V |

WRITE at 100 KHz |

|

|

|

2.0 |

|

3.0 |

mA |

||

ISB |

|

Standby Current .......VCC = 2.5V |

VIN = VCC or VSS |

|

|

|

3.0 |

|

4.0 |

mA |

||

|

|

|

.......VCC = 5.0V |

VIN = VCC or VSS |

|

|

|

12.0 |

|

30.0 |

mA |

|

ILI |

|

Input Leakage Current |

VIN = VCC or VSS |

|

|

|

0.10 |

|

1.0 |

mA |

||

ILO |

|

Output Leakage Current |

VOUT = VCC or VSS |

|

|

|

0.05 |

|

1.0 |

mA |

||

V |

IL |

|

Input Low Level(1) SCL, SDA Pin |

|

|

-0.6 |

|

V |

CC |

´ 0.3 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Input Low Level VCLK Pin |

VCC ³ 2.7V |

|

|

|

|

|

0.8 |

V |

|

|

|

|

|

VCC < 2.7V |

|

|

|

|

0.2 ´ VCC |

V |

||

V |

IH |

|

Input High Level(1) SCL, SDA Pin |

|

V |

´ |

0.7 |

|

V |

CC |

+ 0.5 |

V |

|

|

|

|

|

CC |

|

|

|

|

|

||

|

|

|

Input High Level VCLK Pin |

|

|

2.0 |

|

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

||

VOL |

|

Output Low Level VCC = 3.0V |

IOL = 2.1 mA |

|

|

|

|

|

0.40 |

V |

||

Note: 1. |

VIL min and VIH max are for reference only and not tested. |

|

|

|

|

|

|

|

|

|||

Pin Capacitance(1)

Applicable over recommended operating range from TA = 25°C, f = 1.0 MHz, VCC = +1.8V.

Symbol |

|

Test Condition |

Max |

Units |

Conditions |

|

|

|

|

|

|

CI/O |

|

Input/Output Capacitance (SDA) |

8 |

pF |

VI/O = 0V |

CIN |

|

Input Capacitance (A0, A1, A2, SCL, VCLK) |

6 |

pF |

VIN = 0V |

Note: 1. |

This parameter is characterized and is not 100% tested. |

|

|

|

|

Transmit-Only Mode

Symbol |

Parameter |

|

2.5-volt |

Units |

|

|

|

|

|

|

|

|

|

Min |

|

Max |

|

|

|

|

|

|

|

TVAA |

Output valid from VCLK |

|

|

500 |

ns |

TVHIGH |

VCLK high-time |

4.0 |

|

|

ms |

TVLOW |

VCLK low-time |

4.7 |

|

|

ms |

TVHZ |

Mode transition time |

|

|

500 |

ns |

TVPU |

Transmit-Only power-up time |

0 |

|

|

ns |

3

AC Characteristics

Applicable over recommended operating range from TA = -40°C to +85°C, VCC = +2.5V to +5.5V CL = 1 TTL Gate and 100 pF (unless otherwise noted).

|

|

|

2.5-volt |

|

|

|

|

|

|

|

|

Symbol |

Parameter |

Min |

|

Max |

Units |

|

|

|

|

|

|

fSCL |

Clock Frequency, SCL |

0 |

|

100 |

KHz |

tLOW |

Clock Pulse Width Low |

4.7 |

|

|

μs |

tHIGH |

Clock Pulse Width High |

4.0 |

|

|

μs |

tI |

Noise Suppression Time(1) |

|

|

NA |

ns |

|

(SDA and SCL pins) |

|

|

|

|

|

|

|

|

|

|

tAA |

Clock Low to Data Out Valid |

0.1 |

|

3.5 |

μs |

tBUF |

Time the bus must be free before a new |

4.7 |

|

|

μs |

|

transmission can start |

|

|

|

|

|

|

|

|

|

|

tHD.STA |

Start Hold Time |

4.0 |

|

|

μs |

tSU.STA |

Start Set-up Time |

4.7 |

|

|

μs |

tHD.DAT |

Data In Hold Time |

0 |

|

|

μs |

tSU.DAT |

Data In Set-up Time |

250 |

|

|

ns |

tR |

Inputs Rise Time(1) |

|

|

1.0 |

μs |

tF |

Inputs Fall Time(1) |

|

|

300 |

ns |

tSU.STO |

Stop Set-up Time |

4.0 |

|

|

μs |

tDH |

Data Out Hold Time |

100 |

|

|

ns |

tWR |

Write Cycle Time |

|

|

10 |

ms |

Endurance(1) |

5.0V, 25°C, Page Mode |

1M |

|

|

Write Cycles |

Note: 1. This parameter is characterized and is not 100% tested.

4 |

AT24C21 |

|

|

||

|

Loading...

Loading...