ATMEL TS80C51RA2, TS80C51RD2, TS83C51RB2, TS83C51RC2, TS83C51RD2 User Manual

...

TS80C51RA2

TS80C51RA2/RD2

TS83C51RB2/RC2/RD2

TS87C51RB2/RC2/RD2

High Performance 8-bit Microcontrollers

1. Description

Atmel Wireless & Microcontrollers TS80C51Rx2 is high performance CMOS ROM, OTP, EPROM and ROMless versions of the 80C51 CMOS single chip 8-bit microcontroller.

The TS80C51Rx2 retains all features of the 80C51 with extended ROM/EPROM capacity (16/32/64 Kbytes), 256 bytes of internal RAM, a 7-source , 4-level interrupt system, an on-chip oscilator and three timer/counters.

In addition, the TS80C51Rx2 has a Programmable Counter Array, an XRAM of 256 or 768 bytes, a Hardware Watchdog Timer, a more versatile serial channel that facilitates multiprocessor communication (EUART) and a X2 speed improvement mechanism.

The fully static design of the TS80C51Rx2 allows to reduce system power consumption by bringing the clock frequency down to any value, even DC, without loss of data.

The TS80C51Rx2 has 2 software-selectable modes of reduced activity for further reduction in power consumption. In the idle mode the CPU is frozen while the timers, the serial port and the interrupt system are still operating. In the power-down mode the RAM is saved and all other functions are inoperative.

2. Features

∙80C52 Compatible

∙8051 pin and instruction compatible

∙Four 8-bit I/O ports

∙Three 16-bit timer/counters

∙256 bytes scratchpad RAM

∙High-Speed Architecture

∙40 MHz @ 5V, 30MHz @ 3V

∙X2 Speed Improvement capability (6 clocks/ machine cycle)

30 MHz @ 5V, 20 MHz @ 3V (Equivalent to 60 MHz @ 5V, 40 MHz @ 3V)

∙Dual Data Pointer

∙On-chip ROM/EPROM (16K-bytes, 32K-bytes, 64Kbytes)

∙On-chip eXpanded RAM (XRAM) (256 or 768 bytes)

∙Programmable Clock Out and Up/Down Timer/ Counter 2

∙Programmable Counter Array with

∙High Speed Output,

∙Compare / Capture,

∙Pulse Width Modulator,

∙Watchdog Timer Capabilities

∙Hardware Watchdog Timer (One-time enabled with Reset-Out)

∙2 extra 8-bit I/O ports available on RD2 with high pin count packages

∙Asynchronous port reset

∙Interrupt Structure with

∙7 Interrupt sources,

∙4 level priority interrupt system

∙Full duplex Enhanced UART

∙Framing error detection

∙Automatic address recognition

∙Low EMI (inhibit ALE)

∙Power Control modes

∙Idle mode

∙Power-down mode

∙Power-off Flag

∙Once mode (On-chip Emulation)

∙Power supply: 4.5-5V, 2.7-5.5V

∙Temperature ranges: Commercial (0 to 70oC) and Industrial (-40 to 85oC)

∙Packages: PDIL40, PLCC44, VQFP44 1.4, CQPJ44 (window), CDIL40 (window), PLCC68, VQFP64 1.4, JLCC68 (window)

Rev. C - 06 March, 2001 |

1 |

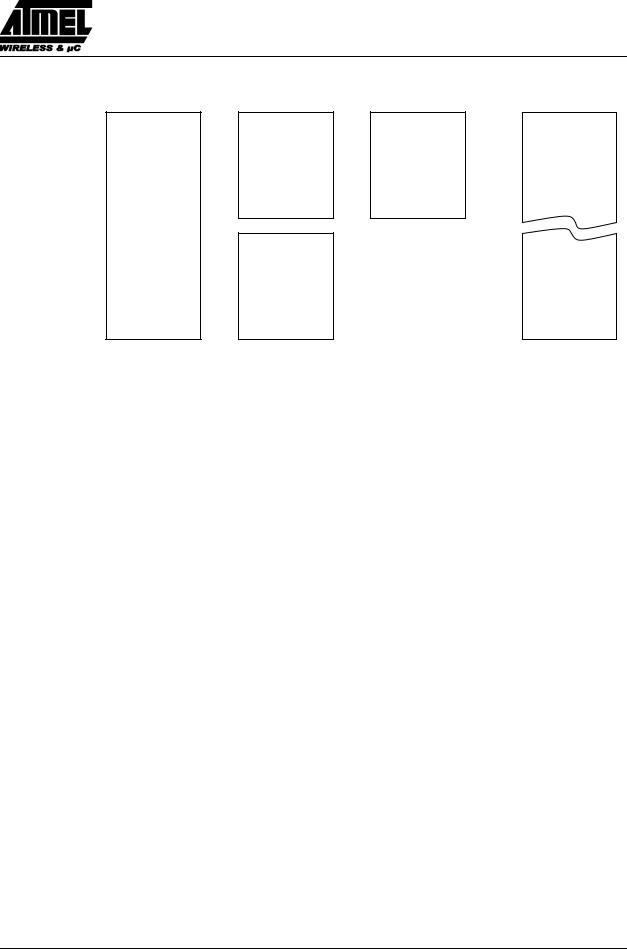

TS80C51RA2/RD2

TS83C51RB2/RC2/RD2

TS87C51RB2/RC2/RD2

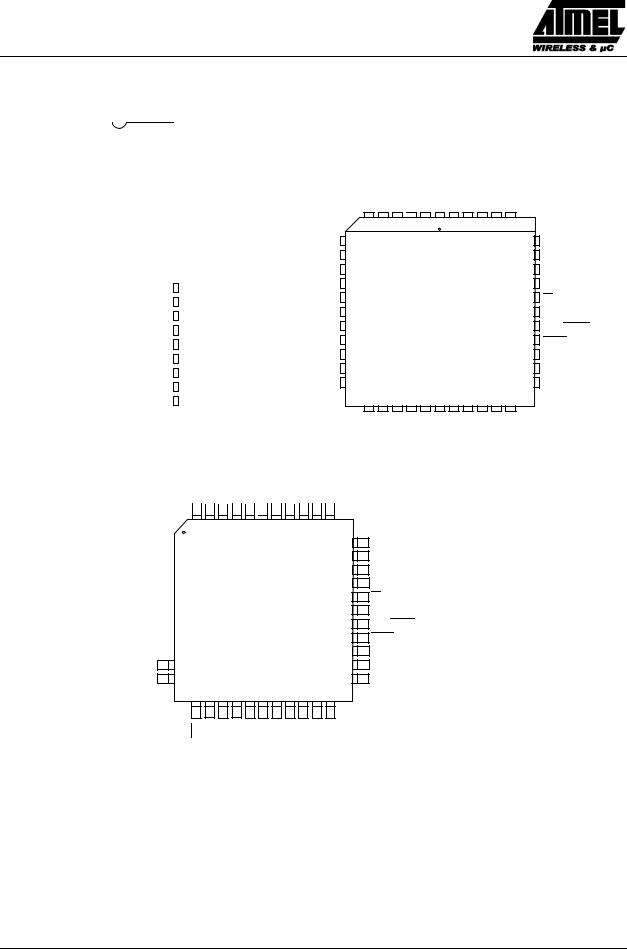

PDIL40 |

|

|

|

|

|

|

PLCC44 |

ROM (bytes) |

EPROM (bytes) |

XRAM (bytes) |

TOTAL RAM |

I/O |

|

(bytes) |

||||||

|

|

|

|

|

||

VQFP44 1.4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

TS80C51RA2 |

0 |

0 |

256 |

512 |

32 |

|

TS80C51RD2 |

0 |

0 |

768 |

1024 |

32 |

|

|

|

|

|

|

|

|

TS83C51RB2 |

16k |

0 |

256 |

512 |

32 |

|

TS83C51RC2 |

32k |

0 |

256 |

512 |

32 |

|

TS83C51RD2 |

64k |

0 |

768 |

1024 |

32 |

|

|

|

|

|

|

|

|

TS87C51RB2 |

0 |

16k |

256 |

512 |

32 |

|

TS87C51RC2 |

0 |

32k |

256 |

512 |

32 |

|

TS87C51RD2 |

0 |

64k |

768 |

1024 |

32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PLCC68 |

ROM (bytes) |

EPROM (bytes) |

XRAM (bytes) |

TOTAL RAM |

I/O |

|

|

||||||

VQFP64 1.4 |

(bytes) |

|||||

|

|

|

|

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

TS80C51RD2 |

0 |

0 |

768 |

1024 |

48 |

|

|

|

|

|

|

|

|

TS83C51RD2 |

64k |

0 |

768 |

1024 |

48 |

|

|

|

|

|

|

|

|

TS87C51RD2 |

0 |

64k |

768 |

1024 |

48 |

|

|

|

|

|

|

|

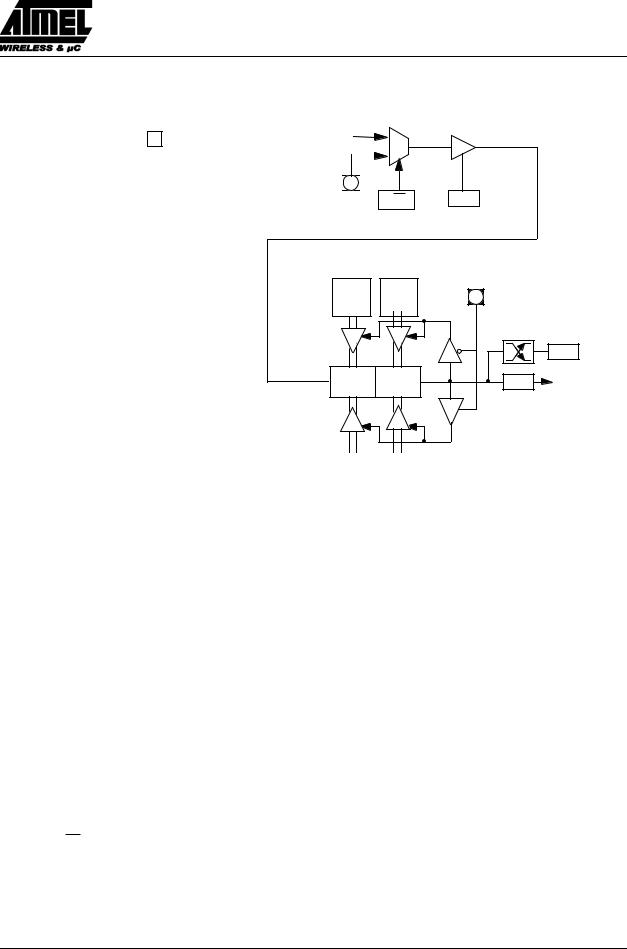

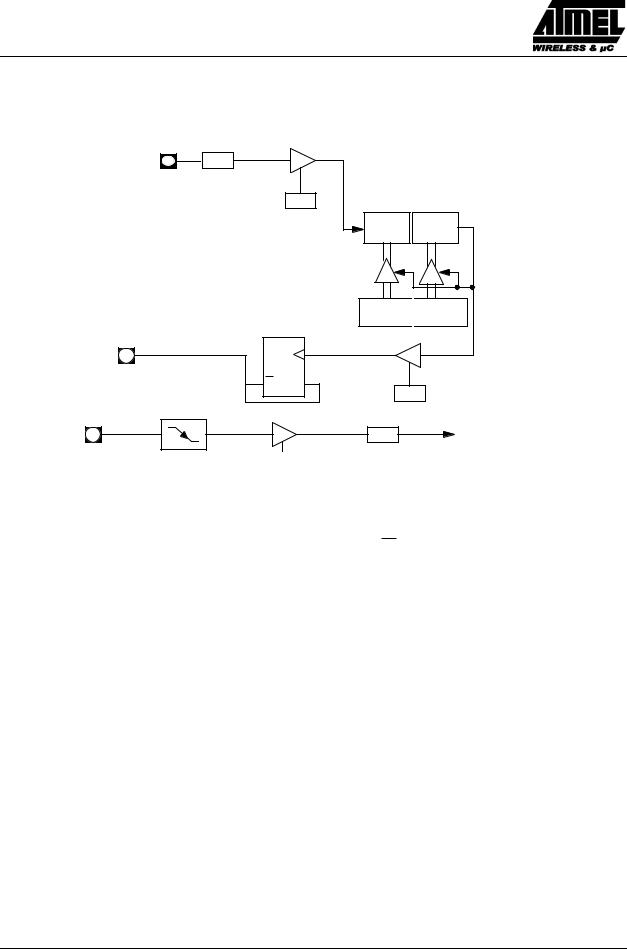

3. Block Diagram

|

|

|

|

|

|

|

|

|

RxD |

TxD |

|

|

|

Vcc Vss |

|

|

|

ECI |

PCA |

|

T2EX |

T2 |

|||||||||||

|

|

|

|

|

|

|

(3) |

|

(3) |

|

|

|

|

|

|

|

|

(1) |

|

|

|

(1) |

|

(1) |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(1) |

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

XTAL1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RAM |

|

|

|

ROM |

|

XRAM |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

XTAL2 |

|

|

|

|

|

|

|

EUART |

|

|

/EPROM |

|

|

|

|

PCA |

|

|

|

Timer2 |

|

||||||||||||

|

|

|

|

|

|

256x8 |

|

|

|

256/768x8 |

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0/16/32/64Kx8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ALE/ PROG |

C51 |

|

|

|

|

PSEN |

CORE |

IB-bus |

CPU |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EA/VPP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

(3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

Timer 0 |

|

|

INT |

|

|

|

|

|

Parallel I/O Ports & Ext. Bus |

|

|

|

|

Watch |

|

||||||||||||||||||||||||

|

|

|

RD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

Timer 1 |

|

|

Ctrl |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Dog |

|

|||||||||||||||

|

|

|

|

|

|

|

(3) |

|

|

|

|

|

|

|

|

|

|

Port 0 |

Port 1 |

Port 2 |

Port 3 |

Port 4 |

Port 5 |

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

WR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(2) |

|

(2) |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(3) |

|

(3) |

|

|

(3) |

|

(3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1 |

P2 |

|

P3 |

P4 |

|

P5 |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

RESET |

|

T0 |

|

|

T1 |

|

INT0 |

|

INT1 |

|

P0 |

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(1): Alternate function of Port 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(2): Only available on high pin count packages |

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(3): Alternate function of Port 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

2 |

Rev. C - 06 March, 2001 |

TS80C51RA2/RD2

TS83C51RB2/RC2/RD2

TS87C51RB2/RC2/RD2

4. SFR Mapping

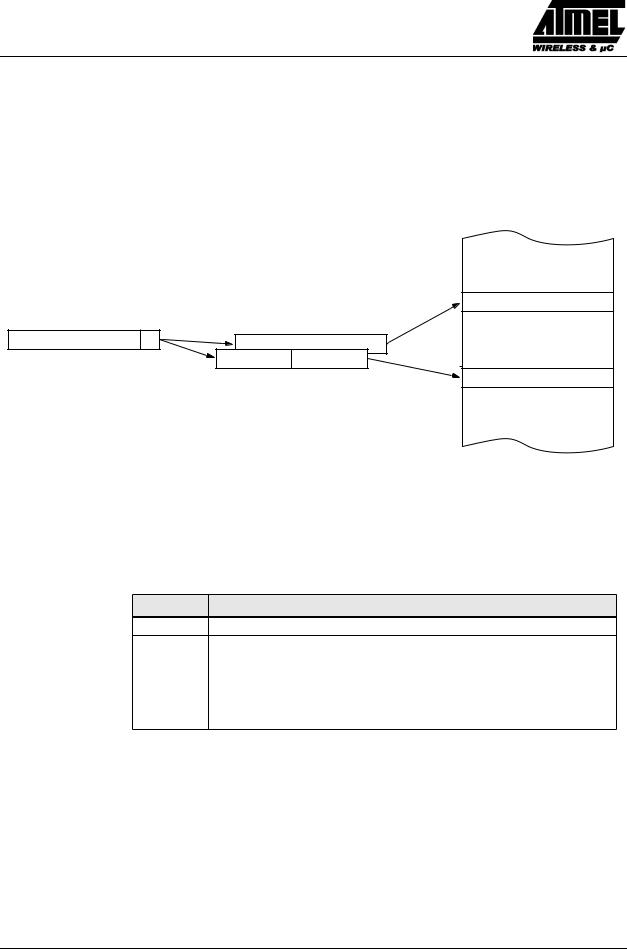

The Special Function Registers (SFRs) of the TS80C51Rx2 fall into the following categories:

∙C51 core registers: ACC, B, DPH, DPL, PSW, SP, AUXR1

∙I/O port registers: P0, P1, P2, P3, P4, P5

∙Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

∙Serial I/O port registers: SADDR, SADEN, SBUF, SCON

∙Power and clock control registers: PCON

∙HDW Watchdog Timer Reset: WDTRST, WDTPRG

∙PCA registers: CL, CH, CCAPiL, CCAPiH, CCON, CMOD, CCAPMi

∙Interrupt system registers: IE, IP, IPH

∙Others: AUXR, CKCON

Table 1. All SFRs with their address and their reset value

F8h

F0h

E8h

E0h

D8h

D0h

C8h

C0h

B8h

B0h

A8h

A0h

98h

90h

88h

80h

Bit |

|

|

Non Bit addressable |

|

|

|

|||

addressable |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

0/8 |

1/9 |

2/A |

3/B |

4/C |

5/D |

6/E |

7/F |

|

|

|

|

|

|

|

|

|

|

|

|

|

CH |

CCAP0H |

CCAP1H |

CCAPL2H |

CCAPL3H |

CCAPL4H |

|

FFh |

|

|

0000 0000 |

XXXX XXXX |

XXXX XXXX |

XXXX XXXX |

XXXX XXXX |

XXXX XXXX |

|

||

|

|

|

|||||||

B |

|

|

|

|

|

|

|

F7h |

|

0000 0000 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||

P5 bit |

CL |

CCAP0L |

CCAP1L |

CCAPL2L |

CCAPL3L |

CCAPL4L |

|

EFh |

|

addressable |

|

||||||||

0000 0000 |

XXXX XXXX |

XXXX XXXX |

XXXX XXXX |

XXXX XXXX |

XXXX XXXX |

|

|

||

1111 1111 |

|

|

|||||||

|

|

|

|

|

|

|

|

||

ACC |

|

|

|

|

|

|

|

E7h |

|

0000 0000 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||

CCON |

CMOD |

CCAPM0 |

CCAPM1 |

CCAPM2 |

CCAPM3 |

CCAPM4 |

|

DFh |

|

00X0 0000 |

00XX X000 |

X000 0000 |

X000 0000 |

X000 0000 |

X000 0000 |

X000 0000 |

|

||

|

|

||||||||

PSW |

|

|

|

|

|

|

|

D7h |

|

0000 0000 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||

T2CON |

T2MOD |

RCAP2L |

RCAP2H |

TL2 |

TH2 |

|

|

CFh |

|

0000 0000 |

XXXX XX00 |

0000 0000 |

0000 0000 |

0000 0000 |

0000 0000 |

|

|

||

|

|

|

|||||||

P4 bit |

|

|

|

|

|

|

P5 byte |

C7h |

|

addressable |

|

|

|

|

|

|

addressable |

||

|

|

|

|

|

|

|

|||

1111 1111 |

|

|

|

|

|

|

1111 1111 |

|

|

IP |

SADEN |

|

|

|

|

|

|

BFh |

|

X000 000 |

0000 0000 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|||

P3 |

|

|

|

|

|

|

IPH |

B7h |

|

1111 1111 |

|

|

|

|

|

|

X000 0000 |

||

|

|

|

|

|

|

|

|||

IE |

SADDR |

|

|

|

|

|

|

AFh |

|

0000 0000 |

0000 0000 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|||

P2 |

|

AUXR1 |

|

|

|

WDTRST |

WDTPRG |

A7h |

|

1111 1111 |

|

XXXX0XX0 |

|

|

|

XXXX XXXX |

XXXX X000 |

||

|

|

|

|

|

|||||

SCON |

SBUF |

|

|

|

|

|

|

9Fh |

|

0000 0000 |

XXXX XXXX |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|||

P1 |

|

|

|

|

|

|

|

97h |

|

1111 1111 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||

TCON |

TMOD |

TL0 |

TL1 |

TH0 |

TH1 |

AUXR |

CKCON |

8Fh |

|

0000 0000 |

0000 0000 |

0000 0000 |

0000 0000 |

0000 0000 |

0000 0000 |

XXXXXX00 |

XXXX XXX0 |

||

|

|||||||||

|

|

|

|

|

|

|

|

|

|

P0 |

SP |

DPL |

DPH |

|

|

|

PCON |

87h |

|

1111 1111 |

0000 0111 |

0000 0000 |

0000 0000 |

|

|

|

00X1 0000 |

||

|

|

|

|

||||||

0/8 |

1/9 |

2/A |

3/B |

4/C |

5/D |

6/E |

7/F |

|

|

|

|

|

|

|

|

|

|

|

|

reserved

Rev. C - 06 March, 2001 |

3 |

TS80C51RA2/RD2

TS83C51RB2/RC2/RD2

TS87C51RB2/RC2/RD2

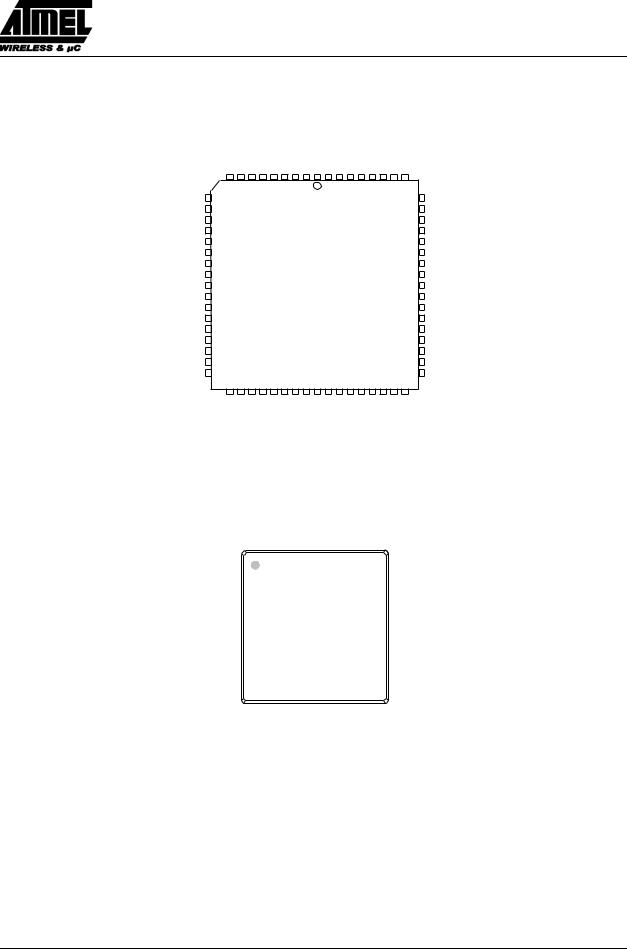

5. Pin Configuration

P1.0 / T2 |

|

1 |

|

|

40 |

|

|

VCC |

|

|

||||||

|

|

|

|

|

|

|

||||||||||

P1.1 / T2EX |

|

2 |

|

|

39 |

|

|

P0.0 |

/ A0 |

|

|

|||||

|

|

|

|

|

|

|

||||||||||

|

P1.2 |

|

3 |

|

|

38 |

|

|

P0.1 |

/ A1 |

|

|

||||

|

|

|

|

|

|

|

|

|||||||||

|

P1.3 |

|

4 |

|

|

37 |

|

P0.2 / A2 |

|

|

||||||

|

|

|

|

|

|

|||||||||||

P1.4 |

|

5 |

|

|

36 |

|

|

P0.3 / A3 |

|

|

||||||

|

|

|

|

|

|

|||||||||||

|

P1.5 |

|

6 |

|

|

35 |

|

|

P0.4 |

/ A4 |

|

|

||||

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

P0.5 |

/ A5 |

|

|

|||||||

|

P1.6 |

|

7 |

|

|

34 |

|

|

|

|

||||||

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

P1.7 |

|

8 |

|

|

33 |

|

|

P0.6 |

/ A6 |

|

P1.5 |

||||

|

|

|

|

|

|

|||||||||||

|

RST |

|

9 |

|

|

32 |

|

|

P0.7 |

/ A7 |

|

|||||

|

|

|

|

|

|

|

P1.6 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P3.0/RxD |

|

10 |

PDIL/ |

31 |

|

|

EA/VPP |

|||||||||

|

|

|

|

P1.7 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

P3.1/TxD |

|

11 |

30 |

|

|

ALE/PROG |

||||||||||

|

|

|

||||||||||||||

|

|

|

|

|

|

RST |

||||||||||

|

|

|

|

|

12 CDIL40 |

|

|

|

PSEN |

|

|

|||||

P3.2/INT0 |

|

29 |

|

|

P3.0/RxD |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

P2.7 |

/ A15 |

||||

P3.3/INT1 |

|

13 |

|

|

28 |

|

|

|||||||||

|

|

|

|

|

NIC* |

|||||||||||

P3.4/T0 |

|

14 |

|

|

27 |

|

|

P2.6 |

/ A14 |

|||||||

|

|

|

||||||||||||||

|

|

|

|

|

P2.5 |

/ A13 |

P3.1/TxD |

|||||||||

P3.5/T1 |

|

15 |

|

|

26 |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

P2.4 |

/ A12 |

P3.2/INT0 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||

P3.6/WR |

|

16 |

|

|

25 |

|

|

|||||||||

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

P2.3 |

/ A11 |

P3.3/INT1 |

|||||||||

|

|

|

|

|

17 |

|

|

24 |

|

|

||||||

P3.7/RD |

|

|

|

|

|

P2.2 |

/ A10 |

P3.4/T0 |

||||||||

XTAL2 |

|

18 |

|

|

23 |

|

|

|||||||||

|

|

|

|

|

P3.5/T1 |

|||||||||||

XTAL1 |

|

19 |

|

|

22 |

|

|

P2.1 |

/ A9 |

|||||||

|

|

|

|

|

|

|

||||||||||

|

VSS |

|

20 |

|

|

21 |

|

|

P2.0 |

/ A8 |

|

|

||||

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1.4 |

P1.3 P1.2 |

|

P1.1/T2EX |

|

P1.0/T2 |

|

VSS1/NIC* |

|

|

VCC |

|

P0.0/AD0 |

|

P0.1/AD1 |

|

P0.2/AD2 |

|

P0.3/AD3 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 43 42 |

41 |

40 |

39 38 |

37 |

36 |

35 |

34 |

|||||||||||||||

|

|

P1.5 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

P1.6 |

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

P1.7 |

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

RST |

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

P3.0/RxD |

|

|

5 |

|

|

|

|

|

|

VQFP44 1.4 |

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

NIC* |

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

P3.1/TxD |

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P3.2/INT0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P3.3/INT1 |

|

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

P3.4/T0 10

P3.5/T1 11

12 13 14 15 16 17 18 19 20 21 22

P3.6/WR |

|

P3.7/RD |

XTAL2 |

XTAL1 |

VSS |

NIC* |

P2.0/A8 |

P2.1/A9 |

P2.2/A10 |

P2.3/A11 |

P2.4/A12 |

|

|||||||||||

|

7

8

9

10

11

12

13

14

15

16

17

33

32

31

30

29

28

27

26

25

24

23

|

|

P1.4 |

|

P1.3 |

P1.2 |

P1.1/T2EX |

P1.0/T2 |

VSS1/NIC* |

VCC |

P0.0/AD0 |

P0.1/AD1 |

P0.2/AD2 |

P0.3/AD3 |

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

5 |

4 |

3 |

2 |

44 |

43 |

42 |

41 |

40 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

39 |

|

|

|

|

|

|

|

|

|

|

|

|

|

38 |

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

|

|

|

|

|

|

|

|

|

|

|

|

|

35 |

|

|

|

|

|

PLCC/CQPJ 44 |

|

|

34 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

30 |

|

|

|

|

|

|

|

|

|

|

|

|

|

29 |

18 19 20 21 22 23 24 25 26 27 28 |

|||||||||||||

|

|

P3.6/WR |

|

P3.7/RD |

XTAL2 |

XTAL1 |

VSS |

NIC* |

P2.0/A8 |

P2.1/A9 |

P2.2/A10 |

P2.3/A11 |

P2.4/A12 |

|

|

||||||||||||

|

|

|

|||||||||||

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7

EA/VPP

NIC*

ALE/PROG

PSEN

P2.7/A15

P2.6/A14

P2.5/A13

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7

EA/VPP

NIC*

ALE/PROG

PSEN

P2.7/A15

P2.6/A14

P2.5/A13

*NIC: No Internal Connection

4 |

Rev. C - 06 March, 2001 |

TS80C51RA2/RD2

TS83C51RB2/RC2/RD2

TS87C51RB2/RC2/RD2

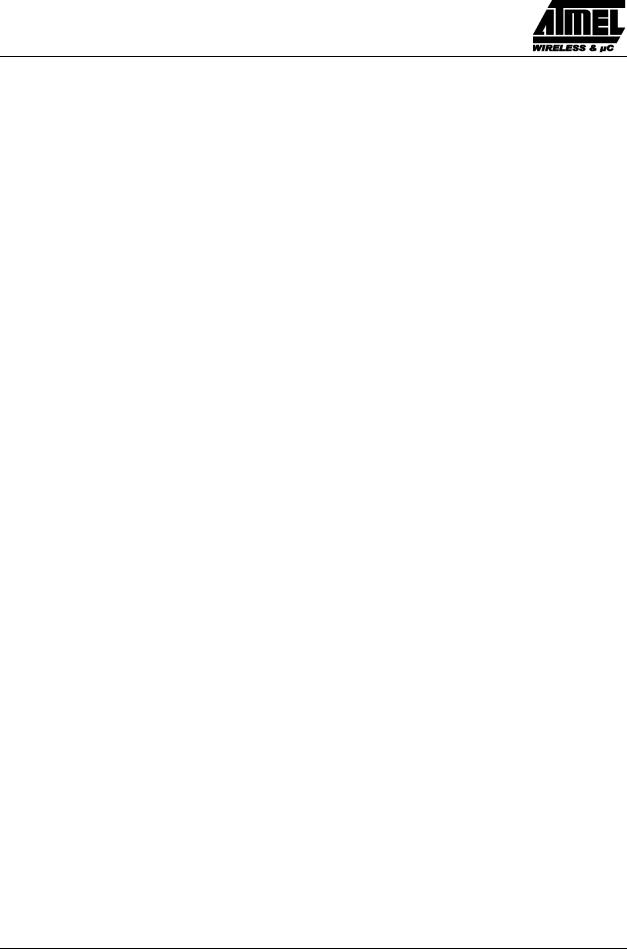

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P0.4/AD4 |

P5.4 |

P5.3 |

|

P0.5/AD5 |

|

P0.6/AD6 |

NIC |

|

P0.7/AD7 |

|

EA/VPP |

|

NIC |

|

|

ALE/PROG |

|

PSEN |

|

NIC |

|

P2.7/A15 |

P2.6/A14 |

P5.2 |

|

P5.1 |

P2.5/A13 |

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

9 |

8 |

7 |

6 |

5 |

|

4 |

3 |

|

|

2 |

1 |

|

68 67 66 65 64 |

|

63 62 61 |

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

P5.5 |

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

60 |

P5.0 |

|

|||||||

P0.3/AD3 |

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

59 |

P2.4/A12 |

|

||||||||

P0.2/AD2 |

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

58 |

P2.3/A11 |

|

||||||||

|

P5.6 |

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

57 |

P4.7 |

|

|||||||

P0.1/AD1 |

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

56 |

P2.2/A10 |

|

||||||||

P0.0/AD0 |

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

55 |

P2.1/A9 |

|

||||||||

|

P5.7 |

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

54 |

P2.0/A8 |

|

|||||||

|

VCC |

17 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PLCC 68 |

|

|

|

|

|

|

|

|

|

|

|

|

53 |

P4.6 |

|

||||||||||||||||||||||

|

NIC |

18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

52 |

NIC |

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

P1.0/T2 |

19 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

51 |

VSS |

|

|||||||

|

P4.0 |

20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

50 |

P4.5 |

|

|||||||

P1.1/T2EX |

21 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

49 |

XTAL1 |

|

||||||||

|

P1.2 |

22 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

XTAL2 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1.3 |

23 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

47 |

P3.7/RD |

|

|||||||

|

P4.1 |

24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

46 |

P4.4 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1.4 |

25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

45 |

P3.6/WR |

|

|||||||

|

P4.2 |

26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |

P4.3 |

|

|||||||

|

|

27 28 |

29 30 31 32 33 34 35 36 37 38 39 40 |

|

41 42 43 |

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||

|

|

|

P1.5 |

P1.6 |

P1.7 |

RST |

|

NIC |

NIC |

|

NIC |

|

P3.0/RxD |

NIC |

|

|

NIC |

NIC |

NIC |

|

P3.1/TxD |

|

|

|

P3.3/INT1 |

|

P3.4/T0 |

P3.5/T1 |

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

P3.2/INT0 |

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

P0.4/AD4 |

P5.4 |

P5.3 P0.5/AD5 |

P0.6/AD6 |

P0.7/AD7 |

|

|

EA/VPP NIC |

|

ALE/PROG |

|

PSEN |

P2.7/A15 P2.6/A14 |

|

P5.2 |

P5.1 P2.5/A13 |

P5.0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P5.5 |

|

|

|

|

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 |

|

|

|

|

P2.4/A12 |

|

||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

|

|

|

|

|

||||||||

|

P0.3/AD3 |

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

47 |

|

|

|

|

P2.3/A11 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

P0.2/AD2 |

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

46 |

|

|

|

|

P4.7 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

P5.6 |

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

45 |

|

|

|

|

P2.2/A10 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

P0.1/AD1 |

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |

|

|

|

|

P2.1/A9 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

P0.0/AD0 |

|

|

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

43 |

|

|

|

|

P2.0/A8 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

P5.7 |

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

42 |

|

|

|

|

P4.6 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

VCC |

|

|

|

|

8 |

|

|

|

|

|

|

|

|

VQFP64 1.4 |

|

|

|

|

|

|

|

|

|

41 |

|

|

|

|

NIC |

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

VSS |

|

|

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

40 |

|

|

|

|

VSS |

|

||||||||||||||||||||||||

|

P1.0/T2 |

|

|

|

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

39 |

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P4.5 |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

P4.0 |

|

|

|

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

38 |

|

|

|

|

XTAL1 |

|

|||||||

|

P1.1/T2EX |

|

|

|

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

|

|

|

|

XTAL2 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

P1.2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

|

|

|

|

P3.7/RD |

|

||||||||

|

P1.3 |

|

|

|

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

35 |

|

|

|

|

P4.4 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

P4.1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

34 |

|

|

|

|

P3.6/WR |

|

||||||||

|

P1.4 |

|

|

|

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

|

|

|

P4.3 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P4.2 |

P1.5 |

P1.6 P1.7 |

RST |

NIC |

NIC NIC |

|

P3.0/RxD |

|

NIC |

NIC P3.1/TxD |

|

P3.2/INT0 |

|

P3.3/INT1 P3.4/T0 |

P3.5/T1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||

|

NIC: No InternalConnection |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

Rev. C - 06 March, 2001 |

5 |

TS80C51RA2/RD2

TS83C51RB2/RC2/RD2

TS87C51RB2/RC2/RD2

Mnemonic |

|

Pin Number |

Type |

|

|

|

|

Name And Function |

|

|

|

|

|

|

|

|

|||

DIL |

LCC |

VQFP 1.4 |

|

|

|

|

|||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

VSS |

20 |

22 |

16 |

I |

|

Ground: 0V reference |

|||

Vss1 |

|

1 |

39 |

I |

|

Optional Ground: Contact the Sales Office for ground connection. |

|||

|

|

|

|

|

|

|

|||

VCC |

40 |

44 |

38 |

I |

|

Power Supply: This is the power supply voltage for normal, idle and power- |

|||

|

down operation |

||||||||

P0.0-P0.7 |

39-32 |

43-36 |

37-30 |

I/O |

|

Port 0: Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s |

|||

|

|

|

|

|

|

written to them float and can be used as high impedance inputs. Port 0 pins must |

|||

|

|

|

|

|

|

be polarized to Vcc or Vss in order to prevent any parasitic current consumption. |

|||

|

|

|

|

|

|

Port 0 is also the multiplexed low-order address and data bus during access to |

|||

|

|

|

|

|

|

external program and data memory. In this application, it uses strong internal |

|||

|

|

|

|

|

|

pull-up when emitting 1s. Port 0 also inputs the code bytes during EPROM |

|||

|

|

|

|

|

|

programming. External pull-ups are required during program verification during |

|||

|

|

|

|

|

|

which P0 outputs the code bytes. |

|||

|

|

|

|

|

|

|

|||

P1.0-P1.7 |

1-8 |

2-9 |

40-44 |

I/O |

|

Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 |

|||

|

|

|

1-3 |

|

|

pins that have 1s written to them are pulled high by the internal pull-ups and |

|||

|

|

|

|

|

|

can be used as inputs. As inputs, Port 1 pins that are externally pulled low will |

|||

|

|

|

|

|

|

source current because of the internal pull-ups. Port 1 also receives the low-order |

|||

|

|

|

|

|

|

address byte during memory programming and verification. |

|||

|

|

|

|

|

|

Alternate functions for Port 1 include: |

|||

|

1 |

2 |

40 |

I/O |

|

T2 (P1.0): Timer/Counter 2 external count input/Clockout |

|||

|

2 |

3 |

41 |

I |

|

T2EX (P1.1): Timer/Counter 2 Reload/Capture/Direction Control |

|||

|

3 |

4 |

42 |

I |

|

ECI (P1.2): External Clock for the PCA |

|||

|

4 |

5 |

43 |

I/O |

|

CEX0 (P1.3): Capture/Compare External I/O for PCA module 0 |

|||

|

5 |

6 |

44 |

I/O |

|

CEX1 (P1.4): Capture/Compare External I/O for PCA module 1 |

|||

|

6 |

7 |

45 |

I/O |

|

CEX0 (P1.5): Capture/Compare External I/O for PCA module 2 |

|||

|

7 |

8 |

46 |

I/O |

|

CEX0 (P1.6): Capture/Compare External I/O for PCA module 3 |

|||

|

8 |

9 |

47 |

I/O |

|

CEX0 (P1.7): Capture/Compare External I/O for PCA module 4 |

|||

|

|

|

|

|

|

|

|||

P2.0-P2.7 |

21-28 |

24-31 |

18-25 |

I/O |

|

Port 2: Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 |

|||

|

|

|

|

|

|

pins that have 1s written to them are pulled high by the internal pull-ups and |

|||

|

|

|

|

|

|

can be used as inputs. As inputs, Port 2 pins that are externally pulled low will |

|||

|

|

|

|

|

|

source current because of the internal pull-ups. Port 2 emits the high-order address |

|||

|

|

|

|

|

|

byte during fetches from external program memory and during accesses to external |

|||

|

|

|

|

|

|

data memory that use 16-bit addresses (MOVX @DPTR).In this application, it |

|||

|

|

|

|

|

|

uses strong internal pull-ups emitting 1s. During accesses to external data memory |

|||

|

|

|

|

|

|

that use 8-bit addresses (MOVX @Ri), port 2 emits the contents of the P2 SFR. |

|||

|

|

|

|

|

|

Some Port 2 pins (P2.0 to P2.5) receive the high order address bits during |

|||

|

|

|

|

|

|

EPROM programming and verification: |

|||

|

|

|

|

|

|

|

|||

P3.0-P3.7 |

10-17 |

11, |

5, |

I/O |

|

Port 3: Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 |

|||

|

|

13-19 |

7-13 |

|

|

pins that have 1s written to them are pulled high by the internal pull-ups and |

|||

|

|

|

|

|

|

can be used as inputs. As inputs, Port 3 pins that are externally pulled low will |

|||

|

|

|

|

|

|

source current because of the internal pull-ups. Some Port 3 pins (P3.4 to P3.5) |

|||

|

|

|

|

|

|

receive the high order address bits during EPROM programming and verification. |

|||

|

|

|

|

|

|

Port 3 also serves the special features of the 80C51 family, as listed below. |

|||

|

10 |

11 |

5 |

I |

|

RXD (P3.0): Serial input port |

|||

|

11 |

13 |

7 |

O |

|

TXD (P3.1): Serial output port |

|||

|

12 |

14 |

8 |

I |

|

|

|

|

(P3.2): External interrupt 0 |

|

|

INT0 |

|||||||

|

13 |

15 |

9 |

I |

|

|

|

|

(P3.3): External interrupt 1 |

|

|

INT1 |

|||||||

|

14 |

16 |

10 |

I |

|

T0 (P3.4): Timer 0 external input |

|||

|

15 |

17 |

11 |

I |

|

T1 (P3.5): Timer 1 external input |

|||

|

16 |

18 |

12 |

O |

|

|

|

(P3.6): External data memory write strobe |

|

|

|

WR |

|||||||

|

17 |

19 |

13 |

O |

|

|

(P3.7): External data memory read strobe |

||

|

|

RD |

|||||||

|

|

|

|

|

|

|

|

|

|

6 |

Rev. C - 06 March, 2001 |

|

|

|

|

|

|

TS80C51RA2/RD2 |

|

|

|

|

|

|

TS83C51RB2/RC2/RD2 |

|

|

|

|

|

|

TS87C51RB2/RC2/RD2 |

|

|

|

|

|

|

|

|

Reset |

9 |

10 |

4 |

I |

Reset: A high on this pin for two machine cycles while the oscillator is running, |

|

|

|

|

|

|

resets the device. An internal diffused resistor to VSS permits a power-on reset |

|

|

|

|

|

|

using only an external capacitor to VCC. If the hardware watchdog reaches its |

|

|

|

|

|

|

time-out, the reset pin becomes an output during the time the internal reset is |

|

|

|

|

|

|

activated. |

|

|

|

|

|

|

|

Rev. C - 06 March, 2001 |