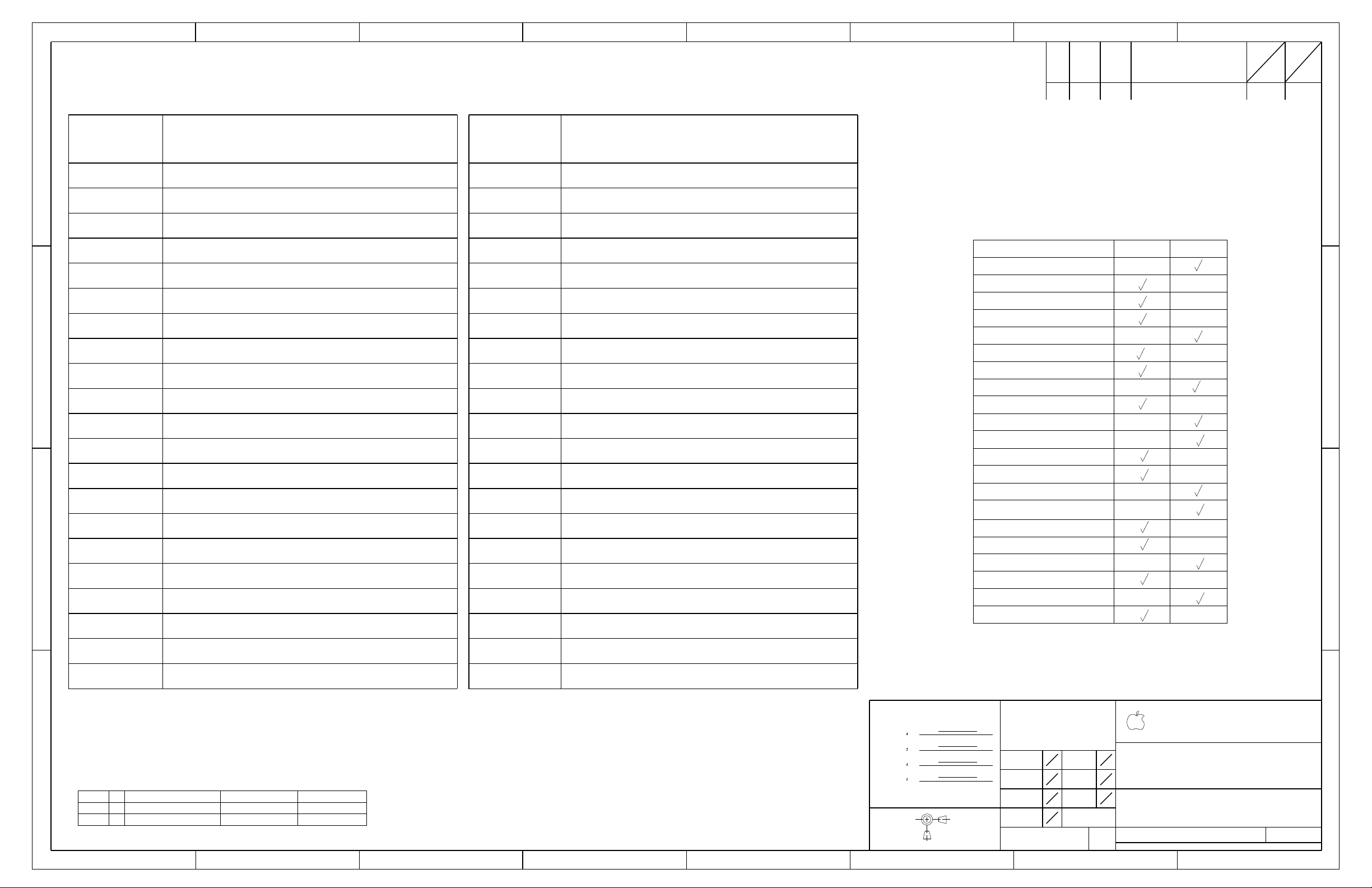

Apple G4 MLB PB17 INCH 051-6531 Schematic

TABLE_5_ITEM

DESCRIPTION OF CHANGE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

Apple Computer Inc.

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

NOTICE OF PROPRIETARY PROPERTY

TITLE

DRAWING NUMBER

SHT

OF

METRIC

DRAFTER

ENG APPD

QA APPD

RELEASE

DESIGN CK

MFG APPD

DESIGNER

SCALE

NONE

MATERIAL/FINISH

NOTED AS

APPLICABLE

SIZE

D

THIRD ANGLE PROJECTION

DIMENSIONS ARE IN MILLIMETERS

XX

X.XX

X.XXX

DO NOT SCALE DRAWING

REV

ZONE

ECN

CK

APPD

DATE

ENG

APPD

DATE

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

ANGLES

REFERENCE DESIGNATOR(S)

BOM OPTION

TABLE_5_HEAD

QTY

DESCRIPTION

PART#

TABLE_5_ITEM

09/04/2003

INTREPID GPIOS/SERIAL/USB INTERFACES/SSCG

BATTERY CHARGER AND CONNECTOR

MARVELL GIGABIT ETHERNET PHY

SERIAL DEBUG (JOLLY ROGER, PWR/NMI/RESET)

SCHEM,MLB,PB17"

17

STUFF

EXT_TMDS

ATI_MEMIO_LO

ATI_MEMIO_HI

INTREPID_USB

NEC_USB

1_5V_MAXBUS

D3_HOT

D3_COLD

FIREWIRE A/B CONNECTORS, PORT POWER LIMITER

25

24

5V_HD_LOGIC

3V_HD_LOGIC

NO_4XVCORE

INT_TMDS

NO_SSCG

SPIDEY - KBD,TPAD,HALL EFFECT,PWR BUTTON

DUAL-CHANNEL LVDS

CONTENTS

PAGE

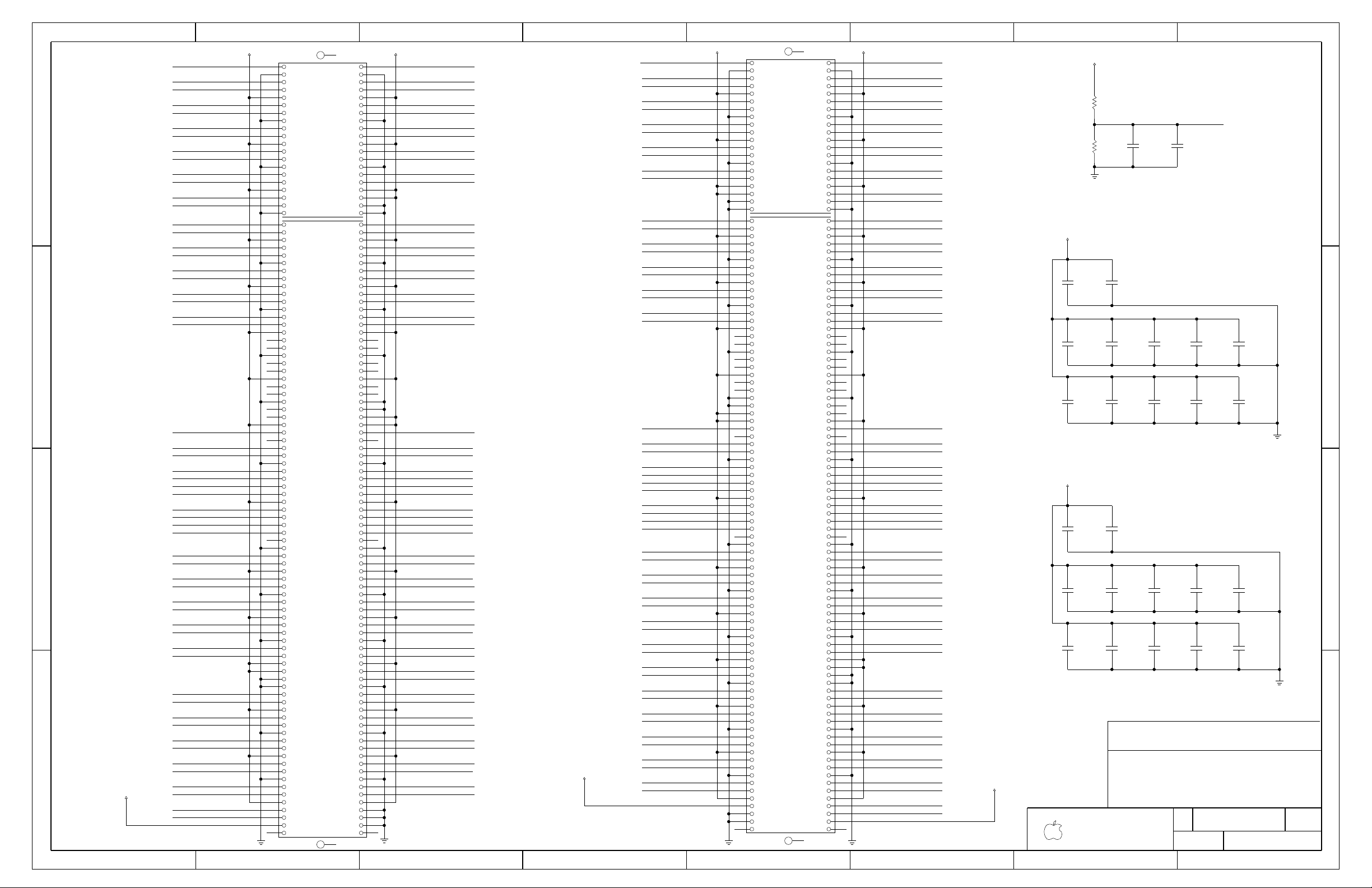

INTREPID AGP 4X/PCI

INTREPID MEMORY INTERFACE / BOOT ROM

10

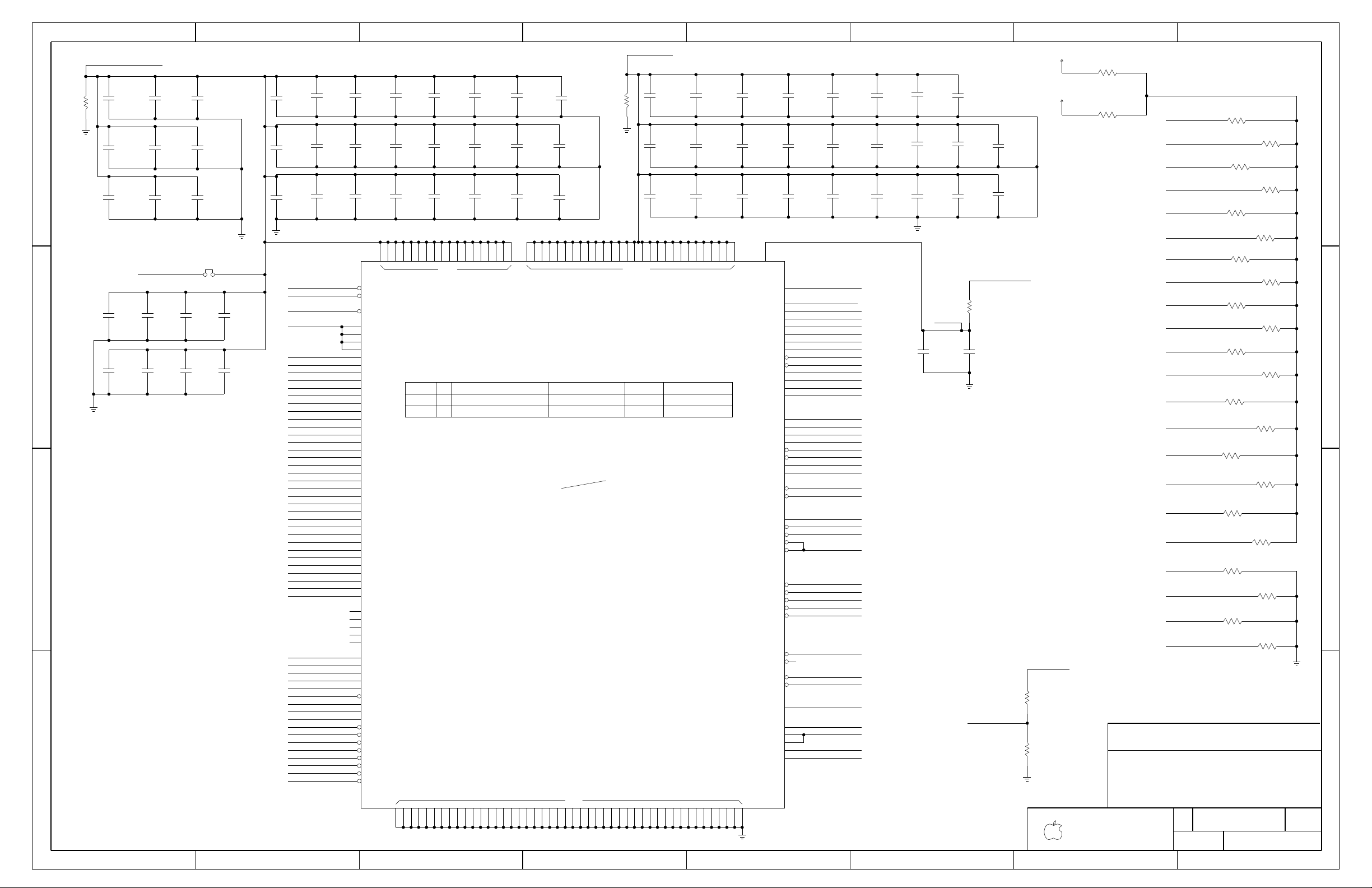

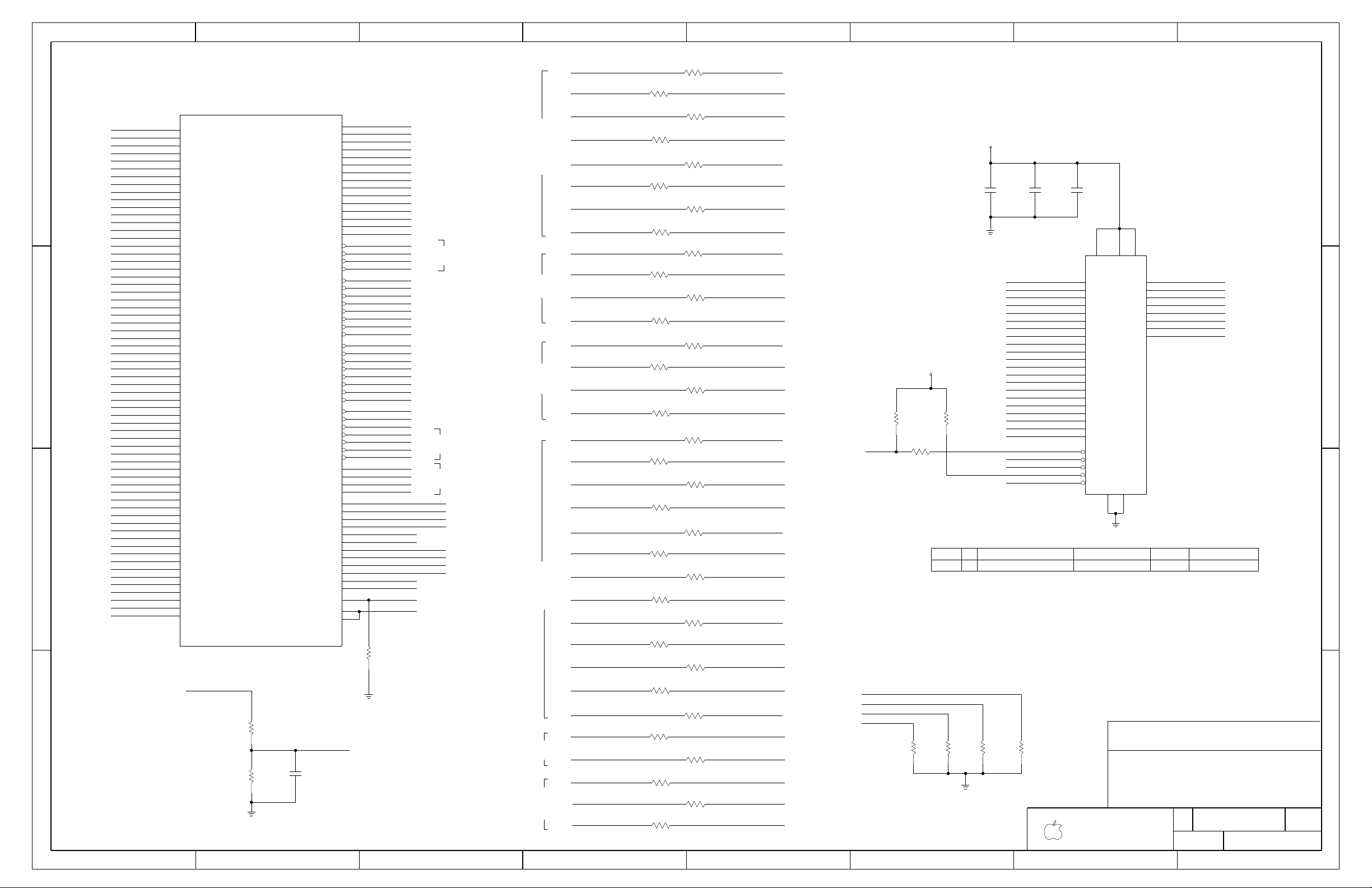

MPC7450 DATA

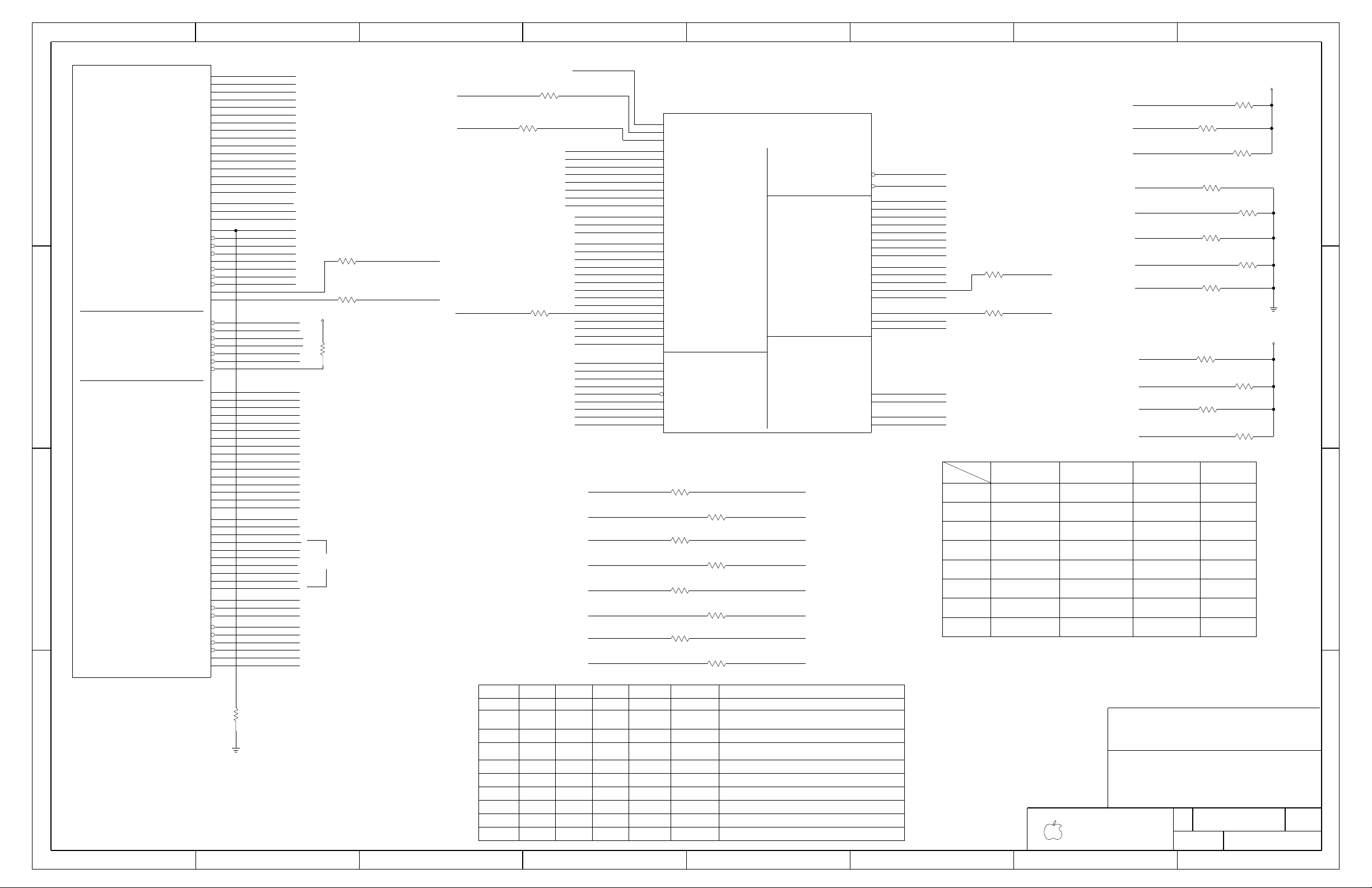

TITLE PAGE AND CONTENTS

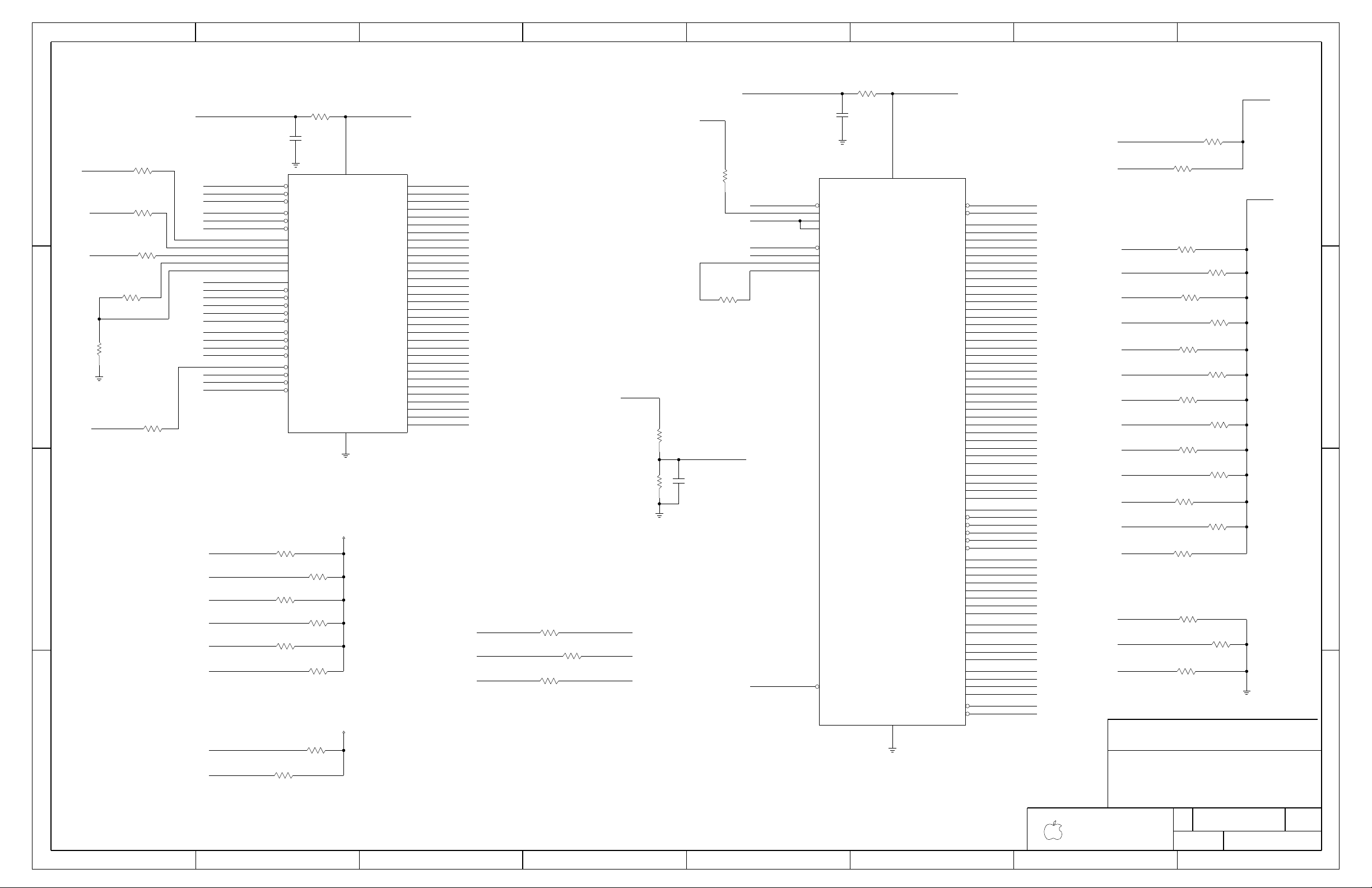

CPU PLL AND CONFIGURATION STRAPS

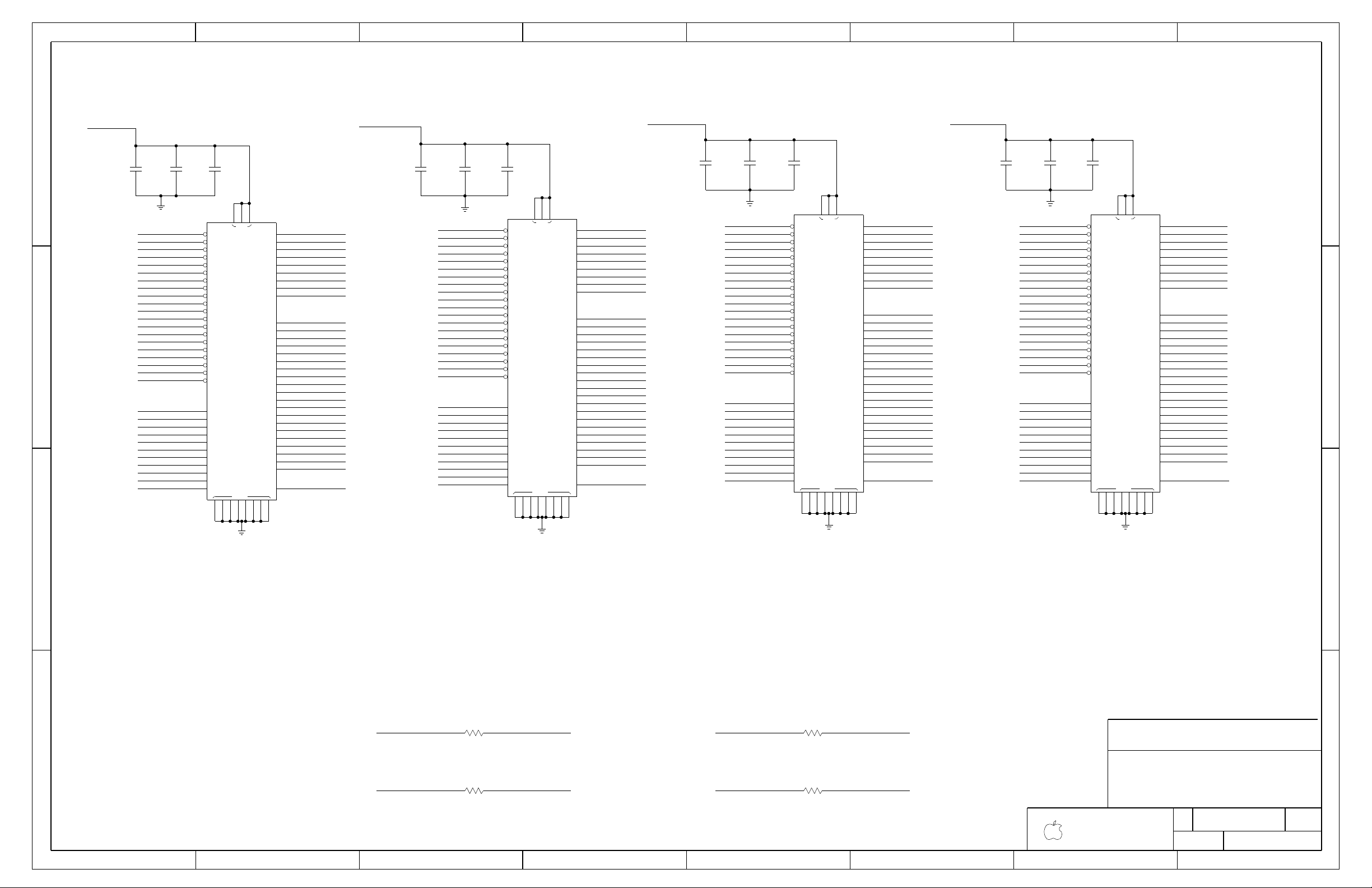

200PIN DDR MEMORY SODIMM CONNECTORS

INTREPID ENET/FW/UATA/EIDE INTERFACES

2

BBANG

NO_BBANG

32

30

1

4

5

13

11

12

14

9

18

SSCG

35

33

8

DDR MEMORY MUXES

INTREPID MAXBUS AND BOOT STRAPS

31

28

GPU_SS

NO STUFF

GPU_SWITCH

SERIAL_DEBUG

VCORE_OFFSET

1_8V_MAXBUS

BOM OPTIONS

3

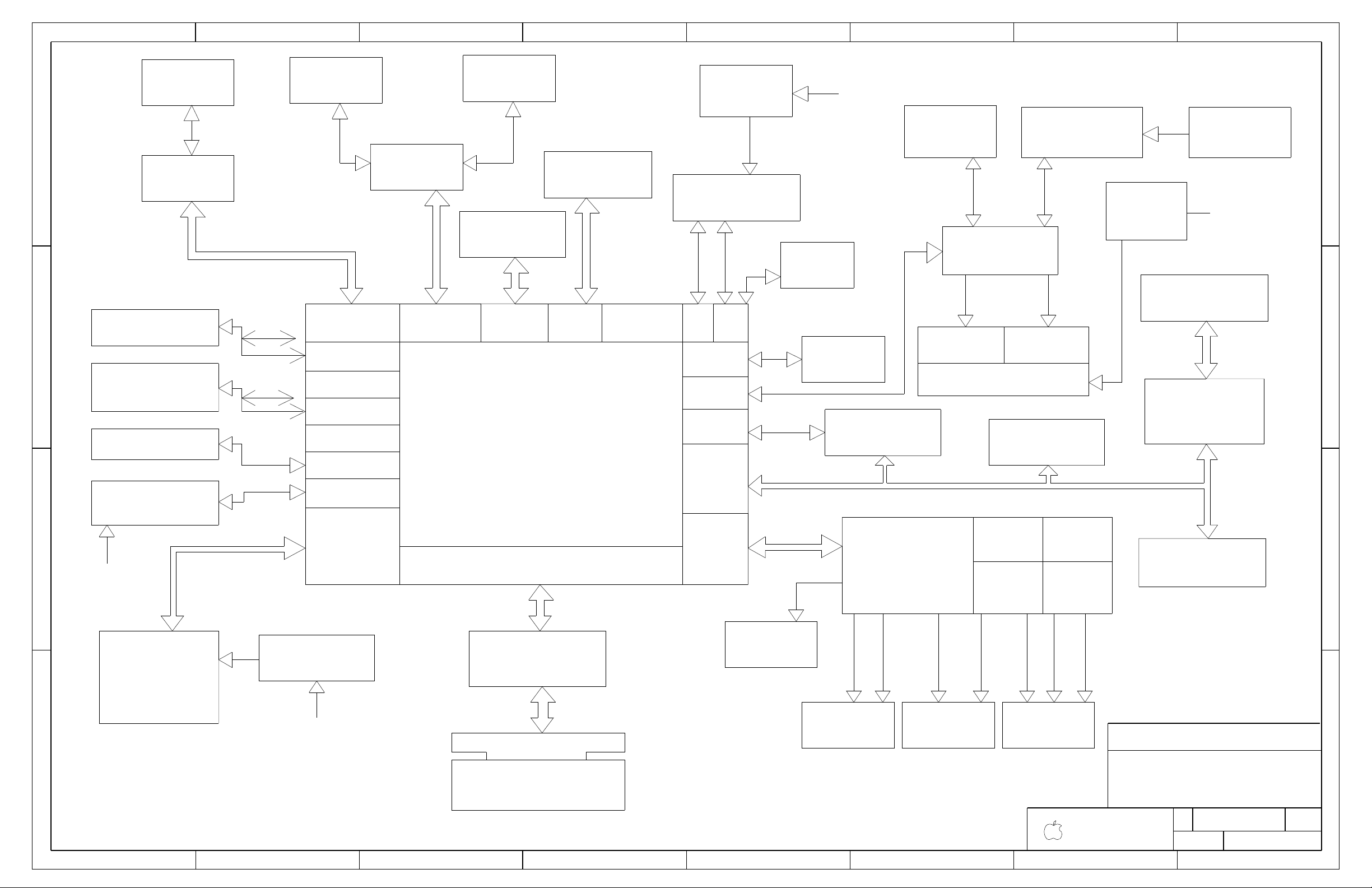

SYSTEM BLOCK DIAGRAM

20

SIL1162 TMDS TRANSMITTER

39

PAGE

26

27

29

22

23

COMPONENT LOCATIONS

SIGNAL NAMES

FUNCTIONAL TEST POINTS

SIGNAL CONSTRAINTS (2 OF 3) - DIGITAL/DIFF

1.5V/ 1.8V / 2.5V SYSTEM POWER SUPPLIES

CPU CORE VOLTAGE POWER SUPPLY

3.3V / 5V SYSTEM POWER SUPPLIES

12.8V SYSTEM POWER SUPPLY / PMU POWER SUPPLY

PMU (POWER MANAGEMENT UNIT)

INTERNAL CONNECTORS - DVD,

LMU, LIGHT SENSOR, BOOTBANGER, SLEEP LED

36

37

38

40

M10 ANALOG, POWER, GND

SIGNAL CONSTRAINTS (3 OF 3) - POWER NETS

43-44

41-42

FAN CONTROLLER, MODEM, SOUND

VIDEO CONNECTORS - INVERTER, DVI, S-VIDEO

CARDSLOT, HARD DRIVE, LEFT USB/BLUETOOTH

USB 2.0

SIGNAL CONSTRAINTS (1 OF 3) - DIGITAL/CLK

REVISION HISTORY (1 OF 1)

M10 LVDS/TMDS/VGA/GPIO & GPU VCORE

M10 AGP & CLOCKS

CARDBUS CONTROLLER (PCI1510)

INTREPID DECOUPLING

INTREPID POWER RAILS

FIREWIRE A/B PHY

34

21

16

15

19

7

6

MPC7450 MAXBUS INTERFACE

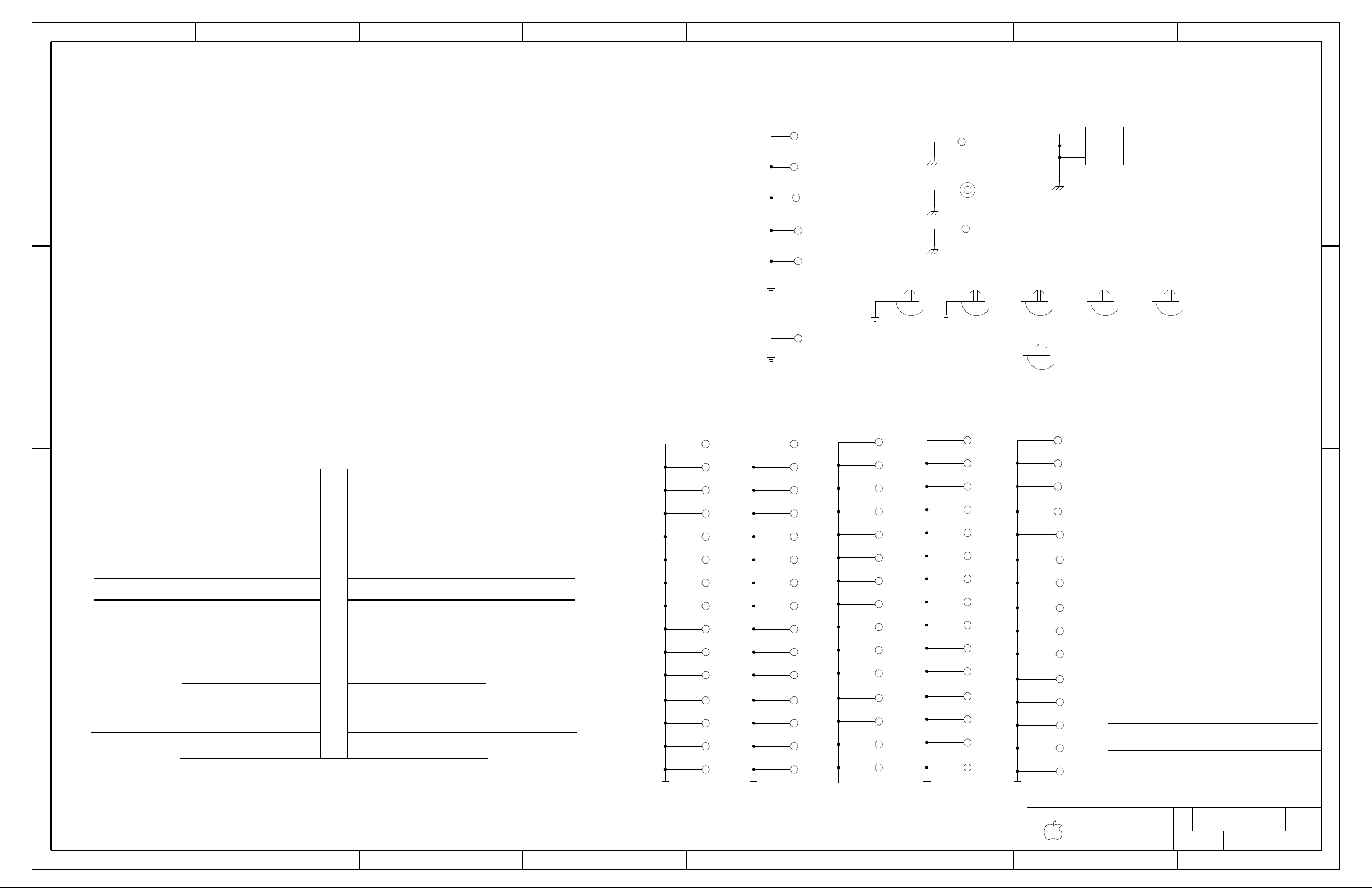

PCB NOTES AND HOLES

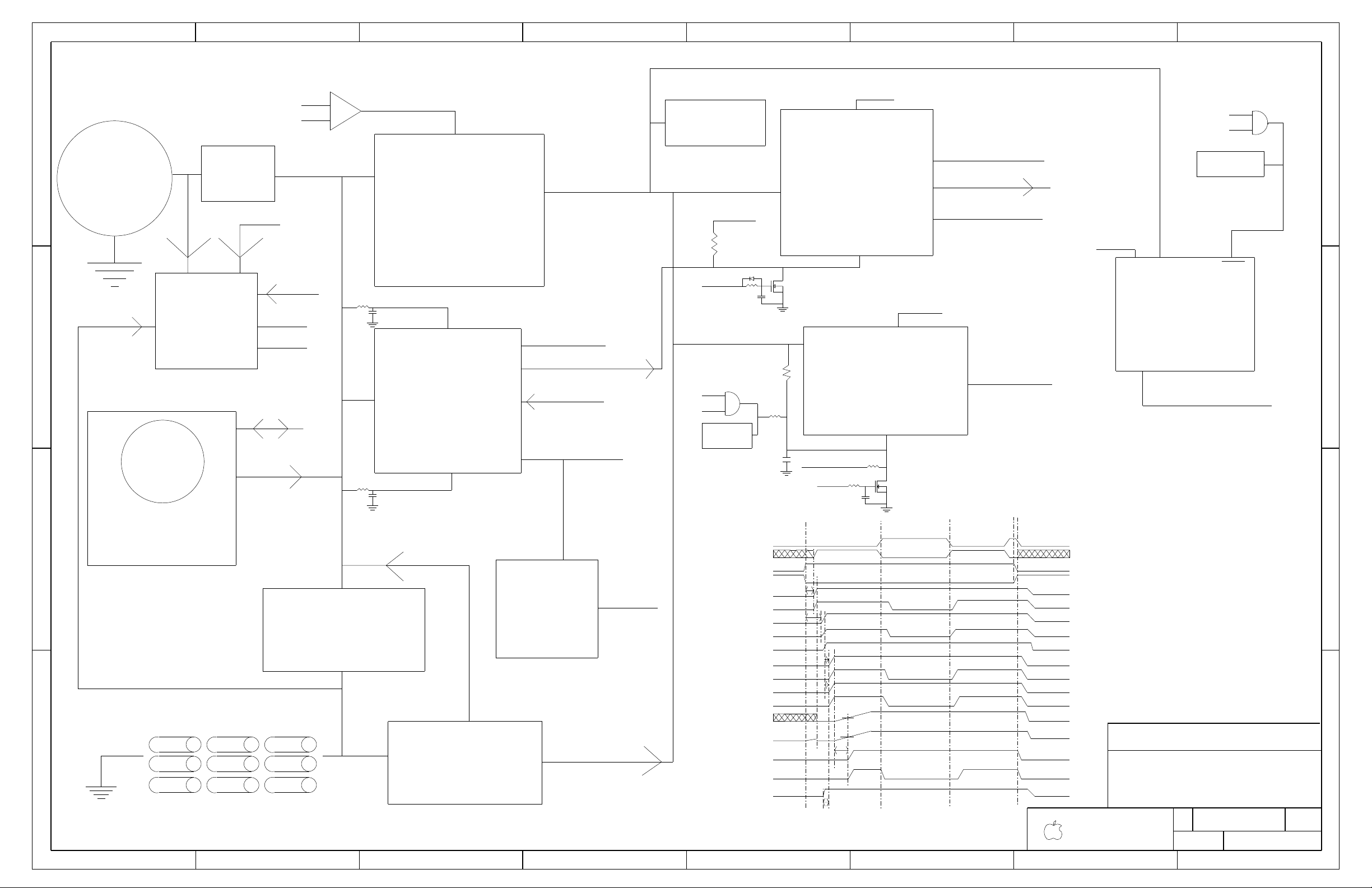

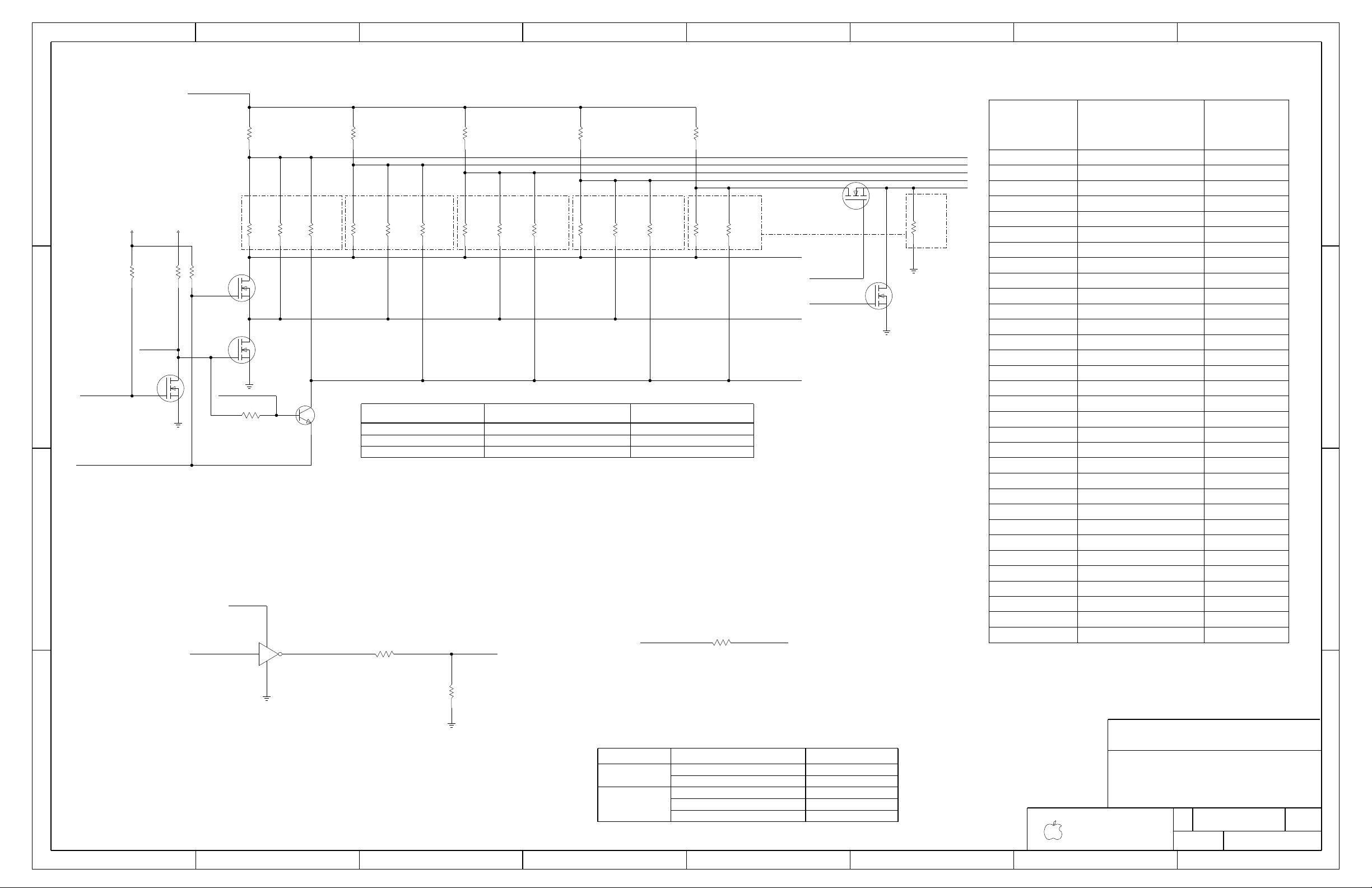

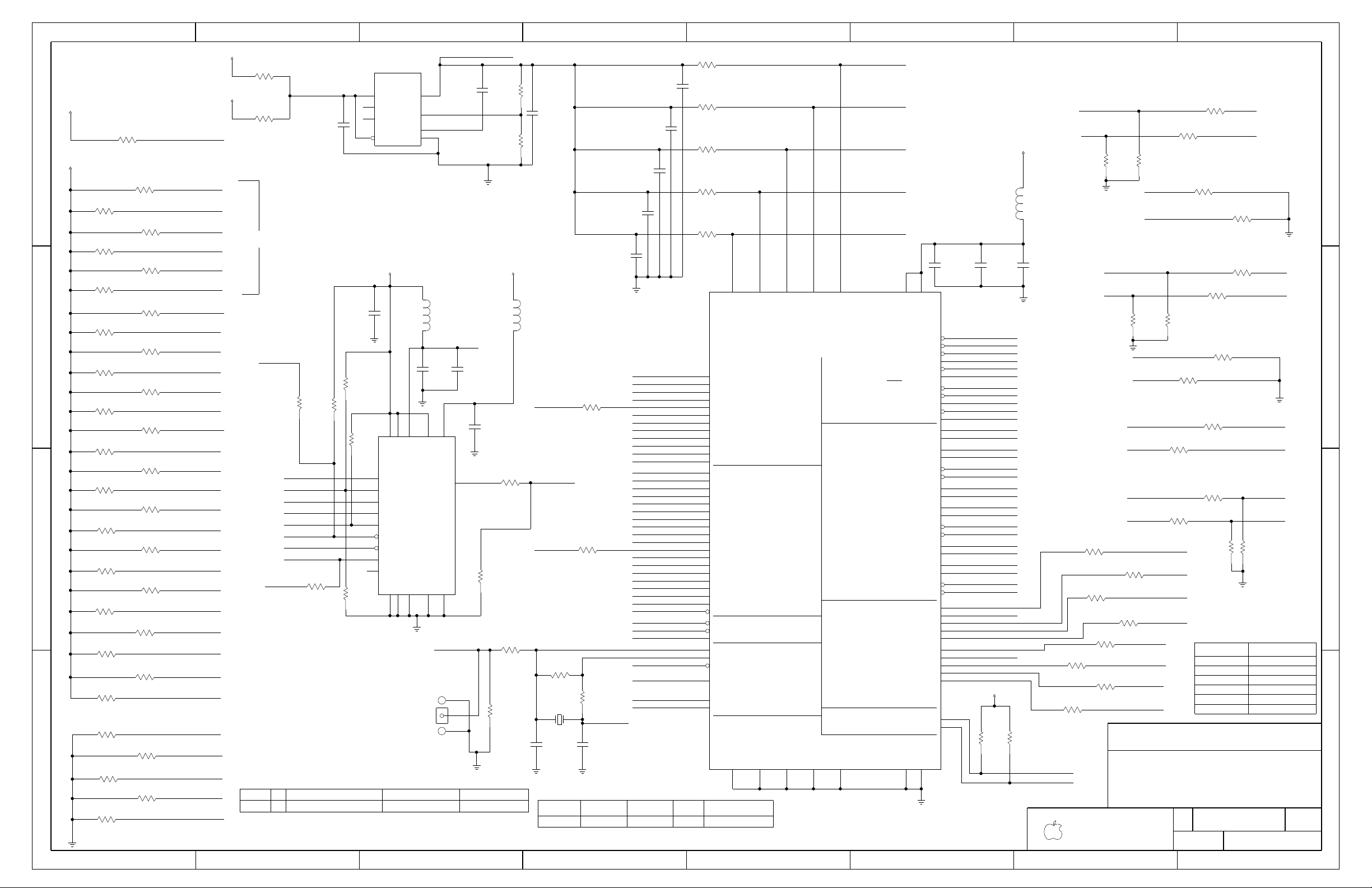

POWER BLOCK DIAGRAM

CONTENTS

1

820-1524

PCBF,MLB,PB17 INCH

PCB1

PRODUCTION RELEASED

051-6531

44

?

293301B

1

09/11/03

SCHEM,MLB,PB17 INCH

B

051-6531

SCHEM,MLB,PB17 INCH

SCH1

1

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

P.28

P.26

P.25

P.33

P.25

P.22P.22P.22

P.22

P.18-21

P.25

P.27

P.24

P.26

P.32-36

P.24

P.32

P.31

P.32

P.26

P.26

P.26

P.25

P.25

P.29

P.30

P.30

P.28

4 DATA PAIRS

UIDE

Connector

32BITS

ATI M10

33MHZ

P.13

4X AGP

INTREPID

PCI

ULTRA ATA/100

66MHZ

1.5V/3.3V

33MHZ

AIRPOPT

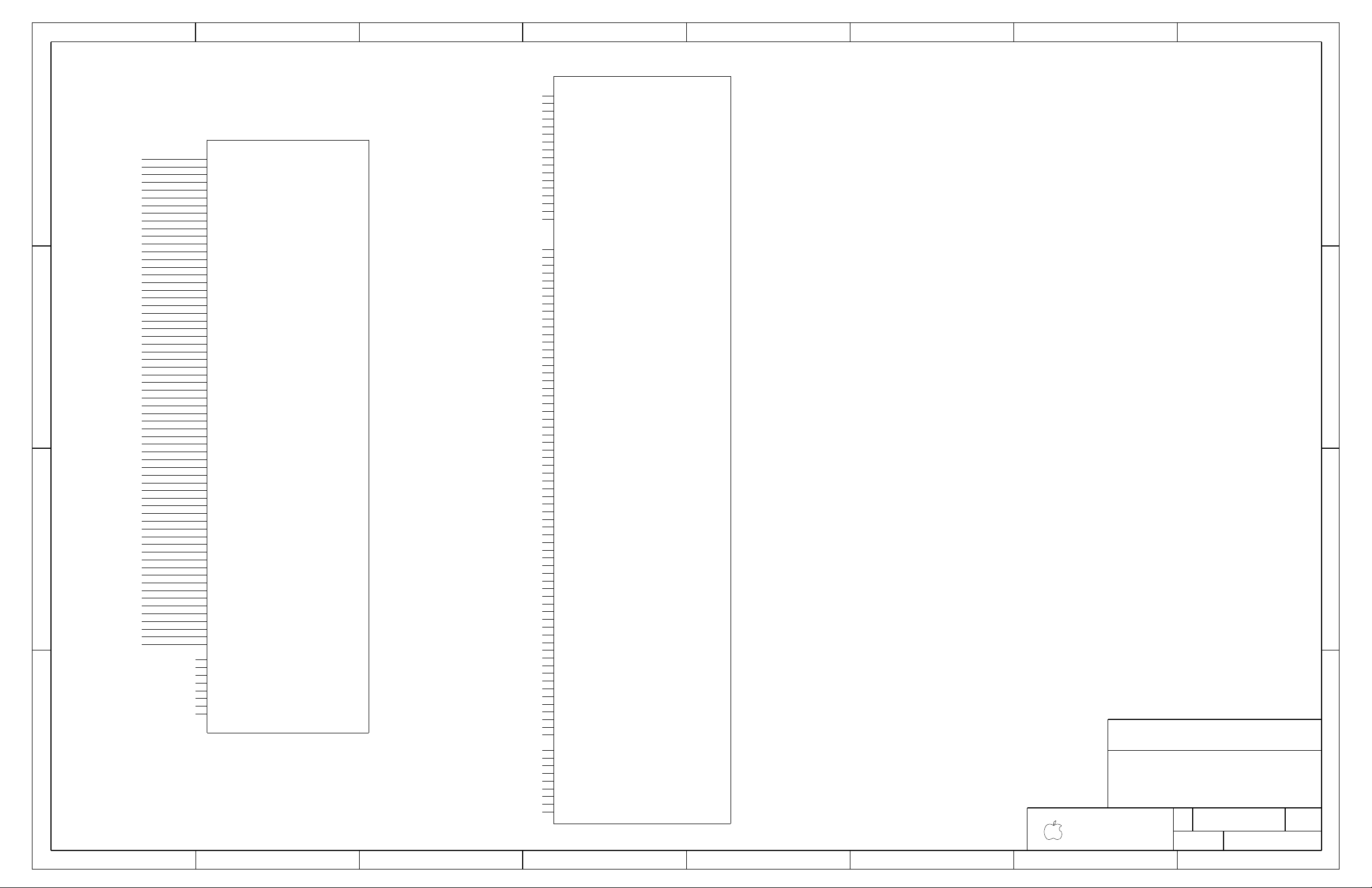

SYSTEM BLOCK DIAGRAM

Connector

64MB

S-VIDEO

TMDS

DVI-I

Connector

P.14

BOOT ROM

USB 2.0

Connector

CARDSLOT

Ethernet

G/MII

P.11

100MHZ

800 MB/S

(MPC7457)

P.14

FIREWIREETHERNET

P.15

64BIT DATA

APOLLO

CPU

U42

U52

CONTROLLER

LIGHT SENSOR

KB LED

P.10

1M X 8

U17

LMU

SLEEP

LED

3.3V

SMBUS

Battery

Connector

I2C

I2C

LMU

PMU

TRACKPAD

OPTICAL DRIVE

TI PCI1510

Keyboard

USB PORT C

USB PORT F

Inverter

FireWire

BOOTROM

VIA/PMU

EIDEUATA 100

DDR MEMORY

DDR SDRAM DIMM 1

DDR SDRAM DIMM 0

SO-DIMM Connector

2:1 DDR MUXES

10/100/1000

MAXBUS

USB PORT B

USB PORT D

(INTERNAL MEM)

MEMORY

CH. C

MEMORY

(INTERNAL MEM)

CH. A

(INTERNAL MEM)

MEMORY

CH. D

MEMORY

(INTERNAL MEM)

CH. B

Connector

CardBus

Controller

3.3V

32BITS

PCI BUS

P.7

P.5-6

P.12

P.9

P.10

P.13

P.15

P.14

P.14

P.15

P.15

P.15

P.15

P.15

64BITS

167MHZ

2.5V

(DDC TOO)

Connector

S-Video

EDID (I2C)

LVDS

Connector

LCD Panel

COMPOSITE

RGB

Connector

P.18

P.18

Connector

5V

SERIAL

& Charger

Power Supply

ConnectorConnector

SUTRO (PWR)

Connector

TUBA (SOUND)

Connector

Connector

Fan

Circuit

P.14

P.15

P.15

SCCA

Serial Debug

Connector

32BITS

PHY

Ethernet

10/100/1000

3.3V

8BIT TX

8BIT RX

125MHZ

FW - A

Connector

FW - B

PHY

2 DATA PAIRS

@ 400MHZ

@ 200MHz

8BIT TX/RX

3.3V

1394 OHCI

EIDE

I2S

I2C

BlueTooth

LEFT USB

BACKUP BATTERY

NOT USED

NOT USED

NOT USED

32BIT ADDRESS

MAXBUS

1.8V

167MHZ

PMU

INTRPEID

I2C

33MHZ

16/32 BITS

3.3V/5V

J18

U49

J24

J22

U28

J13

J11

J14

U48/J2/J4

J25

J19

U36

U39

J15

CARDBUS

J10

U26

J21

J5

U43

J8

J17

J7

J16

U11/U12/U13/U14

J20/J23

U44

J9

J3 (SHARE WITH LEFT USB)

J3 (SHARE WITH BLUETOOTH)

J12

USB 2.0

USB 2.0

P.14 P.14

P.15

USB PORT A

AGP BUS

I2CI2S

MEMORY BUS

Config

CPU PLL

Modem Board

Connector

RIGHT USB

2 DATA PAIRS

USB PORT E

051-6531

B

44

2

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

MAP31 DDR CORE

RC AT 1M*0.1UF @ 24V

RC AT 1M*0.047UF @ 24V

<100UA ALLOWED

STBYMD

+3.3V_MAIN

DC/DC

PG 35

(LTC3411)

STARTS 2.0MSEC AFTER DCDC_EN_L BECOMES LOW

(LTC1625)

SHUT-DOWN

+PBUS (12.8V)

SLEEP: D3HOT/D3COLD

BECOMES ’1’; MUCH LESS THAN THE

AFTER PMU IS UP AND RUNNING

EXT_VCC

TURNS ON AS LOW AS 0.8V/TYP 1.5V

RC CHARGING AT INT_VCC (5V)

MAP31 DDR I/O

+2.5V_MAIN

INTREPID CORE

+5V_MAIN

MAIN 2.5V/1.5V

SHUTDOWN: STOPPED

RUN: RUNNING

SLEEP: STOPPED

PG 34

PG 35

RUN: RUNNING

SLEEP: STOPPED

SHUTDOWN: STOPPED

PG 20

SHUTDOWN: STOPPED

(LTC1778)

DC/DC

PG 32

PG 33

PG 31

PG 31

PG 32

PG 32

PG 31

RUN

SHUT-DOWN

RUN

SLEEP

(D3COLD)

GPU_VCORE

(D3HOT)

GPU_VCORE

(AT LTC1778 RUN/SS)

1_5V_2_5V_OK

(MAX1715 OUTPUT)

1_5V_2_5V_OK

+1_5V_SLEEP

+2_5V_SLEEP

+2_5V_MAIN

SLEEP

SLEEP_L_LS5

3V_5V_OK

2.4V - ??? MS

+3V_SLEEP

+5V_SLEEP

+3V_MAIN

+5V_MAIN

DCDC_EN

DCDC_EN_L

(+1.4V/+1.5V)

CPU_VCORE

1M & 0.1UF @14V, IT TAKES

~5.88MS TO START SWITCHER

GPU_VCORE

SEQUENCING

DCDC_EN_L

1_5V_2_5V_OK

D3_HOT

D3_HOT

RUN/SS

INTERNAL 1.2UA CURRENT SOURCE

1_5V_2_5V_OK WILL NOT PULL LOW UNTIL

+5V_MAIN TURNS ON

DCDC_EN_L OR PMU_POWERUP_L

DCDC_EN

SLEEP

D3_COLD

VCC

RUN: RUNNING

+5V_MAIN

SEQUENCING

MAXBUS

DCDC_EN

SLEEP

VCC

SHDN

+5V_MAIN

(MAX1717)

DC/DC

BROADCOM

MAXBUS

AGP I/O

+1.5V_MAIN

+5V_MAIN

+4_6V_BU

ON1/ON2

PGOOD

3V_5V_OK

PGOOD

(MAX1715)

DC/DC

BACKLIGHT

INVERTER

TURNS CONTROL TO RUN/SS

WHEN IT’S OPEN

NO INRUSH PROTECTION

WHEN ONLY BATTERY IS CONNECTED

+5V_MAIN

14V_PBUS

+3V_PMU

LDO

+3V_PMU

(MAX1772)

CHARGER

BATTERY

BUCK

<~13.44V SHUTS-OFF

>~13.44V TURNS-ON

INRUSH

LIMITER

ADAPTER

IN

AC

(UNTIL DRAINED)

POWER BLOCK DIAGRAM

3S 3P PRISMATIC CELLS

& BOOST OUTPUT

FEED-IN PATH

U21

-

+

1V20_REF

BACKUP BATTERY

BACKUP

BATTERY

CHARGER INPUT

24V IS OUTPUT ONLY FROM

SHUTDOWN: STOPPED

RUN: RUNNING

SLEEP: RUNNING

RUN/SS - 3V

SHUTDOWN: STOPPED

SLEEP: RUNNING

RUN: RUNNING

TURNS ON OUTPUT @ 2.4V

WHEN ONLY BATTERY IS CONNECTED

NO INRUSH PROTECTION

+24V_PBUS

+24V_PBUS

+BATT

+BATT

1_5V_2_5V_OK

VCC

+1.8V_MAIN

+5V_MAIN

LOW IN SHUTDOWN

DCDC_EN_L WILL PULL ON1/ON2

DCDC_EN_L

VCC

VCC

TURNS ON AT >1V

DC/DC

(LTC3707)

MAIN 3V/5V

<100UA ALLOWED

RUN/SS - 5V

TURNS ON AT >1V

INTERNAL ZENER CLAMP TO 6V

INTERNAL ZENER CLAMP TO 6V

STARTS ~4.25MSEC AFTER DCDC_EN_L BECOMES LOW

BATTERY VOLTAGE

SHUTDOWN: RUNNING

SLEEP: RUNNING

RUN: RUNNING

NO AC: BATTERY VOLTAGE

1625 NOT RUNNING

~13.5MS

2.6 MS

~11MS

~???MS

+1_5V_MAIN

+1_8V_MAIN

2.6 MS

1.9 MS

PG 30

PG 31

+PBUS (12.8V)

AC: 12.8V

+PBUS

12.8V CHARGES BACKUP BATTERY

BACKUP BATTERY CIRCUIT CHARGES OFF +PBUS

AND PREVENTS +PBUS AND +24V_PBUS FROM DROPPING BELOW 6V

+PBUS

+PBUS

REGULATOR

HOLDS BOTH RUN/SS AT GND

RUN/SS

DDR POWER

HOWEVER, 5V SHOULD TURN ON ~2.23MS AFTER

GPU_VCORE

POWER SYSTEM ARCHITECTURE

WHEN IT’S CONNECTED TO GND

+1.2V/+1.0V

44

3

B

051-6531

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

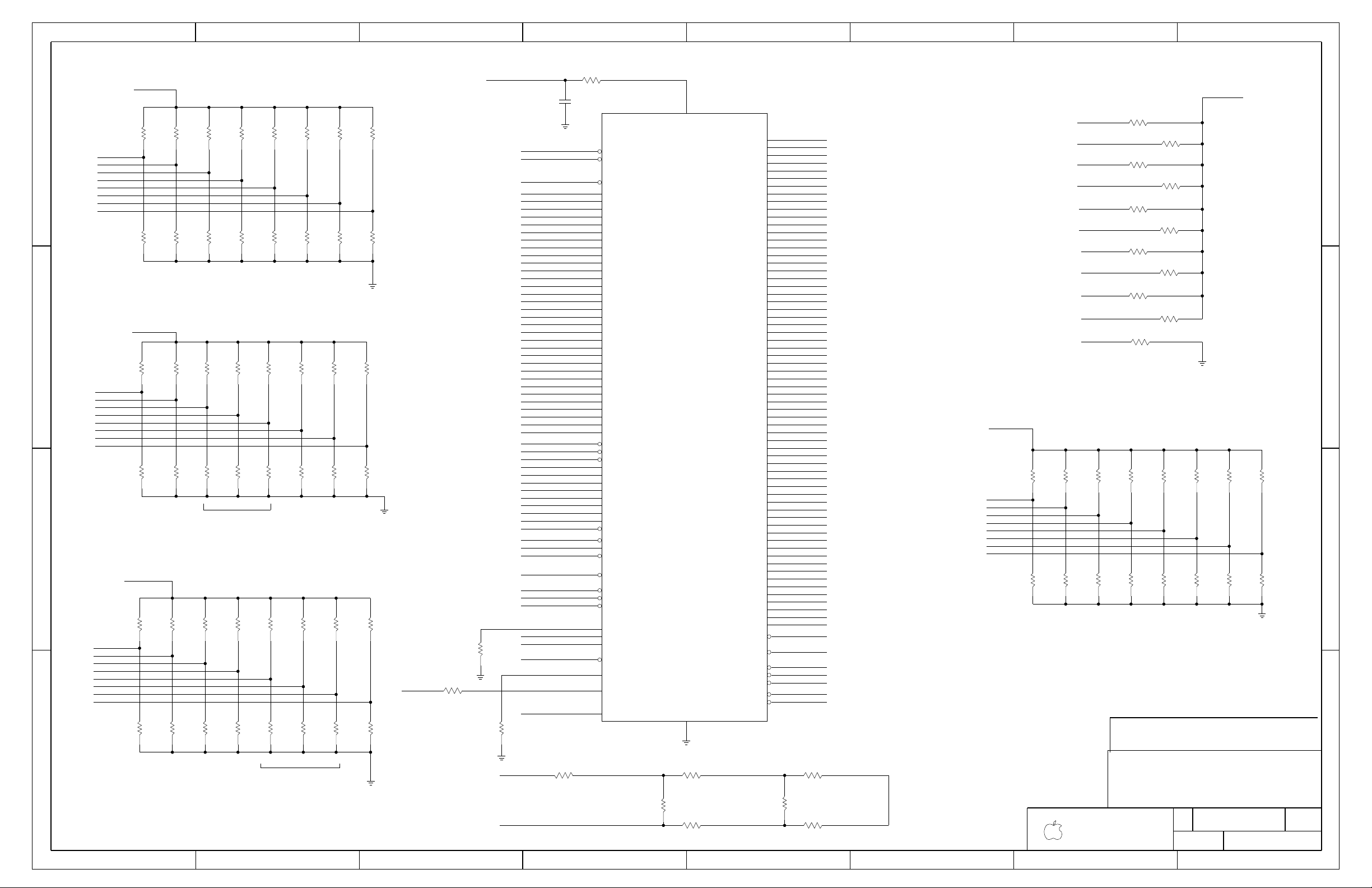

PREPREG THICKNESS: 2-3 MILS

LAYER COUNT: 12

GROUND VIAS

ASICS HEATSINK MOUNTS

BOARD INFORMATION

SEE PCB CAD FILES FOR MORE SPECIFIC INFO.

IMPEDANCE : 50 OHMS +/- 10%

1.0 OZ CU THICKNESS: 1.4 MILS

1/2 OZ CU THICKNESS: 0.7 MILS

THICKNESS : 1.2 MM / 0.047 IN

DIELECTRIC: FR-4

BOARD STACK-UP AND CONSTRUCTION

SIGNAL (1/2 OZ)

20R10 TH VIA OR VIA IN PAD

SIGNAL (1/2 OZ)

GROUND (1/2 OZ)

SIGNAL (1/3 OZ + COPPER PLATING)

SIGNAL (1/2 OZ)

GROUND (1/2 OZ)

GROUND (1/2 OZ)

CUT POWER PLANE(1 OZ)

CUT POWER PLANE(1 OZ)

PREPREG (2MIL)

PREPREG (2MIL)

LAMINATE (3MIL)

LAMINATE (4MIL)

PREPREG (3MIL)

SIGNAL (1/2 OZ)

LAMINATE (4MIL)

GROUND (1/2 OZ)

PREPREG (3MIL)

SIGNAL (1/3 OZ + COPPER PLATING)

SIGNAL TRACE WIDTH: 4 MILS

SIGNAL TRACE SPACING: 4 MILS

PCB SPECS

LAMINATE (4MIL)

1

2

PREPREG (3MIL)

LAMINATE (4MIL)

3

4

5

6

7

8

10

9

11

PREPREG (3MIL)

12

INVERTER

CHASSIS MOUNTS

BOARD HOLES

SPEAKER CLIPS

CONDUCTIVE MOUNTS

I/O AREA

255R158

OMIT

1

ZT11

HOLE-VIA-20R10

1

ZT75

HOLE-VIA-20R10

1

ZT61

HOLE-VIA-20R10

1

ZT63

HOLE-VIA-20R10

1

ZT51

HOLE-VIA-20R10

1

ZT54

HOLE-VIA-20R10

1

ZT42

HOLE-VIA-20R10

1

ZT64

HOLE-VIA-20R10

1

ZT76

HOLE-VIA-20R10

1

ZT59

HOLE-VIA-20R10

1

ZT62

HOLE-VIA-20R10

1

ZT22

HOLE-VIA-20R10

1

ZT3

HOLE-VIA-20R10

1

ZT25

HOLE-VIA-20R10

1

ZT32

HOLE-VIA-20R10

1

ZT31

HOLE-VIA-20R10

1

ZT26

HOLE-VIA-20R10

1

ZT23

HOLE-VIA-20R10

1

ZT19

HOLE-VIA-20R10

1

ZT15

HOLE-VIA-20R10

1

ZT17

HOLE-VIA-20R10

1

ZT13

HOLE-VIA-20R10

1

ZT12

HOLE-VIA-20R10

1

ZT21

HOLE-VIA-20R10

1

ZT14

HOLE-VIA-20R10

1

ZT18

HOLE-VIA-20R10

1

ZT20

235R126

OMIT

1

ZT4

OMIT

146R126

1

ZT83

OMIT

146R126

1

ZT5

OG-503040

SHLD-SM

3

2

1

SH1

CHGND1

SPKR_CLIP_P84

1

SP6

SPKR_CLIP_P84

1

SP1

SPKR_CLIP_P84

1

SP3

SPKR_CLIP_P84

1

SP5

SPKR_CLIP_P84

1

SP2

STDOFF-217ODX150IDX35H-TH

1

BS1

SPKR_CLIP_P84

1

SP4

OMIT

235R126

1

ZT6

OMIT

235R126

1

ZT16

CHGND6

CHGND2

OMIT

255R158

1

ZT10

CHGND5

HOLE-VIA-20R10

1

ZT77

HOLE-VIA-20R10

1

ZT30

HOLE-VIA-20R10

1

ZT28

HOLE-VIA-20R10

1

ZT37

HOLE-VIA-20R10

1

ZT39

HOLE-VIA-20R10

1

ZT40

HOLE-VIA-20R10

1

ZT27

HOLE-VIA-20R10

1

ZT36

HOLE-VIA-20R10

1

ZT38

OMIT

255R158

1

ZT2

HOLE-VIA-20R10

1

ZT24

HOLE-VIA-20R10

1

ZT81

HOLE-VIA-20R10

1

ZT34

HOLE-VIA-20R10

1

ZT33

HOLE-VIA-20R10

1

ZT43

HOLE-VIA-20R10

1

ZT46

HOLE-VIA-20R10

1

ZT50

HOLE-VIA-20R10

1

ZT35

HOLE-VIA-20R10

1

ZT44

HOLE-VIA-20R10

1

ZT66

HOLE-VIA-20R10

1

ZT67

HOLE-VIA-20R10

1

ZT53

HOLE-VIA-20R10

1

ZT52

HOLE-VIA-20R10

1

ZT70

HOLE-VIA-20R10

1

ZT71

HOLE-VIA-20R10

1

ZT78

HOLE-VIA-20R10

1

ZT69

HOLE-VIA-20R10

1

ZT65

HOLE-VIA-20R10

1

ZT45

HOLE-VIA-20R10

1

ZT47

HOLE-VIA-20R10

1

ZT49

HOLE-VIA-20R10

1

ZT56

HOLE-VIA-20R10

1

ZT48

HOLE-VIA-20R10

1

ZT72

HOLE-VIA-20R10

1

ZT55

HOLE-VIA-20R10

1

ZT29

HOLE-VIA-20R10

1

ZT82

HOLE-VIA-20R10

1

ZT74

HOLE-VIA-20R10

1

ZT79

HOLE-VIA-20R10

1

ZT68

HOLE-VIA-20R10

1

ZT60

HOLE-VIA-20R10

1

ZT58

HOLE-VIA-20R10

1

ZT41

HOLE-VIA-20R10

1

ZT7

HOLE-VIA-20R10

1

ZT9

HOLE-VIA-20R10

1

ZT8

HOLE-VIA-20R10

1

ZT1

HOLE-VIA-20R10

1

ZT57

HOLE-VIA-20R10

1

ZT80

HOLE-VIA-20R10

1

ZT73

44

4

051-6531

B

(1 OF 3)

TEST4

TEST3

TEST2

TEST1

TEST0

EXT_QUAL

TBEN

L2TSTCLK

L1TSTCLK

TCK

TMS

TDO

TDI

DTI0

DTI1

DTI2

DTI3

PLL_EXT

PLLCFG3

PLLCFG2

PLLCFG1

PLLCFG0

CLKOUT

SYSCLK

BVSEL

TT3

TT2

TT1

TSIZ0

TSIZ2

TSIZ1

TT4

TT0

A33

A34

A35

AP0

AP3

AP2

AP4

AP1

A25

A24

A23

A26

A27

A28

A29

A30

A31

A32

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A12

A10

A9

A8

A7

A6

A3

A4

A5

A11

A2

A0

A1

OVDD

VDD

GND

AVDD

BR*

BG*

TS*

TRST*

LSSDMODE*

TA*

TEA*

QREQ*

QACK*

CKSTP_IN*

CKSTP_OUT*

INT*

SMI*

MCP*

SRESET*

HRESET*

PMON_IN*

PMON_OUT*

BMODE0*

BMODE1*

TBST*

GBL*

WT*

CI*

AACK*

ARTRY*

SHD0*

HIT*

SHD1*

DRDY*

DBG*

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

CPU_VCORE DECOUPLING NETWORK

PLCAE SHORT CLOSE TO CENTER OF CPU

MORE 0805 10UF CAPS ON VCORE

POWER SUPPLY PAGE (PG 33)

470OHM FOR BOOT BANGER

IN FORMER L3 AREA

MPC7447

PLACE BELOW CPU

NC

MPC7447 MAXBUS

NC

NC

NC

NC

NC

NC

MPC7447 PULL-UPS

CPU_OVDD DECOUPLING NETWORK

470OHM FOR BOOT BANGER

470OHM FOR BOOT BANGER

CPU INTERNAL PLL FILTERING

10K

5%

1/16W

MF

402

21

R87

5%

1/16W

MF

402

10K

21

R139

MF

402

1/16W

5%

10K

21

R107

MF

1/16W

470

5%

402

21

R59

5%

1/16W

MF

402

10K

21

R97

MF

1/16W

5%

200

402

NO_BBANG

2

1

R85

MF

1/16W

10K

5%

402

21

R160

1K

1/16W

MF

402

5%

21

R57

1/16W

MF

402

5%

10K

21

R58

5%

10K

1/16W

MF

402

21

R129

10V

402

CERM

20%

0.1uF

2

1

C39

CERM

0.1uF

20%

10V

402

2

1

C203

10V

402

CERM

20%

0.1uF

2

1

C73

20%

CERM

402

10V

0.1uF

2

1

C74

20%

402

10V

CERM

0.1uF

2

1

C194

402

CERM

0.1uF

10V

20%

2

1

C40

20%

CERM

10V

402

0.1uF

2

1

C191

CERM

20%

10V

402

0.1uF

2

1

C152

0.1uF

10V

CERM

20%

402

2

1

C138

0.1uF

402

CERM

10V

20%

2

1

C113

0.1uF

402

10V

CERM

20%

2

1

C104

402

20%

10V

CERM

0.1uF

2

1

C115

20%

CERM

402

10V

0.1uF

2

1

C38

0.1uF

20%

CERM

10V

402

2

1

C224

0.1uF

20%

CERM

402

10V

2

1

C48

0.1uF

20%

10V

402

CERM

2

1

C90

10V

402

CERM

20%

0.1uF

2

1

C72

CERM

20%

10V

402

0.1uF

2

1

C107

1/16W

5%

MF

402

470

2

1

R206

20%

CERM

10V

402

0.1uF

2

1

C114

10V

CERM

402

20%

0.1uF

2

1

C154

10V

20%

CERM

402

0.1uF

2

1

C91

CERM

0.1uF

20%

10V

402

2

1

C168

402

10V

CERM

20%

0.1uF

2

1

C223

CERM

0.1uF

402

10V

20%

2

1

C112

402

MF

1/16W

5%

470

2

1

R241

5%

1/16W

MF

402

10K

21

R60

5%

1/16W

MF

402

470

21

R61

5%

402

1/16W

MF

10K

21

R148

5%

402

MF

1/16W

1K

21

R98

10uF

20%

6.3V

CERM

805

C25

6.3V

20%

CERM

805

10uF

2

1

C346

CERM

20%

6.3V

10uF

805

C342

20%

805

6.3V

CERM

10uF

2

1

C8

402

MF

5%

1/16W

10K

21

R120

402

MF

5%

10K

1/16W

21

R109

1/16W

MF

402

402

1%

1

2

R106

805

10V

20%

2.2uF

CERM

2

1

C340

10V

805

CERM

20%

2.2uF

2

1

C12

1/16W

MF

402

10K

5%

21

R73

MF

402

5%

1/16W

10K

21

R72

1/16W

1_5V_MAXBUS

603

MF

5%

0

21

R702

1_8V_MAXBUS

MF

5%

0

603

1/16W

21

R693

+1_5V_SLEEP

+1_8V_SLEEP

402

5%

470

1/16W

MF

BBANG

2

1

R86

470

402

MF

1/16W

5%

21

R128

BGA

APOLLO_MPC7445_360

800MHZ

OMIT

D3

K10

K8

J13

J11

J9

J7

H12

H10

M12

M10

M8

L13

L11

L9

L7

K14

K12

H8

C5

E9

F6

E6

E5

E7

F7

G6

L4

A5

F1

D10

E10

B10

B6

A12

L1

A4

B9

C6

F11

E1

K6

A10

A2

F9

H5

E4

P4

G5

A9

D9

A7

D7

C7

C8

B8

J5

H3

G18

F2

E18

D5

C12

V14

V10

V7

V4

U16

U12

U2

T9

T6

C2

R16

R13

R4

P11

P8

P2

N6

M3

L5

K2

B4

C9

E8

B3

G8

D4

D8

B2

H7

H4

G17

F3

E17

V15

V11

V8

V5

U17

U13

U3

D13

T10

T7

R17

R14

R5

P12

P9

P3

N7

M13

D6

M11

M9

M7

M4

L12

L10

L8

L6

K13

K11

C3

K9

K3

K7

J12

J10

J8

J6

H13

H11

H9

B5

E2

A11

N1

P1

K1

G1

R3

M2

H2

B1

A3

J1

B7D2

F8

G9

M1

A8

N2

G7

F5

H6

E3

C1

R1

G2

C10

D1

D11

L2

F10

B11

G10

C4

B12

W1

N5

G3

U1

V2

T1

N3

P5

M5

J3

N4

K4

J2

C11

W2

K5

R2

J4

V1

F4

T2

G4

L3

D12

H1

E11

U43

402

10V

CERM

20%

0.1uF

2

1

C103

402

20%

CERM

10V

0.1uF

2

1

C149

0.1uF

10V

402

CERM

20%

2

1

C151

0.1uF

10V

CERM

20%

402

2

1

C202

402

10V

CERM

20%

0.1uF

2

1

C111

10V

402

CERM

20%

0.1uF

2

1

C110

0.1uF

10V

402

CERM

20%

2

1

C275

10V

20%

402

0.1uF

CERM

2

1

C257

0.1uF

402

CERM

20%

10V

2

1

C273

0.1uF

20%

CERM

402

10V

2

1

C41

10V

CERM

402

0.1uF

20%

2

1

C272

10V

CERM

402

20%

0.1uF

2

1

C46

10K

5%

1/16W

MF

402

21

R65

5%

1/16W

MF

402

10K

21

R130

5%

1/16W

MF

402

10K

21

R79

5%

MF

10K

402

1/16W

21

R108

402

10V

CERM

20%

0.1uF

2

1

C190

402

10V

CERM

20%

0.1uF

2

1

C150

20%

0.1uF

402

10V

CERM

2

1

C201

402

0.1uF

10V

CERM

20%

2

1

C193

CERM

0.1uF

402

10V

20%

2

1

C153

20%

CERM

10uF

6.3V

805

2

1

C344

20%

CERM

10V

402

0.1uF

2

1

C189

402

CERM

20%

0.1uF

10V

2

1

C105

10V

402

20%

0.1uF

CERM

2

1

C192

0.1UF

20%

10V

CERM

402

2

1

C47

0.1UF

20%

10V

CERM

402

2

1

C188

0.1UF

20%

10V

CERM

402

2

1

C169

0.1UF

20%

10V

CERM

402

2

1

C170

0.1UF

20%

10V

CERM

402

2

1

C155

0.1UF

20%

10V

CERM

402

2

1

C139

0.1UF

20%

10V

CERM

402

2

1

C92

0.1UF

20%

10V

CERM

402

2

1

C106

10UF

805

CERM

6.3V

20%

2

1

C195

805

CERM

6.3V

20%

10UF

2

1

C347

10UF

20%

6.3V

CERM

805

2

1

C258

805

CERM

6.3V

20%

10UF

2

1

C345

805

CERM

6.3V

20%

10UF

2

1

C156

805

6.3V

20%

10UF

CERM

2

1

C341

10UF

20%

805

CERM

6.3V

2

1

C225

805

CERM

6.3V

20%

10UF

2

1

C343

SM

OMIT

21

XW31

402

10V

20%

CERM

0.1uF

2

1

C137

805

CERM

10V

2.2uF

20%

2

1

C136

B

051-6531

5

44

IC,APOLLO7,1.X,1.3GHZ,1.XV CORE,85C

U43

1

337S2733 CRITICAL 1_30_VCORE

1_32_VCORE337S2807

1

IC,APOLLO7,1.X,1.33GHZ,1.32V VCORE,85C

U43

CRITICAL

CPU_ADDR<0>

CPU_AVDD

MAXBUS_SLEEP

CPU_CLKOUT_SPN

JTAG_CPU_TRST_L

CPU_QREQ_L

JTAG_CPU_TCK

CPU_DTI<2>

CPU_ADDR<9>

JTAG_CPU_TCK

CPU_L1TSTCLK

MPIC_CPU_INT_L

JTAG_CPU_TDI

JTAG_CPU_TMS

CPU_SMI_L

CPU_HRESET_L

CPU_SRWX_L

CPU_L2TSTCLK

CPU_PULLDOWN

CPU_EDTI

CPU_PULLUP

CPU_PMONIN_L

CPU_CHKSTP_OUT_L

CPU_LSSD_MODE

CPU_SHD0_L

CPU_TBEN

CPU_SHD1_L

CPU_CHKS_L

CPU_VCORE_SLEEP

CPU_TEA_L

CPU_BR_L

CPU_BUS_VSEL

SYSCLK_CPU

CPU_PULLUP

CPU_CHKS_L

CPU_EMODE1_L

CPU_EMODE0_L

CPU_PMONIN_L

CPU_CHKSTP_OUT_L

MPIC_CPU_INT_L

CPU_MCP_L

CPU_SMI_L

CPU_HRESET_L

CPU_SRESET_L

CPU_TBEN

JTAG_CPU_TDI

JTAG_CPU_TDO_TP

JTAG_CPU_TRST_L

JTAG_CPU_TMS

CPU_L1TSTCLK

CPU_LSSD_MODE

CPU_L2TSTCLK

CPU_TA_L

CPU_PLL_CFG<3>

CPU_DBG_L

CPU_DTI<1>

CPU_DTI<0>

CPU_PLL_CFG<0>

MAXBUS_SLEEP

CPU_HIT_L

CPU_SHD1_L

CPU_SHD0_L

CPU_ARTRY_L

CPU_CI_L

CPU_WT_L

CPU_AACK_L

CPU_TSIZ<2>

CPU_GBL_L

CPU_TBST_L

CPU_TSIZ<0>

CPU_TT<2>

CPU_TT<3>

CPU_TT<4>

CPU_TT<1>

CPU_ADDR<31>

CPU_ADDR<30>

CPU_ADDR<29>

CPU_ADDR<28>

CPU_ADDR<26>

CPU_ADDR<27>

CPU_ADDR<24>

CPU_ADDR<23>

CPU_ADDR<25>

CPU_ADDR<21>

CPU_ADDR<22>

CPU_ADDR<18>

CPU_ADDR<19>

CPU_ADDR<20>

CPU_ADDR<16>

CPU_ADDR<17>

CPU_ADDR<13>

CPU_ADDR<14>

CPU_ADDR<15>

CPU_ADDR<12>

CPU_ADDR<8>

CPU_ADDR<10>

CPU_ADDR<7>

CPU_ADDR<4>

CPU_ADDR<3>

CPU_ADDR<2>

CPU_TS_L

CPU_BG_L

CPU_TT<0>

CPU_SRWX_L

CPU_PULLDOWN

CPU_PULLDOWN

CPU_EDTI

CPU_DRDY_L

CPU_PULLDOWN

CPU_TSIZ<1>

MAXBUS_SLEEP

CPU_EMODE1_L

CPU_MCP_L

CPU_SRESET_L

CPU_ADDR<6>

CPU_ADDR<5>

CPU_ADDR<11>

CPU_QACK_L

CPU_ADDR<1>

ADT7460_VCORE_MON

CPU_VCORE_SLEEP

CPU_PLL_CFG<4>

CPU_PLL_CFG<2>

CPU_PLL_CFG<1>

38

38

38

34

34

34

23

23

23

16

16

16

15

39

39

39

15

15

39

8

39

39

39

39

39

23

38

23

39

39

39

8

8

38

36

7

23

36

23

36

36

23

14

23

23

30

7

39

8

34

36

36

36

39

14

30

7

39

8

23

23

23

36

36

36

36

7

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

7

39

36

36

36

36

36

34

8

38

5

5

8

5

8

8

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

8

8 7

8

5

5

5

7

5

5

5

5

5

5

5

5

5

39

5

5

5

5

5

8

7

8

8

8

7

5

8

5

5

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

5

5

5

5

8

5

8

5

5

5

5

8

8

8

8

8

25

5

7

7

7

(2 OF 3)

D0

D60

D61

D62

D63

DP7

DP0

DP1

DP2

DP3

DP4

DP5

DP6

D59

D56

D57

D58

D55

D54

D53

D52

D50

D51

D49

D46

D45

D47

D48

D44

D43

D42

D41

D40

D39

D38

D37

D36

D35

D34

D33

D30

D31

D32

D29

D26

D25

D24

D23

D27

D28

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D1

D2

D3

(3 OF 3)

NC_B14

NC_B13

NC_E12

NC_B18

NC_N19

NC_K17

NC_N18

NC_N12

NC_A6

NC_C13

NC_G11

NC_A14

NC_F12

NC_A13

NC_A18

NC_C14

NC_A15

NC_B16

NC_E13

NC_F13

NC_F14

NC_G12

NC_A17

NC_C15

NC_G14

NC_H14

NC_E14

NC_G13

NC_C16

NC_C17

NC_B17

NC_B15

NC_E15

NC_D14

NC_A19

NC_B19

NC_A16

NC_C18

NC_G15

NC_D15

NC_C19

NC_K16

NC_J17

NC_K18

NC_L18

NC_L19

NC_M18

NC_P16

NC_L16

NC_H15

NC_J16

NC_K19

NC_J15

NC_J19

NC_J18

NC_J14

NC_K15

NC_L14

NC_L17

NC_M15

NC_N17

NC_P19

NC_M16

NC_M19

NC_N16

NC_N13

NC_M17

NC_M14

NC_N14

NC_P18

NC_N15

NC_D19

NC_F15

NC_G19

NC_E16

NC_D17

NC_D16

NC_P15

NC_L15

NC_H19

NC_H18

NC_H17

NC_H16

NC_E19

NC_D18

NC_F16

NC_G16

NC_F19

NC_F17

NC_F18

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

MPC7447/BBANG

NC

BOOT BANGER - LMU PERORMS THIS FUNCTION IF NEEDED

SEE PAGE 22

APOLLO_MPC7445_360

BGA

800MHZ

OMIT

W6

N8

V3

M6

W9

T4

W4

T3

W13

V13

P14

T8

W8

R8

P6

U15

R7

U7

U8

U4

V17

W3

T17

T18

T16

W18

T15

W17

U18

W19

U19

T19

V19

R18

V18

R19

P17

W16

V6

P7

R6

W7

U5

T5

U6

W5

V9

U9

V16

W10

R9

U10

P10

N9

R10

T11

W11

U11

R11

T14

N10

N11

V12

W12

T12

R12

W14

U14

P13

T13

W15

R15

U43

OMIT

BGA

800MHZ

APOLLO_MPC7445_360

P19

P18

P16

P15

N19

N18

N17

N16

N15

N14

N13

N12

M19

M18

M17

M16

M15

M14

L19

L18

L17

L16

L15

L14

K19

K18

K17

K16

K15

J19

J18

J17

J16

J15

J14

H19

H18

H17

H16

H15

H14

G19

G16

G15

G14

G13

G12

G11

F19

F18

F17

F16

F15

F14

F13

F12

E19

E16

E15

E14

E13

E12

D19

D18

D17

D16

D15

D14

C19

C18

C17

C16

C15

C14

C13

B19

B18

B17

B16

B15

B14

B13

A6

A19

A18

A17

A16

A15

A14

A13

U43

6

44

051-6531

B

CPU_DATA<18>

CPU_DATA<0>

CPU_DATA<2>

CPU_DATA<1>

CPU_DATA<3>

CPU_DATA<5>

CPU_DATA<4>

CPU_DATA<6>

CPU_DATA<7>

CPU_DATA<8>

CPU_DATA<10>

CPU_DATA<9>

CPU_DATA<12>

CPU_DATA<11>

CPU_DATA<13>

CPU_DATA<15>

CPU_DATA<14>

CPU_DATA<17>

CPU_DATA<16>

CPU_DATA<19>

CPU_DATA<20>

CPU_DATA<21>

CPU_DATA<22>

CPU_DATA<23>

CPU_DATA<24>

CPU_DATA<25>

CPU_DATA<26>

CPU_DATA<27>

CPU_DATA<28>

CPU_DATA<29>

CPU_DATA<30>

CPU_DATA<31>

CPU_DATA<33>

CPU_DATA<32>

CPU_DATA<34>

CPU_DATA<35>

CPU_DATA<36>

CPU_DATA<37>

CPU_DATA<38>

CPU_DATA<39>

CPU_DATA<40>

CPU_DATA<41>

CPU_DATA<42>

CPU_DATA<43>

CPU_DATA<44>

CPU_DATA<46>

CPU_DATA<45>

CPU_DATA<47>

CPU_DATA<48>

CPU_DATA<49>

CPU_DATA<51>

CPU_DATA<50>

CPU_DATA<52>

CPU_DATA<53>

CPU_DATA<54>

CPU_DATA<56>

CPU_DATA<55>

CPU_DATA<57>

CPU_DATA<58>

CPU_DATA<59>

CPU_DATA<61>

CPU_DATA<60>

CPU_DATA<62>

CPU_DATA<63>

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

G

D

S

G

D

S

04

G

D

S

G

D

S

S

D

G

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

R01D

TRANSISTOR ON CPU_PLL_CFG<4> IS MET.

PLL DISABLE 1 X

STATE ENCODING CPU_PLL_STOP_OC CPU_VCORE_HI_OC

R01B R00C

1417

1167

1083

1000

9.0X

11.0X

1500

R10B

MAXBUS VSEL

1.5V INTERFACE

BUSTYPE SELECT

APOLLO ONLY SUPPORTS MAXBUS

(PROCESSOR)

CPU_BUS_VSEL

SIGNAL

(PROCESSOR)

CPU_EMODE0_L

CPU_HRESET_L

CPU_HRESET_INV

CPU_HRESET_L

TIED

HIGH

LOW

1.8V INTERFACE

1.5V INTERFACE

2.5V INTERFACE

60X BUS MODE

APPLICATION

MAX BUS MODE

DESKTOP HAD PROBLEM USING

1.8V INTERFACE

933

267

400

533

867

800

733

667

0 1011 0B

0 1001 09

5.0X

5.5X

333

500

667

9.5X

8.0X

7.5X

7.0X

6.5X

6.0X

4.0X

3.0X

2.0X

1.0X

0.0X

APOLLO 7

PULLUP TO ENSURE THAT Vgs OF PASS

R10E R00ER10A R00D

LOW SPEED 0 0

R10D R01E

CPU FREQUENCY CONFIGURATION

(MHZ)

PLL OFF

133MHZ

(Bus-to-Core)

MULTIPLIER

0 1111 0F

CPU_PLL_CFG

(AT BUS FREQUENCY)

CORE FREQUENCY

167MHZ

PLL BYPASS 0 0011 03

0 0100 04

0 1000 08

0 1010 0A

0 1101 0D

0 0101 05

0 0010 02

0 1100 0C

0 0001 01

1000

1067

1 0110 16

32004000

3733466728.0X

24.0X

1 1010 1A

0 0000 00

1 1000 18

1 1001 19

1833

1667

1750

1917

1467

1333

1400

1533

1 1100 1C

1 0001 11

1 1101 1D

1 0101 15

0 1110 0E

1 0000 10

1 0010 12

1 0011 13

1 1011 1B

1 1111 1F

1 0100 14

1667

1600

2667

2400

2267

1800

1733

2133

2000

18672333

2500

2667

2083

2000

3333

3000

2833

2250

2167

3500 2800

16.0X

15.0X

14.0X

10.0X

10.5X

12.0X

11.5X

12.5X

13.0X

13.5X

17.0X

18.0X

20.0X

21.0X

1 0111 17

1200

1133

0 0110 06

1583 1267

0 0111 07

1 1110 1E

CPU CONFIGURATION

4 0123

E ABCD HEX

R10E, R01E, OR PULLUP STUFFED

STUFF PASS TRANSISTOR ONLY IF

HIGH SPEED 0 1

CPU PLL CONFIG CIRCUITRY

R00B R10C

INVERTED HRESET_L

R00A R01C

NEED TO CHARACTERIZE

INVERTER TO INVERT HRESET_L

CPU CONFIGURATION

1250

1333

833

917

8.5X

+5V_SLEEP NOW REQUIRED FOR PLL_STOP_L

R01A

NO STUFF

0

MF

402

5%

1/16W

2

1

R23

NO STUFF

5%

402

MF

1/16W

0

2

1

R16

1/16W

10K

5%

MF

402

2

1

R9

1/16W

10K

402

MF

5%

2

1

R10

10K

1/16W

5%

MF

402

2

1

R11

402

10K

MF

1/16W

5%

2

1

R12

402

5%

1/16W

MF

47K

2

1

R3

1/16W

402

10K

5%

MF

2

1

R48

402

82K

MF

1/16W

5%

2

1

R33

0

5%

1/16W

MF

402

NO STUFF

2

1

R18

5%

0

1/16W

MF

402

NO STUFF

2

1

R17

10K

5%

1/16W

MF

402

NO STUFF

2

1

R2

2N7002DW

SOT-363

4

5

3

Q2

2N7002DW

SOT-363

1

2

6

Q2

SC70-5

SN74AUC1G04

1_5V_MAXBUS

CRITICAL

4

5

3

2

U1

402

MF

1/16W

5%

0

2

1

R27

2N7002DW

NO STUFF

SOT-363

1

2

6

Q1

2N7002DW

NO STUFF

SOT-363

4

5

3

Q1

+5V_SLEEP

1/16W

MF

5%

22

402

1_5V_MAXBUS

1 2

R4

22

1/16W

MF

5%

402

1 2

R149

10

MF

5%

1/16W

402

1_8V_MAXBUS

2

1

R5

2N7002

SM

2

1

3

Q3

SM

2N3904

2

3

1

Q4

249K

402

MF

1/16W

1%

21

R47

NO STUFF

5%

1/16W

MF

402

0

2

1

R19

+3V_SLEEP

1/16W

NO STUFF

402

MF

5%

0

2

1

R20

MF

402

5%

0

NO STUFF

1/16W

2

1

R21

1/16W

NO STUFF

402

MF

5%

0

2

1

R22

MF

1/16W

0

402

5%

2

1

R24

1/16W

MF

5%

402

0

2

1

R25

0

5%

1/16W

MF

402

NO STUFF

2

1

R26

402

MF

5%

0

1/16W

2

1

R14

402

5%

NO STUFF

0

MF

1/16W

2

1

R13

NO STUFF

402

MF

1/16W

5%

0

2

1

R15

44

7

051-6531

B

CPU_PLL_CFG<0>

CPU_PLL_CFG<1>

CPU_PLL_FS10

CPU_PLL_FS00

MAXBUS_SLEEP

CPU_VCORE_HI_OC

CPU_PLL_FS01

CPU_PLL_CFG<2>

CPU_PLL_CFG<3>

CPU_PLL_STOP_BASE

CPU_PLL_CFGEXT CPU_PLL_CFG<4>

CPU_PLL_STOP_OC

PLL_STOP_L

CPU_PLL_STOP_OC

CPU_BUS_VSEL

MAXBUS_SLEEP

CPU_HRESET_INV

CPU_HRESET_L

CPU_HRESET_L CPU_EMODE0_L

PLL_STOP_L

38

38

34

34

23

23

16

16

15

15

39

39

8

8

23

23

7

34

30

30

7

7

7

5

5

5

30

5

5

5

7

7

7

5

5

5

5 5

7

(PLL6)

VSSA_7

(PLL6)

VDD15A_7

D_42

D_41

D_40

D_39

D_38

D_44

D_43

D_45

D_46

D_47

D_48

D_52

D_51

D_50

D_49

D_53

D_55

D_54

D_56

D_57

D_58

D_60

D_59

D_62

D_61

D_63

DBG

DRDY

DTI_0

TEA

TA

DTI_2

DTI_1

D_1

D_0

D_2

D_6

D_5

D_4

D_3

D_7

D_11

D_10

D_9

D_8

D_12

D_14

D_13

D_15

D_16

D_17

D_22

D_21

D_20

D_19

D_18

D_23

D_24

D_25

D_26

D_27

D_32

D_31

D_30

D_29

D_28

D_34

D_33

D_35

D_36

D_37

BR

(1 OF 9)

MAXBUS

INTERFACE

TS

BG

A_0

A_1

A_2

A_3

A_4

A_5

A_9

A_6

A_7

A_8

A_10

A_14

A_13

A_12

A_11

A_20

A_16

A_17

A_18

A_19

A_15

A_27

A_22

A_21

A_30

A_29

A_28

A_26

A_25

A_24

A_23

TT_2

TT_1

TT_0

A_31

TBST

TSIZ_0

TSIZ_1

TSIZ_2

CI

GBL

TT_4

AACK

QREQ

ARTRY

TT_3

WT

HIT

ANALYZER_CLK

SUSPENDACK

SUSPENDREQ

QACK

STOPCPUCLK

CPU_FB_OUT

CPU_FB_IN

CPU_CLK

TBEN

ACS_REF

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

DDR_TPDModeEnable_h

0: TDI input (JTAG)

1: TDI output

Spare

Spare

Spare

Spare

MODE C (2.0X) IS FOR CLOCK SLEW OPERATION

FB BUFFER HAS 50 OHM OUTPUT IMPEDANCE

MAXBUS PULL-UPS

0: Legacy interface

1: B-mode interface

FireWire PHY interface

PCI1_REQ1_L / PCI1_GNT1_L

PCI1_REQ2_L / PCI1_GNT2_L

PCI1_REQ0_L / PCI1_GNT0_L

Spare

1: GPIOs

0: REQ/GNT

1: GPIOs

0: REQ/GNT

1: GPIOs

0: REQ/GNT

Processor Bus Mode

1: 60x bus (G3)

0: Max Bus (G4)

BIT 56 TO 63

INTREPID BOOT STRAPS

LONG = 1" LONGER THAN MATCHED LENGTH

SHORT = 1" SHORTER THAN MATCHED LENGTH

NO BUS KEEPER - ?

NO BUS KEEPER - ?

NO BUS KEEPER - ?

NO BUS KEEPER - ?

INPUT - PU

INPUT - PD

NO BUS KEEPER - PU

NO BUS KEEPER - PU

NO BUS KEEPER - PU

INPUT - PU

NO BUS KEEPER - PU

NO BUS KEEPER

NO BUS KEEPER

Vout = MaxBus rail (1.8V)

Vin = Intrepid Vcore (1.5V)

BIT2 BIT1 BIT0

BIT0BIT2

001: 50 ohm

101: 40 ohm

010: 100 ohm

100: 200 ohm

000: 200 ohm

110: 66.6 ohm

011: 33.3 ohm

111: 28.6 ohm

MaxBus output impedance

PLL4MODESEL_NXT[2:0]

1: External source

SelPLL4ExtSrc

1: Active

INTREPID OUTPUTS HIGH BY DEFAULT

BUF_REF_CLK_OUTEnable_h

1: Active

0: Normal 1394b

1: TI PHY workaround

TI 1394b workaround

Spare

Spare

0: Inactive

AnalyzerClk_En_h

0: Inactive

DDR_TPDEn_Pol

1: Active low

0: Active high

0: Active high

ExtPLL_SDwn_Pol

Spare

BIT 32 TO 39

Spare

NO BUS KEEPER - PU

Intrepid MaxBus

1/ D47 - SELAGPSPREADCLK - SLEEP/WAKE CYCLE REQUIRED

2/ D46 - SELPCI1SPREADCLK - SLEEP/WAKE CYCLE REQUIRED

3/ D44 - PLL4MODESEL_NXT<0> - SLEEP/WAKE CYCLE REQUIRED

4/ D43 - PLL4MODESEL_NXT<1> - SLEEP/WAKE CYCLE REQUIRED

5/ D42 - PLL4MODESEL_NXT<2> - SLEEP/WAKE CYCLE REQUIRED

6/ D33 - ANALYZERCLK_EN_H - IMMEDIATE EFFECT

THE FOLLOWING STRAP BITS CAN BE

CHANGED BY SOFTWARE:

IF A STRAP IS NOT LISTED, THEN

IT CANNOT BE CHANGED BY SOFTWARE

INPUT

NO BUS KEEPER - PU

0: PLL5 (NO SPREAD)

1: PLL4

001: 149.76MHZ

000: 166.4MHZ (2.5X)

BIT1

0: PLL5 (NO SPREAD)

PCI0 Source Clock

010: 133.12MHZ (2.0X)

011: 99.84MHZ (1.5X)

100: 83.20MHZ

MODE A (2.5X) IS FOR STATIC OPERATION

INTREPID BOOT STRAPS

1: Active

Spare

Spare

1: Active low

0: Inactive

0: PLL5

BIT 48 TO 55

InternalSpreadEn

BIT 40 TO 47

1: PLL4

PCI1 Source Clock

402

MF

1/16W

1%

1K

2

1

R137

402

CERM

6.3V

20%

0.22UF

2

1

C308

4.7

5%

1/16W

MF

402

21

R227

0

402

MF

1/16W

5%

21

R144

10K

5%

1/16W

SM1

72

RP24

0

402

MF

1/16W

5%

2 1

R167

MF

1/16W

1%

402

511

2

1

R197

NO STUFF

5%

1/16W

MF

402

10K

2

1

R178

10K

402

MF

1/16W

5%

NO STUFF

2

1

R179

NO STUFF

10K

402

MF

1/16W

5%

2

1

R651

NO STUFF

5%

1/16W

MF

402

10K

2

1

R166

10K

402

MF

1/16W

5%

NO STUFF

2

1

R153

NO STUFF

5%

1/16W

MF

402

10K

2

1

R123

NO STUFF

10K

402

MF

1/16W

5%

2

1

R135

5%

1/16W

MF

402

10K

2

1

R674

10K

402

MF

1/16W

5%

2

1

R143

5%

MF

402

1/16W

10K

2

1

R673

5%

1/16W

MF

402

10K

2

1

R664

10K

402

MF

5%

1/16W

2

1

R657

5%

402

10K

MF

1/16W

2

1

R639

10K

402

MF

5%

1/16W

2

1

R643

10K

402

MF

1/16W

5%

NO STUFF

2

1

R642

10K

402

MF

5%

1/16W

2

1

R136

MF

402

1/16W

5%

10K

NO_SSCG

2

1

R165

NO_SSCG

10K

402

1/16W

5%

MF

2

1

R177

402

MF

1/16W

5%

NO_SSCG

10K

2

1

R152

5%

1/16W

MF

402

NO STUFF

10K

2

1

R184

402

MF

1/16W

5%

10K

SSCG

2

1

R134

NO STUFF

10K

402

MF

1/16W

5%

2

1

R164

10K

402

MF

1/16W

5%

NO STUFF

2

1

R142

10K

402

MF

1/16W

5%

NO STUFF

2

1

R122

5%

MF

402

10K

SSCG

1/16W

2

1

R666

MF

5%

10K

1/16W

SSCG

402

2

1

R658

SSCG

10K

402

MF

1/16W

5%

2

1

R675

5%

MF

402

10K

1/16W

2

1

R683

402

MF

1/16W

5%

10K

NO_SSCG

2

1

R644

5%

1/16W

MF

402

10K

2

1

R665

10K

402

MF

1/16W

5%

2

1

R652

10K

402

MF

1/16W

5%

2

1

R640

10K

402

MF

1/16W

5%

NO STUFF

2

1

R176

5%

1/16W

MF

402

10K

NO STUFF

2

1

R141

10K

402

MF

1/16W

5%

2

1

R183

10K

402

MF

1/16W

5%

NO STUFF

2

1

R162

5%

1/16W

MF

402

10K

NO STUFF

2

1

R151

10K

402

MF

1/16W

5%

2

1

R163

5%

1/16W

MF

402

10K

SSCG

2

1

R121

10K

402

MF

1/16W

5%

2

1

R676

NO STUFF

5%

1/16W

MF

402

10K

2

1

R684

5%

1/16W

MF

402

10K

2

1

R653

10K

402

MF

1/16W

5%

2

1

R667

5%

1/16W

MF

402

10K

2

1

R659

402

MF

1/16W

5%

NO STUFF

10K

2

1

R668

NO_SSCG

5%

MF

402

10K

1/16W

2

1

R641

10K

402

MF

1/16W

5%

SSCG

2

1

R133

MF

1/16W

NO_SSCG

10K

5%

402

2

1

R645

5%

1/16W

MF

402

10K

NO STUFF

2

1

R182

10K

402

MF

1/16W

5%

2

1

R174

5%

1/16W

MF

402

10K

NO STUFF

2

1

R150

10K

402

MF

1/16W

5%

NO STUFF

2

1

R131

5%

1/16W

MF

402

10K

NO STUFF

2

1

R132

NO STUFF

10K

402

MF

1/16W

5%

2

1

R175

NO STUFF

10K

402

MF

1/16W

5%

2

1

R161

5%

1/16W

MF

402

10K

NO STUFF

2

1

R140

10K

402

MF

1/16W

5%

2

1

R685

10K

402

MF

1/16W

5%

2

1

R660

NO STUFF

5%

1/16W

MF

402

10K

2

1

R678

5%

1/16W

MF

402

10K

2

1

R647

10K

402

MF

1/16W

5%

2

1

R646

5%

1/16W

MF

402

10K

2

1

R677

10K

402

MF

1/16W

5%

2

1

R669

5%

1/16W

MF

402

10K

2

1

R654

INTREPID-REV2.1

BGA

CRITICAL

D28

H25

H26

J25

D27

B28

G25

E25

D26

H24

G24

B27

E28

A28

A31

E27

AK9

AM8

AH9

A32

G27

B31

A29

D11

E12

A8

G20

B20

G19

E19

A9

D19

A20

J19

B19

H19

A19

A18

D18

B18

E18

B8

B17

A17

G18

D17

H18

J18

A16

E17

B16

A15

B9

H17

B15

G17

E16

D16

A13

A14

D15

J16

E15

H11

G16

A12

B14

D14

H15

B13

G15

B12

E14

H14

E11

G14

A11

D13

B11

G13

E13

D12

A10

J13

B10

G12

D10

B30

D29

K25

G28

A30H16

J24

J15

G26

E29

E26

E23

A25

D23

A26

B26

G23

A21

D20

E24

B21

E20

A22

H21

B22

H20

A23

D21

A24

E21

A27

G21

J21

E22

B23

B24

D22

G22

H22

B25

J22

D25

D24

H23

G8

H13

B29

U45

402

MF

1/16W

5%

0

NO STUFF

2

1

R225

0

5%

1/16W

MF

402

21

R215

402

MF

1/16W

5%

0

2

1

R208

NO STUFF

0

5%

1/16W

MF

402

21

R207

402

MF

1/16W

5%

0

21

R226

NO STUFF

402

MF

1/16W

5%

0

21

R196

1/16W

5%

10K

SM1

63

RP24

10K

5%

1/16W

SM1

81

RP23

SM1

1/16W

5%

10K

54

RP23

SM1

10K

5%

1/16W

72

RP23

1/16W

5%

10K

SM1

72

RP21

SM1

10K

5%

1/16W

81

RP21

SM1

10K

1/16W

5%

63

RP21

10K

5%

1/16W

SM1

54

RP21

1/16W

5%

10K

SM1

54

RP24

SM1

10K

1/16W

5%

63

RP23

B

051-6531

448

CPU_DATA<43>

CPU_ADDR<26>

CPU_ADDR<27>

CPU_DATA<47>

CPU_DATA<45>

CPU_DATA<46>

MAXBUS_SLEEP

CPU_DATA<54>

CPU_DATA<52>

MAXBUS_SLEEP

CPU_CI_L

CPU_ADDR<31>

CPU_ADDR<29>

CPU_DATA<38>

CPU_DATA<42>

CPU_DATA<44>

CPU_GBL_L

+1_5V_INTREPID_PLL7

INTREPID_ACS_REF

CPU_TBEN

CPU_CLK_EN

SYSCLK_LA_TP

INT_CPUFB_OUT

INT_SUSPEND_ACK_L

INT_SUSPEND_REQ_L

CPU_QACK_L

CPU_QREQ_L

CPU_ARTRY_L

CPU_HIT_L

CPU_AACK_L

CPU_WT_L

CPU_TT<3>

CPU_TT<4>

CPU_TT<2>

CPU_TT<0>

CPU_TT<1>

CPU_TSIZ<1>

CPU_TSIZ<2>

CPU_TSIZ<0>

CPU_TBST_L

CPU_ADDR<30>

CPU_ADDR<28>

CPU_ADDR<25>

CPU_ADDR<23>

CPU_ADDR<24>

CPU_ADDR<21>

CPU_ADDR<22>

CPU_ADDR<20>

CPU_ADDR<18>

CPU_ADDR<19>

CPU_ADDR<17>

CPU_ADDR<16>

CPU_ADDR<15>

CPU_ADDR<13>

CPU_ADDR<14>

CPU_ADDR<11>

CPU_ADDR<12>

CPU_ADDR<10>

CPU_ADDR<9>

CPU_ADDR<8>

CPU_ADDR<7>

CPU_ADDR<6>

CPU_ADDR<5>

CPU_ADDR<4>

CPU_ADDR<3>

CPU_ADDR<2>

CPU_ADDR<0>

CPU_ADDR<1>

CPU_TS_L

CPU_BG_L

CPU_BR_L

CPU_DATA<1>

CPU_DATA<0>

CPU_DATA<3>

CPU_DATA<4>

CPU_DATA<2>

CPU_DATA<5>

CPU_DATA<6>

CPU_DATA<8>

CPU_DATA<9>

CPU_DATA<7>

CPU_DATA<10>

CPU_DATA<11>

CPU_DATA<13>

CPU_DATA<12>

CPU_DATA<14>

CPU_DATA<15>

CPU_DATA<16>

CPU_DATA<18>

CPU_DATA<17>

CPU_DATA<19>

CPU_DATA<21>

CPU_DATA<20>

CPU_DATA<22>

CPU_DATA<23>

CPU_DATA<24>

CPU_DATA<26>

CPU_DATA<25>

CPU_DATA<27>

CPU_DATA<28>

CPU_DATA<29>

CPU_DATA<31>

CPU_DATA<30>

CPU_DATA<32>

CPU_DATA<33>

CPU_DATA<34>

CPU_DATA<35>

CPU_DATA<36>

CPU_DATA<37>

CPU_DATA<38>

CPU_DATA<39>

CPU_DATA<40>

CPU_DATA<42>

CPU_DATA<41>

CPU_DATA<43>

CPU_DATA<45>

CPU_DATA<44>

CPU_DATA<46>

CPU_DATA<47>

CPU_DATA<49>

CPU_DATA<50>

CPU_DATA<48>

CPU_DATA<51>

CPU_DATA<52>

CPU_DATA<54>

CPU_DATA<53>

CPU_DATA<55>

CPU_DATA<56>

CPU_DATA<57>

CPU_DATA<59>

CPU_DATA<58>

CPU_DATA<60>

CPU_DATA<62>

CPU_DATA<61>

CPU_DATA<63>

CPU_DBG_L

CPU_DRDY_L

CPU_DTI<0>

CPU_DTI<1>

CPU_DTI<2>

CPU_TA_L

CPU_TEA_L

+1_5V_INTREPID_PLL

MAXBUS_SLEEP

CPU_DATA<39>

CPU_DATA<37>

CPU_DATA<36>

CPU_DATA<35>

CPU_DATA<34>

CPU_DATA<33>

CPU_DATA<55>

CPU_DATA<41>

CPU_DATA<40>

CPU_DATA<53>

CPU_DATA<51>

CPU_DATA<50>

CPU_DATA<49>

CPU_DATA<48>

CPU_DATA<32>

INT_CPUFB_IN

INT_CPUFB_OUT_NORM

INT_CPUFB_IN_NORM

INT_CPUFB_LONG

CPU_DATA<63>

CPU_DATA<62>

CPU_DATA<61>

CPU_DATA<60>

CPU_DATA<59>

MAXBUS_SLEEP

CPU_DATA<58>

CPU_DATA<57>

CPU_DATA<56>

CPU_TA_L

CPU_TS_L

CPU_BR_L

CPU_ARTRY_L

CPU_DRDY_L

CPU_HIT_L

CPU_AACK_L

CPU_TEA_L

CPU_DBG_L

CPU_BG_L

MAXBUS_SLEEP

CPU_QREQ_L

INT_CPUFB_IN

SYSCLK_CPU_UF

SYSCLK_CPU

INT_CPUFB_OUT

INT_CPUFB_OUT_SHORT

38

38

38

38

38

34

34

34

34

34

23

23

23

23

23

16

16

16

16

16

15

15

15

15

15

36

36

36

36

8

36

36

8

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

38

8

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

8

36

36

36

36

36

36

36

36

36

36

36

36

36

8

36

8

36

36

8

8

8

7

8

8

7

36

36

36

8

8

8

36

36

36

8

8

8

8

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

8

8

8

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

36

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

36

36

36

8

8

14

7

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

36

8

8

8

8

8

7

8

8

8

8

8

8

8

8

8

8

8

8

8

7

8

36

36

36

6

5

5

6

6

6

5

6

6

5

5

5

5

6

6

6

5

38

5

30

8

30

30

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

5

5

5

5

5

5

5

12

5

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

8

36

36

36

6

6

6

6

6

5

6

6

6

5

5

5

5

5

5

5

5

5

5

5

5

8

36

5

8

36

A0

A1

A6

A2

A3

A4

A5

A9

A8

A7

A10

A11

A12

A13

A14

A15

A16

A20

A17

A18

A19

CE

OE

WE

WP

PWD

GND

DQ0

DQ1

DQ6

DQ5

DQ2

DQ3

DQ4

DQ7

VPP VCC

FEPR-1MX8

(2 OF 9)

DDR_VREF_1

DDR_VREF_0

DDR_DATA_0

DDR_DATA_1

DDR_DATA_2

DDR_DATA_3

DDR_DATA_4

DDR_DATA_5

DDR_DATA_6

DDR_DATA_7

DDR_DATA_8

DDR_DATA_9

DDR_DATA_10

DDR_DATA_11

DDR_DATA_12

DDR_DATA_13

DDR_DATA_14

DDR_DATA_15

DDR_DATA_16

DDR_DATA_17

DDR_DATA_18

DDR_DATA_19

DDR_DATA_20

DDR_DATA_21

DDR_DATA_25

DDR_DATA_26

DDR_DATA_27

DDR_DATA_28

DDR_DATA_29

DDR_DATA_30

DDR_DATA_33

DDR_DATA_34

DDR_DATA_35

DDR_DATA_36

DDR_DATA_37

DDR_DATA_38

DDR_DATA_39

DDR_DATA_40

DDR_DATA_41

DDR_DATA_42

DDR_DATA_43

DDR_DATA_44

DDR_DATA_45

DDR_DATA_46

DDR_DATA_47

DDR_DATA_48

DDR_DATA_49

DDR_DATA_50

DDR_DATA_51

DDR_DATA_52

DDR_DATA_53

DDR_DATA_54

DDR_DATA_55

DDR_DATA_56

DDR_DATA_57

DDR_DATA_58

DDR_DATA_59

DDR_DATA_60

DDR_DATA_61

DDR_DATA_62

DDR_DATA_63

DDR_DATA_22

DDR_DATA_23

DDR_DATA_24

DDR_DATA_31

DDR_DATA_32

DDR_BA_0

DDR_BA_1

DDRCS_3

DDRCS_2

DDRCS_1

DDRCS_0

DDR_DQS_7

DDR_DQS_6

DDR_DQS_5

DDR_DQS_4

DDR_DQS_3

DDR_DQS_2

DDR_DQS_1

DDR_DQS_0

DDR_DM_7

DDR_DM_6

DDR_DM_5

DDR_DM_4

DDR_DM_3

DDR_DM_2

DDR_DM_1

DDR_DM_0

DDRRAS

DDRCAS

DDRWE

DDRCKE0

DDRCKE1

DDRCKE2

DDRCKE3

DDR_MCLK_0_P

DDR_MCLK_0_N

DDR_MCLK_1_P

DDR_MCLK_1_N

DDR_MCLK_2_P

DDR_MCLK_2_N

DDR_MCLK_3_P

DDR_MCLK_3_N

DDR_MCLK_4_P

DDR_MCLK_4_N

DDR_MCLK_5_P

DDR_MCLK_5_N

DDR_REF

DDR_SELHI_0

DDR_SELHI_1

DDR_SELLO_0

DDR_SELLO_1

MEMORY

DDR

INTERFACE

DDR_A_10

DDR_A_11

DDR_A_12

DDR_A_9

DDR_A_8

DDR_A_7

DDR_A_6

DDR_A_5

DDR_A_4

DDR_A_3

DDR_A_2

DDR_A_1

DDR_A_0

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

OVERRIDE ROM MODULE

PULL-DOWN RESISTORS TO ENSURE

CKE STAYS LOW AFTER INTREPID

2.5V I/O SHUTS OFF

1MB BOOT ROM

INTERCEPTS ROM CHIP SELECT

MEM_VREF

’2’ & ’3’ GO TO SLOT B

’0’ & ’1’ GO TO SLOT A

’2’ & ’3’ GO TO SLOT B

’0’ & ’1’ GO TO SLOT A

’1’S ARE SAME POLARITY (ACTIVE-HI)

’0’S ARE SAME POLARITY (ACTIVE-LO)

CNTL

BA

ADDR

CKE

CS

PINS ARE SWAPABLE FOR RPAKS

CLOCKS

INT - DDR/BOOTROM

SERIES RESISTORS FOR CLOCK/CONTROL SIGNALS

402

MF

1/16W

10K

5%

2

1

R387

402

MF

1/16W

5%

22

21

R238

402

MF

1/16W

1%

1K

2

1

R199

402

MF

1/16W

1%

10K

2

1

R198

402

CERM

10V

20%

0.1UF

2

1

C245

1%

1/16W

MF

402

10K

2

1

R191

OMIT

3.3V

TSOP

12

9

11 3130

10

24

3923

35

34

33