Analog Devices DA1843JST, DA1843JS Datasheet

a |

Serial-Port 16-Bit |

|

SoundComm Codec |

||

|

|

|

|

|

AD1843 |

|

|

|

FEATURES

Single Chip Integrated Speech, Audio, Fax and Modem Codec

Highly Configurable Stereo åD ADCs and Quad åD DACs

Supports V.34, V.32bis, and Fallback Modem Standards As Well As Voice Over Data

Dual Digital Resamplers with Programmable Input and Output Phase and Frequency

Three On-Chip Phase Lock Loops for Synchronization to External Signals, Including Video

Thirteen Analog Inputs and Seven Analog Outputs Advanced Analog and Digital Signal Mixing and Digital-

to-Digital Sample Rate Conversion Programmable Gain, Attenuation and Mute On-Chip Signal Filters

Digital Interpolation and Decimation Analog Output Low Pass

1 Hz Resolution Programmable Sample Rates from 4 kHz to 54 kHz Derived from a Single Clock Input

80-Lead PQFP and 100-Lead TQFP Packages Operation from +5 V or Mixed +5 V/+3 V Supplies FIFO-Buffered Serial Digital Interface Compatible with

ADSP-21xx Fixed-Point DSPs Advanced Power Management

VHDL Model of Serial Port Available; Evaluation Board and MAFE Board Available

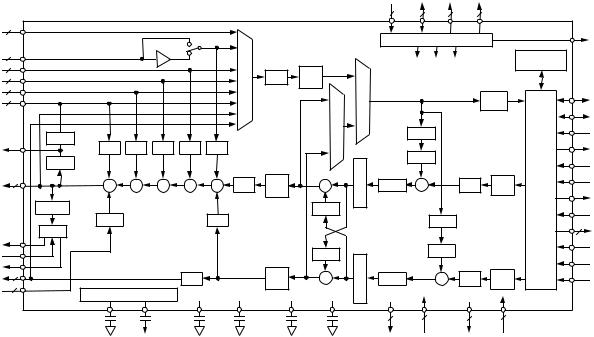

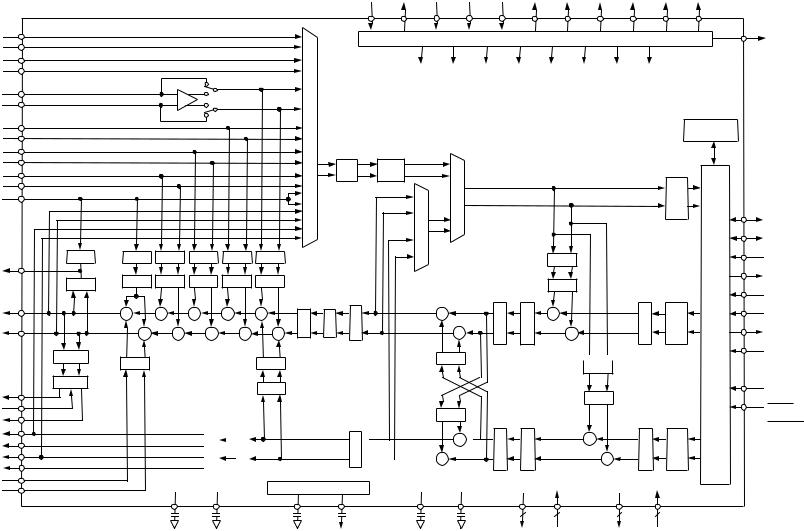

GENERAL PRODUCT DESCRIPTION

The AD1843 SoundComm™ Codec is a complete analog front end for high performance DSP-based telephony and audio applications. The device integrates the real-world analog I/O requirements for many popular functions thereby reducing size, power consumption, and system complexity. The AD1843 SoundComm is the world’s first codec which can support four different sample rates simultaneously, without any beat frequency noise issues. This is essential for highly integrated audio/ modem/fax products since the sample rates associated with audio are very much distinct from the sample rates associated with telephony-oriented data communication. It is also the first codec to offer on-chip digital phase lock loops for sample rate synchronization to external clock signals. This sample rate flexibility is enabled through Analog Devices’ Continuous Time Oversampling (CTO) technology.

The main elements of the AD1843 are its extensive input and mixing section, its two channels of sigma-delta (åD) analog-to-digital conversion, its four channels of åD digital-to-analog conversion, its digital filters, and the clock and control circuitry for implementing the device’s different modes. The AD1843 permits flexible samplerate selection through programming and external synchronization, many input and output options, and many mixing options.

(continued on page 11)

SoundComm is a trademark of Analog Devices, Inc.

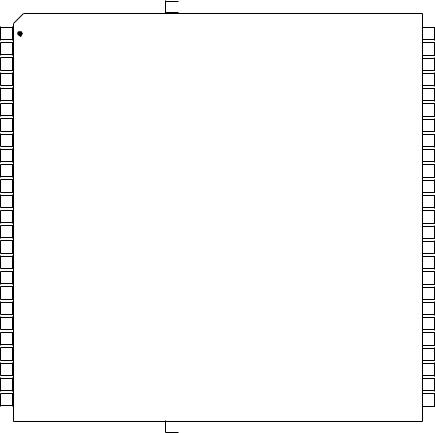

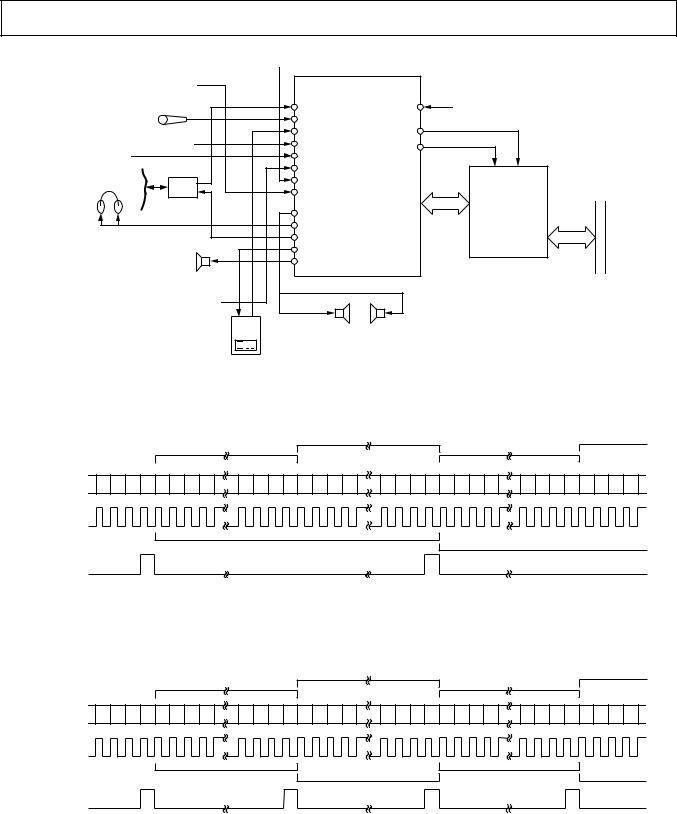

SIMPLIFIED FUNCTIONAL BLOCK DIAGRAM

|

|

|

|

|

|

|

|

|

|

|

|

SYNC |

XTAL |

CONV |

BIT |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

3 |

2 |

|

3 |

|

3 |

|

|

LIN |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD1843 |

|

CLOCK GENERATION |

|

|

CLKOUT |

||||||

|

|

|

|

20 dB |

|

|

S |

|

|

|

|

||||||||

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CONTROL |

|

||

MIC |

|

|

|

|

|

E |

|

|

|

|

|

|

|

|

|

|

|

||

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

AUX1 |

|

|

|

|

|

L |

|

|

åD |

S |

|

|

|

|

|

|

REGISTERS |

|

|

2 |

|

|

|

|

|

E |

PGA |

|

|

|

|

|

|

|

|

|

|||

AUX2 |

|

|

|

|

|

C |

ADC |

E |

|

|

|

|

|

|

|

|

|||

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

AUX3 |

|

|

|

|

|

T |

|

|

|

L |

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

S |

E |

|

|

|

|

|

µ/A |

|

|

||

MIN |

|

|

|

|

|

O |

|

|

|

|

|

|

|

ADC |

SCLK |

||||

|

|

|

|

|

|

R |

|

|

E |

C |

|

|

|

|

|

LAW |

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

T |

|

|

|

|

|

|

D |

SDFS |

|

|

|

|

|

|

|

|

|

|

E |

O |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

|

||

|

|

|

|

|

|

|

|

|

|

C |

R |

|

ATTN |

|

|

|

|

SDI |

|

|

MUTE |

|

|

|

|

|

|

|

|

|

|

|

|

|

G |

||||

|

|

|

|

|

|

|

|

|

T |

|

|

|

|

|

|

|

I |

|

|

MOUT |

|

GAM |

GAM |

GAM |

GAM |

GAM |

|

|

O |

|

|

|

|

|

|

|

SDO |

||

|

|

|

|

|

MUTE |

|

|

|

|

T |

|||||||||

|

MUTE |

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

A |

BM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

||

|

|

|

|

|

|

|

|

|

|

|

M |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

µ/A |

|

|

|

LOUT1 |

å |

å |

å |

å |

å |

GAM |

åD |

|

å |

U |

ATTN |

å |

|

|

FIFO |

DAC1 |

CS |

||

|

DAC |

|

T |

|

|

LAW |

|

||||||||||||

|

|

|

LEFT AND |

|

|

|

|

E |

|

|

|

|

|

I |

TSO |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

DRIVER |

|

RIGHT CHANNELS |

|

|

|

|

MUTE |

|

|

|

|

|

|

|

N |

TSI |

||

|

|

MUTE |

|

|

GAM |

|

|

|

|

|

ATTN |

|

|

|

T |

||||

|

MUTE |

|

|

|

|

|

|

|

|

|

|

E |

2 |

||||||

|

|

GAM = GAIN |

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

XCTL [1:0] |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

F |

|

||

HPOUTL |

|

|

|

ATTENUATION |

|

|

|

|

|

|

|

|

|

|

|

|

PDMNFT |

||

|

|

|

|

|

|

|

|

|

|

MUTE |

|

|

|

A |

|||||

HPOUTC |

|

|

|

MUTE |

|

|

|

|

|

MUTE |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|||||

|

LEFT AND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RESET |

|||

HPOUTR |

4 |

|

|

|

|

|

|

|

M |

|

|

|

|

|

|

E |

|||

RIGHT CHANNELS |

|

|

|

åD |

|

|

|

|

|

|

|

µ/A |

|

|

|||||

LOUT2 |

GAM |

|

|

|

å |

U |

ATTN |

|

å |

|

FIFO |

DAC2 |

PWRDWN |

||||||

|

|

|

|

|

|

DAC |

|

T |

|

|

LAW |

||||||||

SUM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

2 |

VOLTAGE REFERENCE |

|

|

|

|

|

|

E |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

3 |

|

|

8 |

9 |

|

|

REV. 0 |

|

VREF |

CMOUT |

AAFILTL |

AAFILTR |

FILTL |

FILTR |

|

GNDA |

VCC |

|

GNDD |

VDD |

|

|

||||

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

© Analog Devices, Inc., 1996

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

AD1843–SPECIFICATIONS

STANDARD TEST CONDITIONS UNLESS OTHERWISE NOTED |

|

|||

Temperature |

25 |

°C |

DAC Conditions |

ADC Input Conditions |

Digital Supply (VDD) |

5.0 |

V |

Autocalibrated |

Mic 20 dB Gain Disabled |

Analog Supply (VCC) |

5.0 |

V |

0 dB Attenuation |

LIN Single-Ended |

Sample Rate (FS) |

48 |

kHz |

0 dB Relative to Full Scale |

(LINLSD & LINRSD = 0) |

Input Signal |

1008 |

Hz |

16-Bit Linear Mode |

Autocalibrated |

Analog Output Passband |

20 Hz to 20 kHz |

|

No Output Load |

0 dB PGA Gain |

ADC FFT Size |

2048 |

|

Mute Off |

–1.0 dB Relative to Full Scale |

DAC FFT Size |

8192 |

|

DAC1 Single-Ended |

Line Input |

VIH |

2.0 |

V |

DAC2 Differential |

16-Bit Linear Mode |

VIL |

0.8 |

V |

|

|

VOH |

2.4 |

V |

|

|

VOL |

0.4 |

V |

|

|

IOH |

–2 |

mA |

|

|

IOL |

2 |

mA |

|

|

ANALOG INPUT

|

Min |

Typ |

Max |

Units |

|

|

|

|

|

Full-Scale Input Voltage (RMS Values Assume Sine Wave Input) |

|

|

|

|

All Inputs with ADRFLT & ADLFLT = 0 and LINLSD & LINRSD = 0 |

|

1 |

|

V rms |

(LINLP, LINRP, AUX1L, AUX1R, AUX2L, |

2.55 |

2.828 |

3.1 |

V p-p |

AUX2R, AUX3L, AUX3R, MIN) |

|

|

|

|

All Inputs with ADRFLT & ADLFLT = 0 and LINLSD & LINRSD = 1 |

|

2 |

|

V rms |

(LINLP & LINLN, LINRP & LINRN) |

5.1 |

5.656 |

6.2 |

V p-p |

All Inputs with ADRFLT & ADLFLT = 1 and LINLSD & LINRSD = 0 |

|

1.127 |

|

V rms |

(LINLP, LINRP, AUX1L, AUX1R, AUX2L, AUX2R, AUX3L, |

2.8 |

3.156 |

3.5 |

V p-p |

AUX3R, MIN) |

|

|

|

|

All Inputs with ADRFLT & ADLFLT = 1 and LINLSD & LINRSD = 1 |

|

2.254 |

|

V rms |

(LINLP & LINLN, LINRP & LINRN) |

5.6 |

6.312 |

7.0 |

V p-p |

MIC with +20 dB Gain (LMGE & RMGE = 1 |

|

|

|

|

and ADRFLT & ADLFLT = 0) |

|

0.1 |

|

V rms |

(MICL, MICR) |

0.25 |

0.2828 |

0.31 |

V p-p |

MIC with 0 dB Gain (LMGE & RMGE = 0 |

|

|

|

|

and ADRFLT & ADLFLT = 0) |

|

1 |

|

V rms |

(MICL, MICR) |

2.55 |

2.828 |

3.1 |

V p-p |

AUX, SUM and MIN Input Impedance* |

10K |

|

|

Ω |

(AUX1L, AUX1R, AUX2L, AUX2R, AUX3L, AUX3R, SUML, |

|

|

|

|

SUMR, MIN) |

|

|

|

Ω |

LIN Input Impedance* (LINLP, LINLN, LINRP, LINRN) |

40K |

|

|

|

MIC Input Impedance* (MICL, MICR) |

20K |

|

|

Ω |

Input Capacitance* (All Inputs) |

|

15 |

|

pF |

|

|

|

|

|

PROGRAMMABLE GAIN AMPLIFIER–ADC |

|

|

|

|

|

|

|

|

|

|

Min |

Typ |

Max |

Units |

|

|

|

|

|

Step Size (0 dB to 22.5 dB) (All Steps Tested) |

1.3 |

1.5 |

1.7 |

dB |

PGA Gain Range Span* |

21.5 |

22.5 |

23.5 |

dB |

|

|

|

|

|

INPUT (AUX1, AUX2, AUX3, MIN, MIC) |

|

|

|

|

ANALOG AMPLIFIERS/ATTENUATORS |

|

|

|

|

|

|

|

|

|

|

Min |

Typ |

Max |

Units |

|

|

|

|

|

Step Size (+12.0 dB to –30 dB) (All Steps Tested) |

1.25 |

1.5 |

1.75 |

dB |

Step Size (–31.5 dB to –34.5 dB) (All Steps Tested) |

1.1 |

1.5 |

1.9 |

dB |

Input Gain/Attenuation Range* |

45.5 |

46.5 |

47.5 |

dB |

Mute Attenuation* |

|

–80.0 |

|

dB |

|

|

|

|

|

–2– |

REV. 0 |

AD1843

DIGITAL DECIMATION AND INTERPOLATION FILTERS–AUDIO MODE*

|

|

Min |

Max |

Units |

|

|

|

|

|

Passband |

|

0 |

0.40 × FS |

Hz |

Passband Ripple |

|

0 |

–0.016 |

dB |

Transition Band |

|

0.4 × FS |

0.6 × FS |

Hz |

Stopband1 |

|

0.6 × FS |

|

Hz |

Stopband Rejection |

|

91.8 |

|

dB |

Group Delay |

|

|

15/FS |

s |

Group Delay Variation Over Passband |

|

|

0.0 |

μs |

DIGITAL DECIMATION AND INTERPOLATION FILTERS–MODEM MODE* |

|

|

|

|

|

|

|

|

|

|

|

Min |

Max |

Units |

|

|

|

|

|

Passband |

|

0 |

0.442 × FS |

Hz |

Passband Ripple |

|

0 |

–0.220 |

dB |

Transition Band |

|

0.442 × FS |

0.542 × FS |

Hz |

Stopband2 |

|

0.542 × FS |

|

Hz |

Stopband Rejection |

|

75.7 |

|

dB |

Group Delay |

|

|

19/FS |

s |

Group Delay Variation Over Passband |

|

|

0.0 |

μs |

Sample Rate |

|

|

24 |

kHz |

|

|

|

|

|

DIGITAL DECIMATION AND INTERPOLATION FILTERS–RESAMPLER MODE* |

|

|

|

|

|

|

|

|

|

|

|

Min |

Max |

Units |

|

|

|

|

|

Passband |

|

0 |

0.4 × FS |

Hz |

Passband Ripple |

|

0 |

–0.035 |

dB |

Transition Band |

|

0.4 × FS |

0.5 × FS |

Hz |

Stopband3 |

|

0.5 × FS |

|

Hz |

Stopband Rejection |

|

92.2 |

|

dB |

Group Delay |

|

|

25/FS |

s |

Group Delay Variation Over Passband |

|

|

0.0 |

μs |

ANALOG-TO-DIGITAL CONVERTERS |

|

|

|

|

|

|

|

|

|

|

Min |

Typ |

Max |

Units |

|

|

|

|

|

Audio Dynamic Range (–60 dB Input, THD+N Referenced to Full Scale, |

|

|

|

|

A-Weighted, ADRFLT & ADLFLT = 0) |

80 |

85 |

|

dB |

Modem Dynamic Range (–60 dB Input, THD+N Referenced to Full Scale, |

|

|

|

|

300 Hz to 4 kHz Analog Output Passband, LINRSD & LINLSD = 1, |

|

|

|

|

ADRFLT & ADLFLT = 1, FS = 12.8 kHz) |

87 |

90 |

|

dB |

Audio THD+N (Referenced to Full Scale) |

|

|

0.03 |

% |

|

|

–74 |

–70 |

dB |

Modem THD+N (–3.0 dB Referenced to Full Scale, |

|

|

|

|

300 Hz to 4 kHz Analog Output Passband, LINRSD & LINLSD = 1, |

|

|

|

|

ADRFLT & ADLFLT = 1, FS = 12.8 kHz) |

|

|

0.02 |

% |

|

|

–78.5 |

–74 |

dB |

Audio Signal-to-Intermodulation Distortion* (CCIF Method) |

|

–94 |

–80 |

dB |

ADC Crosstalk* |

|

|

|

|

LIN Inputs (Input L, Ground R, Read R; Input R, Ground L, Read L) |

|

|

–80 |

dB |

Line to MIC (Input LIN, Ground and Select MIC, Read Both Channels) |

|

|

–80 |

dB |

Line to AUX1, AUX2, AUX3, MIN |

|

|

–80 |

dB |

Interchannel Gain Mismatch (Difference of Gain Errors) |

|

|

±0.5 |

dB |

ADC Offset Error |

|

10 |

50 |

mV |

|

|

|

|

|

REV. 0 |

–3– |

AD1843

DAC1 DIGITAL-TO-ANALOG CONVERTERS

|

Min |

Typ |

Max |

Units |

|

|

|

|

|

Audio Dynamic Range (–60 dB Input, THD+N Referenced to Full Scale, |

|

|

|

|

A-Weighted, DA1FLT = 0) |

77 |

80 |

|

dB |

Audio THD+N (Referenced to Full Scale, DA1FLT = 0) |

|

|

0.03 |

% |

|

|

–74 |

–70 |

dB |

Audio Signal-to-Intermodulation Distortion* (CCIF Method) |

|

–92 |

–80 |

dB |

Interchannel Gain Mismatch (Difference of Gain Errors) |

|

|

±0.5 |

dB |

DAC Crosstalk* (Input L, Zero R, Measure LOUT1R; Input R, Zero L, |

|

|

|

|

Measure LOUT1L) |

|

|

–77 |

dB |

Total Out-of-Band Energy* |

|

|

|

|

(Measured from 0.6 × FS to 100 kHz in Audio Mode) |

|

|

–60 |

dB |

Audible Out-of-Band Energy* |

|

|

|

|

(Measured from 0.6 × FS to 22 kHz in Audio Mode, |

|

|

|

|

Tested at FS = 8.0 kHz) |

|

|

–72 |

dB |

DAC2 DIGITAL-TO-ANALOG CONVERTERS |

|

|

|

|

|

|

|

|

|

|

Min |

Typ |

Max |

Units |

|

|

|

|

|

Audio Dynamic Range (–60 dB Input, THD+N Referenced to Full Scale, |

|

|

|

|

A-Weighted, DA2FLT = 0) |

78 |

80 |

|

dB |

Modem Dynamic Range (–60 dB Input, THD+N Referenced to Full Scale, |

|

|

|

|

300 Hz to 4 kHz Analog Output Passband, DA2FLT = 1, RDA2G5:0 |

|

|

|

|

& LDA2G5:0 = 000101 [4.5 dB], FS = 12.8 kHz) |

87 |

90 |

|

dB |

Audio THD+N (Referenced to Full Scale, DA2FLT = 0) |

|

|

0.03 |

% |

|

|

–77 |

–70 |

dB |

Modem THD+N (–3.0 dB Referenced to Full Scale, |

|

|

|

|

300 Hz to 4 kHz Analog Output Passband, DA2FLT = 1, RDA2G5:0 |

|

|

|

|

& LDA2G5:0 = 000101 [4.5 dB], FS = 12.8 kHz) |

|

|

0.016 |

% |

|

|

–81 |

–76 |

dB |

Audio Signal-to-Intermodulation Distortion* (CCIF Method) |

|

–86 |

–80 |

dB |

Interchannel Gain Mismatch (Difference of Gain Errors) |

|

|

±0.5 |

dB |

DAC Crosstalk* (Input L, Zero R, Measure LOUT2R; Input R, Zero L, |

|

|

|

|

Measure LOUT2L) |

|

|

–80 |

dB |

Total Out-of-Band Energy* |

|

|

|

|

(Measured from 0.6 × FS to 100 kHz in Audio Mode) |

|

|

–60 |

dB |

Audible Out-of-Band Energy* |

|

|

|

|

(Measured from 0.6 × FS to 22 kHz in Audio Mode, |

|

|

|

|

Tested at FS = 8.0 kHz) |

|

|

–72 |

dB |

DC Offset |

|

5 |

25 |

mV |

|

|

|

|

|

DAC1 AND DAC2 ANALOG AMPLIFIERS/ATTENUATORS |

|

|

|

|

|

|

|

|

|

|

Min |

Typ |

Max |

Units |

|

|

|

|

|

Step Size (+12.0 dB to –30.0 dB) (All Steps Tested) |

1.25 |

1.5 |

1.75 |

dB |

Step Size (–31.5 dB to –34.5 dB) (All Steps Tested) |

1.1 |

1.5 |

1.9 |

dB |

Step Size (–36.0 dB to –82.5 dB)* |

1.3 |

1.5 |

1.7 |

dB |

Output Attenuation Span* |

81.5 |

82.5 |

83.5 |

dB |

Mute Attenuation* |

|

–80 |

|

dB |

|

|

|

|

|

DIGITAL MIX ATTENUATORS |

|

|

|

|

|

|

|

|

|

|

Min |

Typ |

Max |

Units |

|

|

|

|

|

Step Size (0 dB to –94.5 dB)* (All Steps Tested) |

1.3 |

1.5 |

1.7 |

dB |

Output Attenuation Span* |

93.5 |

94.5 |

95.5 |

dB |

Mute Attenuation* |

|

–90 |

|

dB |

|

|

|

|

|

–4– |

REV. 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD1843 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ANALOG OUTPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Min |

|

|

|

|

Typ |

|

Max |

|

Units |

||||||||||||||||||||||

LOUT1 Full-Scale Output Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.707 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V rms |

||||||||||||||||||||||||||||||||

(RMS Values Assume Sine Wave Input) |

|

|

|

|

|

|

|

|

|

|

|

|

1.8 |

|

2.0 |

|

|

|

|

|

|

|

2.2 |

|

|

|

|

|

V p-p |

||||||||||||||||||||||||||||||||||||

LOUT2 Full-Scale Single-Ended Output Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.707 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V rms |

||||||||||||||||||||||||||||||||

(RMS Values Assume Sine Wave Input) |

|

|

|

|

|

|

|

|

|

|

|

|

1.8 |

|

2.0 |

|

|

|

|

|

|

|

2.2 |

|

|

|

|

|

V p-p |

||||||||||||||||||||||||||||||||||||

LOUT2 Full-Scale Differential Output Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.414 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V rms |

||||||||||||||||||||||||||||||||

(RMS Values Assume Sine Wave Input) |

|

|

|

|

|

|

|

|

|

|

|

|

3.6 |

|

4.0 |

|

|

|

|

|

|

|

4.4 |

|

|

|

|

|

V p-p |

||||||||||||||||||||||||||||||||||||

LOUT1 Output Impedance* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

600 |

|

|

|

|

|

Ω |

|||||||||||||||||||||

LOUT2 Output Impedance* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

Ω |

||||||||||||||||||||

LOUT1 External Load Impedance* |

|

|

|

|

|

|

|

|

|

|

|

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

kΩ |

||||||||||||||||||||||||||

LOUT2 External Load Impedance* |

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

kΩ |

|||||||||||||||||||||||||

MOUT External Load Impedance* |

|

|

|

|

|

|

|

|

|

|

|

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

kΩ |

||||||||||||||||||||||||||

HPOUT External Load Impedance* |

|

|

|

|

|

|

|

|

|

|

|

|

16 |

|

32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ω |

||||||||||||||||||||||||||||||||

HPOUT THD+N (Referenced to Full Scale, 32 Ω External Load Impedance) |

|

|

|

|

|

|

|

0.10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

% |

|

|

|||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

–60 |

|

|

|

|

|

|

|

|

|

dB |

|||||||||||||

Output Capacitance* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

|

|

|

|

pF |

||||||||||||||||

External Load Capacitance* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

100 |

|

|

|

|

|

pF |

|||||||||||||||||||||

CMOUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2.10 |

2.25 |

|

|

|

|

|

|

2.40 |

|

|

|

|

|

V |

|||||||||||||||||||||||

External CMOUT Load Current* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10 |

|

|

|

|

|

|

μA |

|||||||||||||||||||||||||

CMOUT Output Impedance* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

±5 |

|

|

|

|

|

kΩ |

||||||||||||||||||||||||||

Mute Click* (Muted Output Minus Unmuted Midscale DAC1 and DAC2 Outputs) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

mV |

|||||||||||||||||||||||||||||||||||||||

SYSTEM SPECIFICATIONS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Max |

|

Units |

|||||||||

System Frequency Response Ripple* (Line-In to Line-Out) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.0 |

|

|

|

|

|

dB |

||||||||||||||||||||||||||||||||

Differential Nonlinearity* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

±1 |

|

|

|

|

|

Bit |

|||||||||||||||||||||

Phase Linearity Deviation* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

|

|

|

|

|

|

Degrees |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

STATIC DIGITAL SPECIFICATIONS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Min |

|

Max |

|

Units |

|||||||||||||||||||

High-Level Input Voltage (VIH) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

Digital Inputs, Except SCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2.0 |

|

|

|

|

|

|

|

|

VDD+ 0.3 |

|

V |

||||||||||||||||||||||||||||||||||||

XTALI and SCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2.4 |

|

|

|

|

|

|

|

|

VDD+ 0.3 |

|

V |

|||||||||||||||||||||||||||

Low-Level Input Voltage (VIL) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

–0.3 |

0.8 |

|

|

|

|

|

V |

||||||||||||||||||||||||||||||||||||

High-Level Output Voltage (VOH) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2.4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

||||||||||||||||||||||||||||||

Low-Level Output Voltage (VOL) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.4 |

|

|

|

|

|

V |

||||||||||||||||||||||||||

Input Leakage Current (GO/NOGO Tested) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

–10 |

10 |

|

|

|

|

|

|

μA |

|||||||||||||||||||||||||||||||||||

Output Leakage Current (GO/NOGO Tested) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

–10 |

10 |

|

|

|

|

|

|

μA |

|||||||||||||||||||||||||||||||||||

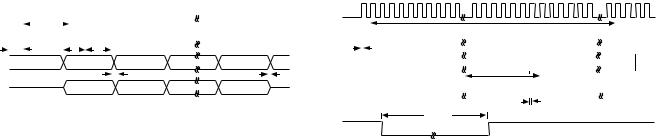

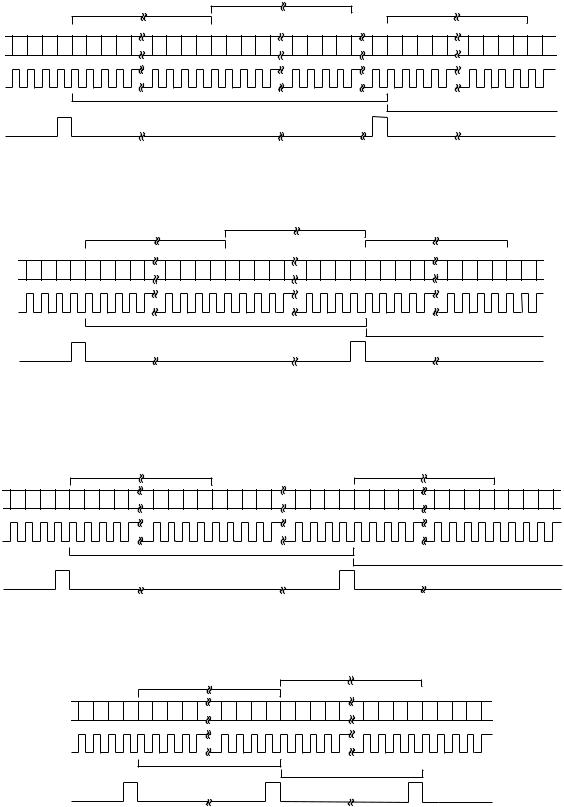

TIMING PARAMETERS (GUARANTEED OVER OPERATING TEMPERATURE AND DIGITAL SUPPLY RANGE) |

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Min |

|

|

|

|

Typ |

|

Max |

|

Units |

||||||||||||||||||||||

Serial Data Frame Sync [SDFS] Period (t1) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

μs |

|||||||||||||||||||||||

(Master Mode, FRS = 1 [16 Slots per Frame], SCF = 0 [SCLK = 12.288 MHz]) |

|

|

|

|

|

|

|

20.833 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||

Frame Sync [SDFS] HI Pulse Width (t2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

80 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ns |

|||||||||||||||||||||||||||||

Clock [SCLK] to Frame Sync [SDFS] Propagation Delay (tPD1) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

|

|

|

|

ns |

|||||||||||||||||||||||||||||||

Data [SDI] Input Setup Time to SCLK (tS) |

|

|

|

|

|

|

|

|

|

|

|

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ns |

||||||||||||||||||||||||||

Data [SDI] Input Hold Time from SCLK (tH) |

|

|

|

|

|

|

|

|

|

|

|

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ns |

||||||||||||||||||||||||||

Clock [SCLK] to Output Data [SDO] Valid (tDV) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

|

|

|

|

ns |

|||||||||||||||||||||||||

Clock [SCLK] to Output Data [SDO] Three-State [High-Z] (tHZ) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

|

|

|

|

ns |

|||||||||||||||||||||||||||||||||||

Clock [SCLK] to Time Slot Output [TSO] Propagation Delay (tPD2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

|

|

|

|

ns |

|||||||||||||||||||||||||||||||||||

RESET and PWRDWN LO Pulse Width (tRPWL) |

|

|

|

|

|

|

|

|

|

|

|

|

100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ns |

||||||||||||||||||||||||||

SCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

SDFS |

|

|

|

|

t2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDFS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

t |

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tPD1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

PD1 |

|

|

|

S |

|

|

H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDI |

|

|

|

BIT 15 |

BIT 14 |

BIT 0 |

SDI OR SDO |

|

|

|

15 |

14 |

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

2 |

1 |

|

0 |

15 |

14 |

13 |

|

|

|

|

|

15 |

1413 |

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tDV |

|

tHZ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LAST |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VALID |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

SDO |

|

|

|

BIT 15 |

BIT 14 |

BIT 0 |

TSO |

|

|

|

|

|

|

|

|

|

|

|

|

|

TIME SLOT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tPD2

tRPWL

RESET

PWRDWN

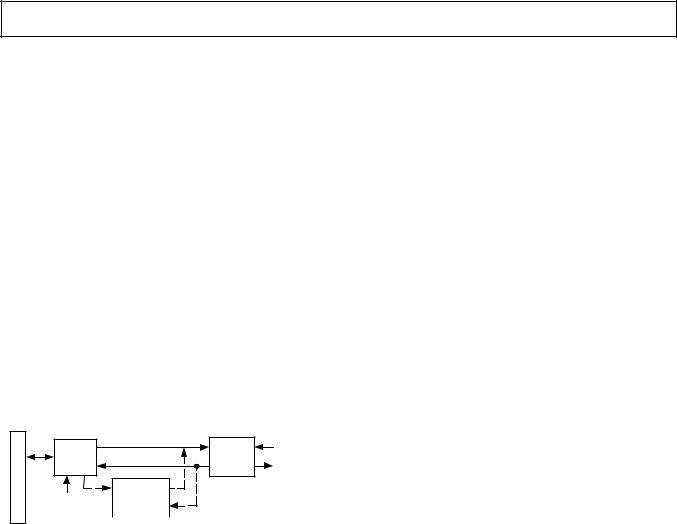

Figure 1. Timing Diagrams

REV. 0 |

–5– |

AD1843

POWER SUPPLY (33 Ω HPOUT LOAD)

|

|

|

|

|

|

|

|

|

Min |

Typ |

Max |

Units |

Power Supply Range—Analog VCC |

4.75 |

|

5.25 |

V |

||||||||

Power Supply Range—Digital VDD |

2.85 |

|

5.25 |

V |

||||||||

Total Power Supply Current—5.0 VCC and VDD Operating |

|

|

|

|

||||||||

|

(5.0 VCC and VDD Supplies) |

|

210 |

250 |

mA |

|||||||

Total Power Supply Current—5.0 VCC/3.0 VDD Operating* |

|

|

|

|

||||||||

|

(5.0 VCC Analog/3.0 VDD Digital Supplies) |

|

150 |

175 |

mA |

|||||||

Analog Supply Current—5.0 VCC Operating |

|

60 |

75 |

mA |

||||||||

Digital Supply Current—5.0 VDD Operating |

|

150 |

175 |

mA |

||||||||

Digital Supply Current—3.0 VDD Operating* |

|

90 |

100 |

mA |

||||||||

Digital Power Supply Current—VDD Power Down ( |

PWRDWN |

LO) |

|

|

1 |

mA |

||||||

|

Analog Power Supply Current—VCC Power Down ( |

PWRDWN |

LO) |

|

|

0.5 |

mA |

|||||

Power Dissipation—5.0 VCC and VDD Operating (Current × Nominal Supply) |

|

|

1250 |

mW |

||||||||

|

Power Dissipation—5.0 VCC/3.0 VDD Operating* (Current × Nominal Supply) |

|

|

875 |

mW |

|||||||

Power Dissipation—5.0 VCC and VDD Power Down ( |

PWRDWN |

LO) |

|

|

|

|

||||||

|

(Current × Nominal Supply) |

|

|

7.5 |

mW |

|||||||

Power Dissipation—5.0 VCC/3.0 VDD Power Down* ( |

PWRDWN |

LO) |

|

|

|

|

||||||

|

(Current × Nominal Supply) |

|

|

5 |

mW |

|||||||

Power Supply Rejection (100 mV p-p Signal @ 1 kHz)* |

40 |

|

|

dB |

||||||||

|

(At Both Analog and Digital Supply Pins, for ADC, DAC1 and DAC2) |

|

|

|

|

|||||||

CLOCK SPECIFICATIONS* |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Min |

Typ |

Max |

Units |

Input Crystal/Clock Frequency |

|

24.576 |

|

MHz |

||||||||

Input Clock Duty Cycle (When an External Clock Is Used Instead of a Crystal) |

25/75 |

|

75/25 |

% |

||||||||

Initialization Sample Rate Change Time |

|

|

0 |

ms |

||||||||

PACKAGE CHARACTERISTICS |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Typ |

|

Units |

|

PQFP θJA (Thermal Resistance [Junction-to-Ambient]) |

|

96 |

|

°C/W |

|||||||

PQFP θJC (Thermal Resistance [Junction-to-Case]) |

|

8.75 |

|

°C/W |

||||||||

TQFP θJA (Thermal Resistance [Junction-to-Ambient]) |

|

30.6 |

|

°C/W |

||||||||

TQFP θJC (Thermal Resistance [Junction-to-Case]) |

|

4.6 |

|

°C/W |

||||||||

NOTES

1The stopband repeats itself at multiples of 64 × FS, where FS is the sampling frequency. Thus the audio mode digital filter will attenuate to –91.8 dB or better across |

|||||||||||||

|

the frequency spectrum except for a range of ± 0.6 × FS wide at multiples of 64 × FS. |

|

|

|

|

|

|

|

|||||

2The stopband repeats itself at multiples of 64 × FS, where FS is the sampling frequency. Thus the modem mode digital filter will attenuate to –75.7 dB or better across |

|||||||||||||

|

the frequency spectrum except for a range of ± 0.542 × FS wide at multiples of 64 × FS. |

|

|

|

|

|

|

||||||

3The stopband repeats itself at multiples of 64 × FS, where FS is the sampling frequency. Thus the resampler mode digital filter will attenuate to –92.2 dB or better |

|||||||||||||

|

across the frequency spectrum except for a range of ± 0.5 × FS wide at multiples of 64 × FS. |

|

|

|

|

|

|

||||||

*Guaranteed, not tested. |

|

|

|

|

|

|

|

|

|

|

|

||

Specifications subject to change without notice. |

|

|

|

|

|

|

|

|

|

|

|||

|

ABSOLUTE MAXIMUM RATINGS* |

|

|

|

*Stresses greater than those listed under “Absolute Maximum Ratings” may cause |

||||||||

|

|

|

|

|

|

|

permanent damage to the device. This is a stress rating only and functional |

||||||

|

|

|

Min |

Max |

Units |

||||||||

|

|

|

operation of the device at these or any other conditions above those indicated in the |

||||||||||

|

Power Supplies |

|

|

|

|

operational section of this specification is not implied. Exposure to absolute |

|||||||

|

Digital (VDD) |

–0.3 |

6.0 |

V |

maximum rating conditions for extended periods may affect device reliability. |

||||||||

|

|

|

|

|

|

|

|

||||||

|

Analog (VCC) |

–0.3 |

6.0 |

V |

|

ORDERING INFORMATION |

|

|

|||||

|

Input Current |

|

±10.0 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|||

|

(Except Supply Pins) |

|

mA |

|

|

|

|

|

|

|

|||

|

|

|

Temperature |

Package |

Package |

||||||||

|

Analog Input Voltage (Signal Pins) |

–0.3 |

VCC + 0.3 |

V |

|

||||||||

|

Model |

Range |

Description |

Option |

|||||||||

|

Digital Input Voltage (Signal Pins) |

–0.3 |

VDD + 0.3 |

V |

|||||||||

|

|

|

|

|

|

|

|

||||||

|

Ambient Temperature (Operating) |

0 |

+70 |

°C |

AD1843JS |

0°C to +70°C |

80-Lead PQFP |

S-80 |

|||||

|

Storage Temperature |

–65 |

+150 |

°C |

|||||||||

|

AD1843JST |

0°C to +70°C |

100-Lead TQFP |

ST-100 |

|||||||||

|

ESD Tolerance (Human Body |

1000 |

|

V |

|||||||||

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|||||

|

Model per Method 3015.2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

of MIL-STD-883B) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAUTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily |

|

|

|

|

|||||||||

|

WARNING! |

|

|

||||||||||

accumulate on the human body and test equipment and can discharge without detection. |

|

|

|

||||||||||

Although the AD1843 features proprietary ESD protection circuitry, permanent damage may |

|

|

|

|

|||||||||

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD |

|

ESD SENSITIVE DEVICE |

|

||||||||||

precautions are recommended to avoid performance degradation or loss of functionality. |

|

|

|||||||||||

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

–6– |

REV. 0 |

AD1843

PIN CONFIGURATIONS

80-Lead PQFP

|

|

|

SDI |

|

SCLK |

|

GNDD |

|

V |

|

CLKOUT |

|

CONV3 |

|

BIT3 |

|

GNDD |

|

V |

|

CONV2 |

|

BIT2 |

GNDD |

|

V |

|

CONV1 |

|

BIT1 |

|

GNDD |

|

V |

|

V |

|

XTALO |

|

XTALI |

|

|||

|

|

|

|

|

|

|

|

|

DD |

|

|

|

|

|

|

|

|

|

DD |

|

|

|

|

|

|

|

DD |

|

|

|

|

|

|

|

DD |

|

DD |

|

|

|

|

|

|

|

|

|

|

80 |

|

79 |

|

78 |

|

77 |

|

76 |

|

75 |

|

74 |

|

73 |

|

72 |

|

71 |

|

70 |

|

69 |

|

68 |

|

67 |

|

66 |

|

65 |

|

64 |

|

63 |

|

62 |

|

61 |

|

|

|

SDO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GNDD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

60 |

||||

SDFS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

59 |

XCTL1 |

|||

GNDD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

58 |

XCTL0 |

|||

VDD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

57 |

SYNC3 |

|||

TSI |

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

56 |

SYNC2 |

||

TSO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

55 |

SYNC1 |

|||

GNDD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

54 |

GNDD |

|||

VDD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD |

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

53 |

||||

CS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RESET |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

52 |

||||

BM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD1843 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PWRDWN |

||||

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

51 |

|||||||||

AUX3R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TOP VIEW |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD |

||||

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

50 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(Not to Scale) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

AUX3L |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|