AMD LX 70000.8W, LX 80000.9W, LX 90001.5W, LX 60000.7W User Manual

AMD Geode™ LX Processors

Data Book

February 2009

Publication ID: 33234H

AMD Geode™ LX Processors Data Book

© 2009 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. (“AMD”) products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD’s Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD’s products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD’s product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

Contacts

www.amd.com

Trademarks

AMD, the AMD Arrow logo, AMD Athlon, Geode, GeodeLink, 3DNow!, and combinations thereof, are trademarks of Advanced Micro Devices, Inc.

Linux is a registered trademark of Linus Torvalds.

WinBench is a registered trademark of Ziff Davis, Inc.

Windows is a registered trademark of Microsoft Corporation in the United States and/or other jurisdictions.

Pentium is a registered trademark and MMX is a trademark of Intel Corporation in the United States and/or other jurisdictions.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

2 |

AMD Geode™ LX Processors Data Book |

Contents |

33234H |

|

|

Contents

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.0 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.1 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.0 Architecture Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.1 CPU Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.2 GeodeLink™ Control Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.3 GeodeLink™ Interface Units . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.4 GeodeLink™ Memory Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.5 Graphics Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.6 Display Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.7 Video Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.8 Video Input Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.9 GeodeLink™ PCI Bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.10 Security Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

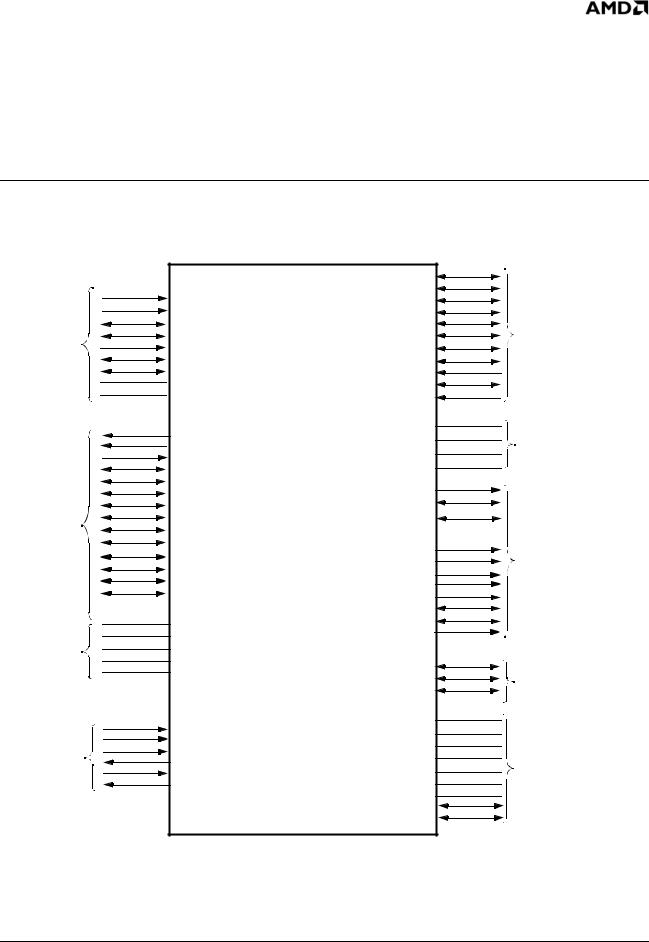

3.0 Signal Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.1 Buffer Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2 Bootstrap Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

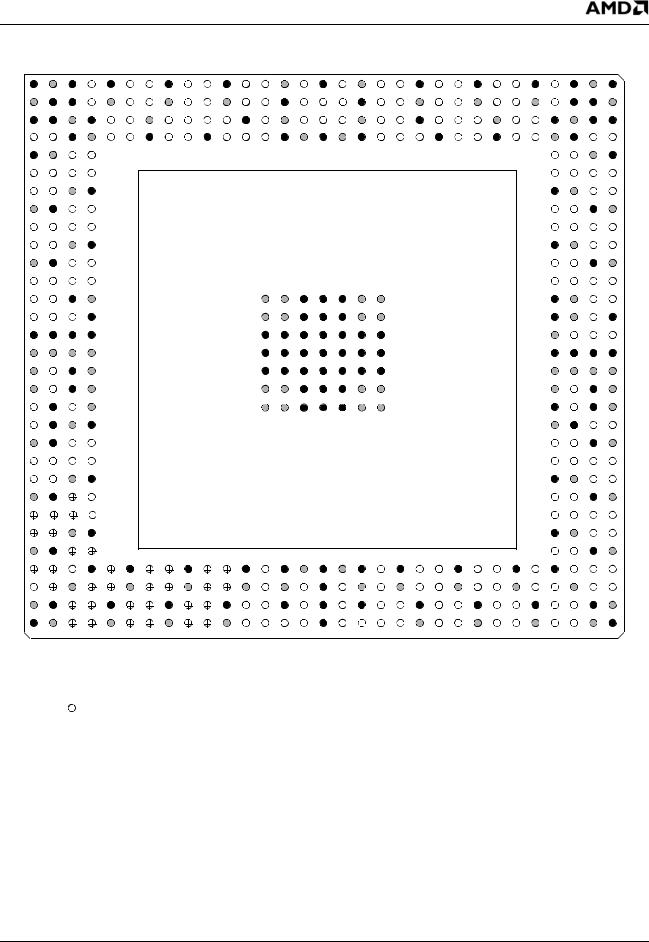

3.3 Ball Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.4 Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

4.0 GeodeLink™ Interface Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

4.1 MSR Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

4.2 GLIU Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

5.0 CPU Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.1 Core Processor Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.2 Instruction Set Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

5.3 Application Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

5.4 System Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

5.5 CPU Core Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

AMD Geode™ LX Processors Data Book |

3 |

33234H |

Contents |

6.0 Integrated Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

6.1 |

GeodeLink™ Memory Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

210 |

6.2 |

GeodeLink™ Memory Controller Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

219 |

6.3 |

Graphics Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

237 |

6.4 |

Graphics Processor Register Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

254 |

6.5 |

Display Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

278 |

6.6 |

Display Controller Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

300 |

6.7 |

Video Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

388 |

6.8 |

Video Processor Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

412 |

6.9 |

Video Input Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

462 |

6.10 |

Video Input Port Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

482 |

6.11 |

Security Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

510 |

6.12 |

Security Block Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

513 |

6.13 |

GeodeLink™ Control Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

533 |

6.14 |

GeodeLink™ Control Processor Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

539 |

6.15 |

GeodeLink™ PCI Bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

566 |

6.16 |

GeodeLink™ PCI Bridge Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

572 |

7.0 Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 597

7.1 Electrical Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 597

7.2 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 597

7.3 Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 598

7.4 DC Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 599

7.5 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 604

7.6 AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 607

8.0 Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 619

8.1 General Instruction Set Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 619 8.2 CPUID Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 627 8.3 Processor Core Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 633 8.4 MMX™, FPU, and AMD 3DNow!™ Technology Instructions Sets . . . . . . . . . . . . . . . . . . . . . . 658

9.0 Package Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 675

9.1 Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 675

Appendix A Support Documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 677

A.1 Order Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 677

A.2 Data Book Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 679

4 |

AMD Geode™ LX Processors Data Book |

List of Figures |

33234H |

|

|

List of Figures

Figure 1-1. |

Internal Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 11 |

Figure 3-1. |

Signal Groups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 21 |

Figure 3-2. |

BGU481 Ball Assignment Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 25 |

Figure 4-1. |

GeodeLink™ Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 46 |

Figure 6-1. |

Integrated Functions Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

209 |

Figure 6-2. |

GLMC Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

210 |

Figure 6-3. |

HOI Addressing Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

211 |

Figure 6-4. |

HOI Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

211 |

Figure 6-5. |

LOI Addressing Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

212 |

Figure 6-6. |

LOI Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

212 |

Figure 6-7. |

Request Pipeline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

215 |

Figure 6-8. |

DDR Reads . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

216 |

Figure 6-9. |

DDR Writes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

217 |

Figure 6-10. |

Graphics Processor Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

237 |

Figure 6-11. |

14-Bit Repeated Pattern . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

244 |

Figure 6-12. |

Display Controller High-Level Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

278 |

Figure 6-13. |

GUI Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

279 |

Figure 6-14. |

VGA Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

280 |

Figure 6-15. |

VGA Frame Buffer Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

288 |

Figure 6-16. |

Graphics Controller High-level Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

289 |

Figure 6-17. |

Write Mode Data Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

290 |

Figure 6-18. |

Read Mode Data Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

291 |

Figure 6-19. |

Color Compare Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

292 |

Figure 6-20. |

Graphics Filter Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

293 |

Figure 6-21. |

Flicker Filter and Line Buffer Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

295 |

Figure 6-22. |

Interlaced Timing Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

298 |

Figure 6-23. |

Video Processor Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

389 |

Figure 6-24. |

Video Processor Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

390 |

Figure 6-25. |

Downscaler Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

392 |

Figure 6-26. |

Linear Interpolation Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

393 |

Figure 6-27. |

Mixer Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

395 |

Figure 6-28. |

Color Key and Alpha-Blending Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

396 |

Figure 6-29. |

VOP Internal Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

398 |

Figure 6-30. |

525-Line NTSC Video Window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

399 |

Figure 6-31. |

HBLANK and VBLANK for Lines 20-262, 283-524 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

399 |

Figure 6-32. |

HBLANK and VBLANK for Lines 263, 525 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

400 |

Figure 6-33. |

HBLANK and VBLANK for Lines 1-18, 264-281 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

400 |

Figure 6-34. |

HBLANK and VBLANK for Lines 19, 282 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

400 |

Figure 6-35. |

BT.656 8/16 Bit Line Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

403 |

Figure 6-36. |

Flat Panel Display Controller Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

405 |

Figure 6-37. |

Dithered 8x8 Pixel Pattern . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

408 |

Figure 6-38. |

N-Bit Dithering Pattern Schemes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

409 |

Figure 6-39. |

VIP Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

463 |

Figure 6-40. |

BT.656, 8/16-Bit Line Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

467 |

Figure 6-41. |

525 line, 60 Hz Digital Vertical Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

468 |

AMD Geode™ LX Processors Data Book |

5 |

|

|

33234H |

List of Figures |

Figure 6-42. |

Ancillary Data Packets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 469 |

Figure 6-43. |

Message Passing Data Packet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 470 |

Figure 6-44. |

Data Streaming Data Packet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 470 |

Figure 6-45. |

BT.601 Mode Default Field Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 471 |

Figure 6-46. |

BT.601 Mode Programmable Field Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 472 |

Figure 6-47. |

BT.601 Mode Horizontal Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 472 |

Figure 6-48. |

BT.601 Mode Vertical Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 473 |

Figure 6-49. |

YUV 4:2:2 to YUV 4:2:0 Translation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 474 |

Figure 6-50. |

Dual Buffer for Message Passing and Data Streaming Modes . . . . . . . . . . . . . . . |

. . . . . . . 476 |

Figure 6-51. |

Example VIP YUV 4:2:2 SAV/EAV Packets Stored in System Memory in a Linear Buffer . 477 |

|

Figure 6-52. |

Example VIP YUV 4:2:0 Planar Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 478 |

Figure 6-53. |

Example VIP 8/16and 10-bit Ancillary Packets Stored in System Memory . . . . . |

. . . . . . . 479 |

Figure 6-54. |

Security Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 510 |

Figure 6-55. |

GLCP Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 533 |

Figure 6-56. |

Processor Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 536 |

Figure 6-57. |

GIO Interface Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 537 |

Figure 6-58. |

GLPCI Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 566 |

Figure 6-59. |

Atomic MSR Accesses Across the PCI Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 568 |

Figure 6-60. |

Simple Round-Robin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 570 |

Figure 6-61. |

Weighted Round-Robin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 570 |

Figure 7-1. |

VMEMLX Power Split . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 600 |

Figure 7-2. |

Drive Level and Measurement Points for Switching Characteristics . . . . . . . . . . . |

. . . . . . . 607 |

Figure 7-3. |

Drive Level and Measurement Points for Switching Characteristics . . . . . . . . . . . |

. . . . . . . 608 |

Figure 7-4. |

Power Up Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 609 |

Figure 7-5. |

Drive Level and Measurement Points for Switching Characteristics . . . . . . . . . . . |

. . . . . . . 609 |

Figure 7-6. |

Drive Level and Measurement Points for Switching Characteristics . . . . . . . . . . . |

. . . . . . . 610 |

Figure 7-7. |

Drive Level and Measurement Points for Switching Characteristics . . . . . . . . . . . |

. . . . . . . 611 |

Figure 7-8. |

DDR Write Timing Measurement Points . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 615 |

Figure 7-9. |

DDR Read Timing Measurement Points . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 616 |

Figure 9-1. |

BGU481 Top/Side View/Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 675 |

Figure 9-2. |

BGU481 Bottom View/Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 676 |

Figure A-1. |

AMD Geode™ LX Processors OPN Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 677 |

6 |

AMD Geode™ LX Processors Data Book |

List of Tables |

33234H |

|

|

List of Tables

Table 2-1. |

Graphics Processor Feature Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 17 |

Table 3-1. |

Video Signal Definitions Per Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 22 |

Table 3-2. |

Buffer Type Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 23 |

Table 3-3. |

Bootstrap Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 24 |

Table 3-4. |

Ball Type Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 24 |

Table 3-5. |

Ball Assignments - Sorted by Ball Number . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 26 |

Table 3-6. |

Ball Assignments - Sorted Alphabetically by Signal Name . . . . . . . . . . . . . . . . . . . . . . . . . |

. 30 |

Table 3-7. |

Signal Behavior During and After Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 43 |

Table 4-1. |

MSR Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 45 |

Table 4-2. |

MSR Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 47 |

Table 4-3. |

GLIU Memory Descriptor Address Hit and Routing Description . . . . . . . . . . . . . . . . . . . . . |

. 48 |

Table 4-4. |

GLIU I/O Descriptor Address Hit and Routing Description . . . . . . . . . . . . . . . . . . . . . . . . . |

. 49 |

Table 4-5. |

GeodeLink™ Device Standard MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 50 |

Table 4-6. |

GLIU Specific MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 50 |

Table 4-7. |

GLIU Statistic and Comparator MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 51 |

Table 4-8. |

GLIU P2D Descriptor MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 53 |

Table 4-9. |

GLIU Reserved MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 53 |

Table 4-10. |

GLIU IOD Descriptor MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 54 |

Table 5-1. |

Initialized Core Register Controls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 89 |

Table 5-2. |

Application Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 91 |

Table 5-3. |

Segment Register Selection Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 92 |

Table 5-4. |

EFLAGS Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 93 |

Table 5-5. |

System Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 94 |

Table 5-6. |

Control Registers Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 95 |

Table 5-7. |

CR4 Bit Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 96 |

Table 5-8. |

CR3 Bit Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 96 |

Table 5-9. |

CR2 Bit Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 96 |

Table 5-10. |

CR0 Bit Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 96 |

Table 5-11. |

Effects of Various Combinations of EM, TS, and MP Bits . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 98 |

Table 5-12. |

Standard GeodeLink™ Device MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 99 |

Table 5-13. |

CPU Core Specific MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 99 |

Table 5-14. |

XC_HIST_MSR Exception Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

126 |

Table 5-15. |

Region Properties Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

170 |

Table 5-16. |

Read Operations vs. Region Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

170 |

Table 5-17. |

Write Operations vs. Region Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

170 |

Table 6-1. |

LOI - 2 DIMMs, Same Size, 1 DIMM Bank . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

213 |

Table 6-2. |

LOI - 2 DIMMs, Same Size, 2 DIMM Banks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

213 |

Table 6-3. |

Non-Auto LOI - 1 or 2 DIMMs, Different Sizes, 1 DIMM Bank . . . . . . . . . . . . . . . . . . . . . . . |

214 |

Table 6-4. |

Non-Auto LOI - 1 or 2 DIMMs, Different Sizes, 2 DIMM Banks . . . . . . . . . . . . . . . . . . . . . . |

214 |

Table 6-5. |

Standard GeodeLink™ Device MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

219 |

Table 6-6. |

GLMC Specific MSR Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

219 |

Table 6-7. |

Graphics Processor Feature Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

238 |

Table 6-8. |

BLT Command Buffer Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

239 |

Table 6-9. |

Vector Command Buffer Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

240 |

Table 6-10. |

LUT (Lookup Table) Load Command Buffer Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

240 |

AMD Geode™ LX Processors Data Book |

7 |

|

|

33234H |

List of Tables |

|

|

|

Table 6-11. |

Data Only Command Buffer Structure . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . . 240 |

Table 6-12. |

Bit Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 241 |

Table 6-13. |

Pixel Ordering for 4-Bit Pixels . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 243 |

Table 6-14. |

Example Vector Pattern . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 244 |

Table 6-15. |

Example Vector Length . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 244 |

Table 6-16. |

Example of Monochrome Pattern . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 247 |

Table 6-17. |

Example of 8-Bit Color Pattern (3:3:2 Format) . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 248 |

Table 6-18. |

Example of 16-Bit Color Pattern (5:6:5 Format) . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 248 |

Table 6-19. |

32-bpp 8:8:8:8 Color Data Format . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 249 |

Table 6-20. |

16-bpp Color Data Format . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 249 |

Table 6-21. |

8-bpp 3:3:2 Color Data Format . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 249 |

Table 6-22. |

Monochrome Data Format . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 249 |

Table 6-23. |

Example of Byte-Packed Monochrome Source Data . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 250 |

Table 6-24. |

Example of Unpacked Monochrome Source Data . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 250 |

Table 6-25. |

GP_RASTER_MODE Bit Patterns . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 251 |

Table 6-26. |

Common Raster Operations . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 251 |

Table 6-27. |

Alpha Blending Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 252 |

Table 6-28. |

Standard GeodeLink™ Device MSRs Summary . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 254 |

Table 6-29. |

Graphics Processor Configuration Register Summary . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 254 |

Table 6-30. |

PAT_COLOR Usage for Color Patterns . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 264 |

Table 6-31. |

PAT_DATA Usage for Color Patterns . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 265 |

Table 6-32. |

Display Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 281 |

Table 6-33. |

Cursor Display Encodings . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 283 |

Table 6-34. |

Icon Display Encodings . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 283 |

Table 6-35. |

Cursor/Color Key/Alpha Interaction . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 284 |

Table 6-36. |

Video Bandwidth . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 286 |

Table 6-37. |

YUV 4:2:0 Video Data Ordering . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 287 |

Table 6-38. |

YUV 4:2:2 Video Data Ordering . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 287 |

Table 6-39. |

VGA Text Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 288 |

Table 6-40. |

Text Mode Attribute Byte Format . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 288 |

Table 6-41. |

VGA Graphics Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 288 |

Table 6-42. |

Programming Image Sizes . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 297 |

Table 6-43. |

Vertical Timing in Number of Lines . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 298 |

Table 6-44. |

Timing Register Settings for Interlaced Modes . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 299 |

Table 6-45. |

Standard GeodeLink™ Device MSRs Summary . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 300 |

Table 6-46. |

DC Specific MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 300 |

Table 6-47. |

DC Configuration Control Register Summary . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 300 |

Table 6-48. |

VGA Block Configuration Register Summary . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 303 |

Table 6-49. |

VGA Block Standard Register Summary . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 303 |

Table 6-50. |

VGA Block Extended Register Summary . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 304 |

Table 6-51. |

VGA Sequencer Registers Summary . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 358 |

Table 6-52. |

Font Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 360 |

Table 6-53. |

CRTC Register Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 361 |

Table 6-54. |

CRTC Registers Summary . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 362 |

Table 6-55. |

CRTC Memory Addressing Modes . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 371 |

Table 6-56. |

Graphics Controller Registers Summary . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 373 |

Table 6-57. |

Attribute Controller Registers Summary . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 378 |

Table 6-58. |

Video DAC Registers Summary . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 382 |

Table 6-59. |

Extended Registers Summary . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 384 |

Table 6-60. |

Truth Table for Alpha-Blending . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 397 |

Table 6-61. |

VOP Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 401 |

Table 6-62. |

SAV/EAV Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 402 |

Table 6-63. |

Protection Bit Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 402 |

Table 6-64. |

SAV VIP Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 404 |

Table 6-65. |

VOP Clock Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . 404 |

|

|

|

8 |

|

AMD Geode™ LX Processors Data Book - |

List of Tables |

33234H |

|

Table 6-66. |

Panel Output Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 406 |

Table 6-67. |

Register Settings for Dither Enable/Disable Feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 410 |

Table 6-68. |

Display RGB Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 411 |

Table 6-69. |

Standard GeodeLink™ Device MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 412 |

Table 6-70. |

Video Processor Module Specific MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 412 |

Table 6-71. |

Video Processor Module Configuration Control Registers Summary . . . . . . . . . . . . . . . . |

. 412 |

Table 6-72. |

VIP Capabilities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 462 |

Table 6-73. |

SAV/EAV Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 466 |

Table 6-74. |

VIP Data Types / Memory Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 475 |

Table 6-75. |

Standard GeodeLink™ Device MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 482 |

Table 6-76. |

VIP Configuration/Control Registers Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 482 |

Table 6-77. |

EEPROM Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 512 |

Table 6-78. |

Standard GeodeLink™ Device MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 513 |

Table 6-79. |

Security Block Specific MSRs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 513 |

Table 6-80. |

Security Block Configuration/Control Registers Summary . . . . . . . . . . . . . . . . . . . . . . . . . |

. 513 |

Table 6-81. |

TAP Control Instructions (25-Bit IR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 534 |

Table 6-82. |

TAP Instruction Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 534 |

Table 6-83. |

GIO_PCI Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 537 |

Table 6-84. |

CIS Signaling Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 538 |

Table 6-85. |

Standard GeodeLink™ Device MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 539 |

Table 6-86. |

GLCP Specific MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 539 |

Table 6-87. |

Bootstrap Bit Settings and Reset State of GLCP_SYS_RSTPLL (PW1 and IRQ13 = 0) |

. . 556 |

Table 6-88. |

Bootstrap Bit Settings and Reset State of GLCP_SYS_RSTPLL (PW1 and IRQ13 vary) . |

. 557 |

Table 6-89. |

Format for Accessing the Internal PCI Configuration Registers . . . . . . . . . . . . . . . . . . . . |

. 569 |

Table 6-90. |

PCI Device to AD Bus Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 570 |

Table 6-91. |

Standard GeodeLink™ Device MSRs Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 572 |

Table 6-92. |

GLPCI Specific Registers Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 572 |

Table 6-93. |

Region Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 586 |

Table 7-1. |

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 597 |

Table 7-2. |

Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 598 |

Table 7-3. |

AMD Geode LX 900@1.5W Processor DC Currents . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 600 |

Table 7-4. |

AMD Geode LX 800@0.9W Processor DC Currents . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 601 |

Table 7-5. |

AMD Geode LX 700@0.8W Processor DC Currents . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 602 |

Table 7-6. |

AMD Geode LX 600@0.7W Processor DC Currents . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 603 |

Table 7-7. |

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 604 |

Table 7-8. |

System Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 608 |

Table 7-9. |

PCI Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 609 |

Table 7-10. |

VIP Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 610 |

Table 7-11. |

Flat Panel Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 611 |

Table 7-12. |

CRT Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 612 |

Table 7-13. |

CRT Display Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 612 |

Table 7-14. |

CRT Display Analog (DAC) Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 613 |

Table 7-15. |

Memory (DDR) Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 614 |

Table 7-16. |

JTAG Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 617 |

Table 8-1. |

General Instruction Set Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 619 |

Table 8-2. |

Instruction Fields . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 620 |

Table 8-3. |

Instruction Prefix Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 620 |

Table 8-4. |

w Field Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 621 |

Table 8-5. |

d Field Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 621 |

Table 8-6. |

s Field Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 621 |

Table 8-7. |

eee Field Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 622 |

Table 8-8. |

mod r/m Field Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 622 |

Table 8-9. |

General Registers Selected by mod r/m Fields and w Field . . . . . . . . . . . . . . . . . . . . . . . |

. 623 |

Table 8-10. |

reg Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 624 |

Table 8-11. |

sreg2 Field Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 624 |

AMD Geode™ LX Processors Data Book |

9 |

|

|

33234H |

List of Tables |

Table 8-12. |

sreg3 Field (FS and GS Segment Register Selection) . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 624 |

Table 8-13. |

ss Field Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 625 |

Table 8-14. |

index Field Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 625 |

Table 8-15. |

mod base Field Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 626 |

Table 8-16. |

CPUID Instruction with EAX = 00000000h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 627 |

Table 8-17. |

CPUID Instruction with EAX = 00000001h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 627 |

Table 8-18. |

CPUID Instruction Codes with EAX = 00000000 . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 628 |

Table 8-19. |

CPUID Instruction with EAX = 80000000h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 629 |

Table 8-20. |

CPUID Instruction with EAX = 80000001h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 629 |

Table 8-21. |

CPUID Instruction Codes with EAX = 80000001h . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 630 |

Table 8-22. |

CPUID Instruction with EAX = 80000002h, 80000003h, or 80000004h . . . . . . . . . |

. . . . . . 631 |

Table 8-23. |

CPUID Instruction with EAX = 80000005h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 632 |

Table 8-24. |

CPUID Instruction with EAX = 80000006h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 632 |

Table 8-25. |

Processor Core Instruction Set Table Legend . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 633 |

Table 8-26. |

Processor Core Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 634 |

Table 8-27. |

MMX™, FPU, and AMD 3DNow!™ Instruction Set Table Legend . . . . . . . . . . . . . |

. . . . . . 658 |

Table 8-28. |

MMX™ Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 660 |

Table 8-29. |

FPU Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 667 |

Table 8-30. |

AMD 3DNow!™ Technology Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 671 |

Table A-1. |

Valid OPN Combinations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 678 |

Table A-2. |

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 679 |

Table A-3. |

Edits to Current Revision . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 679 |

10 |

AMD Geode™ LX Processors Data Book - |

Overview |

33234H |

|

|

Overview1

1.1General Description

AMD Geode™ LX processors are integrated x86 processors specifically designed to power embedded devices for entertainment, education, and business. Serving the needs of consumers and business professionals alike, it’s an excellent solution for embedded applications, such as thin clients, interactive set-top boxes, single board computers, and mobile computing devices.

Available with a core voltage of 1.2V, 1.25V, or 1.4V it offers extremely low typical power consumption leading to longer battery life and enabling small form-factor, fanless designs.

While the processor core provides maximum compatibility with the vast amount of Internet content available, the intelligent integration of several other functions, including graphics and video datapaths, offers a true system-level multimedia solution.

For implementation details and suggestions for this device, see the supporting documentation (i.e., application notes, schematics, etc.) on the AMD Embedded Developer Support Web site (http://wwwd.amd.com/dev, NDA required).

SYSREF |

|

|

|

|

|

|

Clock Module |

|

|

|

|

|

|

|

|

CPU Core |

|

|

|

|

|

Graphics Processor (GP) |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

System PLL |

|

|

|

64 KB L1 I-cache |

|

Integer |

|

MMU |

|

|

FPU |

|

|

|

|

BLT Engine |

|

1 KB |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Unit |

|

Load/Store |

|

|

|

|

|

|

|

|

|

LUT |

|

||||

DOTREF |

|

|

|

|

|

|

CPU PLL |

|

|

|

64 KB L1 D-cache |

|

|

|

|

|

|

|

|

|

|

|

|

|

ROP Unit |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

DOTCLK PLL |

|

|

|

|

|

TLB |

|

|

|

Bus Controller |

|

|

|

|

|

Alpha Compositing |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

128 KB L2 cache |

|

|

|

|

|

|

|

|

|

|

|

|

|

Rotation BLT |

|

|

|

|

|||||

SDCLKs |

|

|

|

GeodeLink™ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

Memory |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Controller (GLMC) |

|

|

|

|

|

GeodeLink™ Interface Unit 0 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

64-Bit |

|

|

64-bit DDR SDRAM |

|

|

|

|

|

|

|

|

(GLIU0) |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

DDR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Display Controller (DC) |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Compression Buffer |

|

|

|||

|

|

|

|

|

|

|

GeodeLink™ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

Control |

|

|

|

|

|

GeodeLink™ Interface Unit 1 |

|

|

|

|

|

|

Palette RAM |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

Test/Reset |

|

|

|

|

Processor (GLCP) |

|

|

|

|

|

|

|

|

(GLIU1) |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

Power Mgmnt |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Timing |

|

|

|

|

|||||

Interface |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Graphics Filter/Scaling |

|

|

|||

|

|

|

|

|

|

|

Test |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Diagnostic |

|

|

|

HW VGA |

|

|

|

|

|

|

AMD Geode™ |

Companion I/F |

|

|

RGB |

YUV |

Companion |

|

|

|

Video Processor (VP) |

|

Device |

Security Block |

|

|

||

|

Video Input |

GeodeLink™ |

TFT |

Video Scalar |

|

|

|

||||

|

128-bit AES |

PCI Bridge |

Controller/ |

||

|

Port (VIP) |

|

|||

|

(CBC/ECB) |

(GLPCI) |

Video |

Video Mixer |

|

|

|

||||

|

True |

|

|

Output |

Alpha Blender |

|

|

|

Port (VOP) |

||

|

Random Number |

|

|

||

|

|

|

|

|

|

|

Generator |

|

|

|

|

|

|

|

|

|

3x8-Bit DAC |

|

EEPROM on package |

VIP |

PCI |

TFT/VOP |

|

|

(optional) |

|

|

|

CRT |

|

|

|

|

|

|

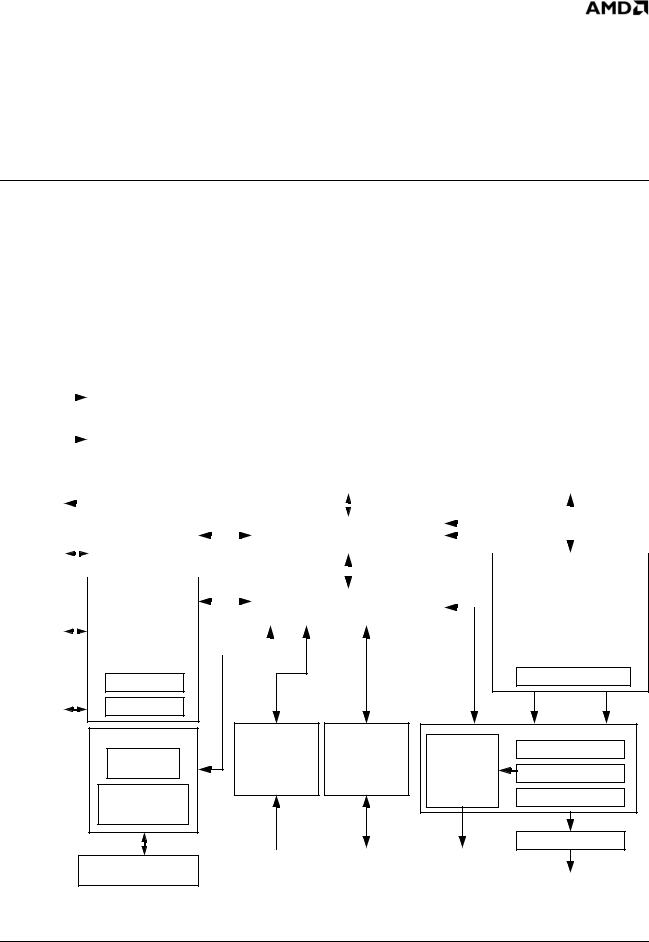

Figure 1-1. Internal Block Diagram

AMD Geode™ LX Processors Data Book |

11 |

33234H |

Overview |

1.2Features

General Features

■Functional blocks include:

—CPU Core

—GeodeLink™ Control Processor

—GeodeLink Interface Units

—GeodeLink Memory Controller

—Graphics Processor

—Display Controller

—Video Processor

– TFT Controller/Video Output Port

—Video Input Port

—GeodeLink PCI Bridge

—Security Block

■0.13 micron process

■Packaging:

—481-Terminal BGU (Ball Grid Array Cavity Up) with internal heatspreader

■Single packaging option supports all features

■Industrial temperature range available for the LX 800@0.9W processor*

CPU Processor Features

■x86/x87-compatible CPU core

■Performance:

—Processor frequency: up to 600 MHz

—Dhrystone 2.1 MIPs: 150 to 450

—Fully pipelined FPU

■Split I/D cache/TLB (Translation Look-aside Buffer):

—64 KB I-cache/64 KB D-cache

—128 KB L2 cache configurable as I-cache, D-cache, or both

■Efficient prefetch and branch prediction

■Integrated FPU that supports the MMX™ and AMD 3DNow!™ instruction sets

■Fully pipelined single precision FPU hardware with microcode support for higher precisions

GeodeLink™ Control Processor

■JTAG interface:

—ATPG, Full Scan, BIST on all arrays

—1149.1 Boundary Scan compliant

■ICE (in-circuit emulator) interface

■Reset and clock control

■Designed for improved software debug methods and performance analysis

■Power Management:

—LX 900@1.5W processor* (Unterminated): Total Dissipated Power (TDP) 5.1W,

2.6W typical @ 600 MHz max power

—LX 800@0.9W processor* (Unterminated): Total Dissipated Power (TDP) 3.6W,

1.8W typical @ 500 MHz max power

—LX 700@0.8W processor* (Unterminated): Total Dissipated Power (TDP) 3.1W,

1.3W typical @ 433 MHz max power

—LX 600@0.7W processor* (Unterminated): Total Dissipated Power (TDP) 2.8W,

1.2W typical @ 366 MHz max power

—GeodeLink active hardware power management

—Hardware support for standard ACPI software power management

—I/O companion SUSP/SUSPA power controls

—Lower power I/O

—Wakeup on SMI/INTR

■Works in conjunction with the AMD Geode™ CS5536 (USB 2.0) or CS5535 (USB 1.1) companion device

GeodeLink™ Architecture

■High bandwidth packetized uni-directional bus for internal peripherals

■Standardized protocol to allow variants of products to be developed by adding or removing modules

■GeodeLink Control Processor (GLCP) for diagnostics and scan control

■Dual GeodeLink Interface Units (GLIUs) for device interconnect

GeodeLink™ Memory Controller

■Integrated memory controller for low latency to CPU and on-chip peripherals

■64-bit wide DDR SDRAM bus operating frequency:

— 200 MHz, 400 MT/S

■Supports unbuffered DDR DIMMS using up to 2 GB DRAM technology

■Supports up to 2 DIMMS (16 devices max)

2D Graphics Processor

■High performance 2D graphics controller

■Alpha BLT

■Windows® GDI GUI acceleration:

— Hardware support for all Microsoft RDP codes

■Command buffer interface for asynchronous BLTs

■Second pattern channel support

■Hardware screen rotation

*The AMD Geode LX 900@1.5W processor operates at 600 MHz, the AMD Geode LX 800@0.9W processor operates at 500 MHz, the AMD Geode LX 700@0.8W processor operates at 433 MHz and the AMD Geode LX 600@.07W processor operates at 366 MHz. Model numbers reflect performance as described here: http://www.amd.com/connectivitysolutions/geodelxbenchmark.

12 |

AMD Geode™ LX Processors Data Book |

Overview |

33234H |

Display Controller

■Hardware frame buffer compression improves Unified Memory Architecture (UMA) memory efficiency

■CRT resolutions supported:

—Supports up to 1920x1440x32 bpp at 85 Hz

—Supports up to 1600x1200x32 bpp at 100 Hz

■Supports up to 1600x1200x32 bpp at 60 Hz for TFT

■Standard Definition (SD) resolution for Video Output Port (VOP):

—720x482 at 59.94 Hz interlaced for NTSC

—768x576 at 50 Hz interlaced for PAL

■High Definition (HD) resolution for Video Output Port (VOP):

—Up to 1920x1080 at 30 Hz interlaced (1080i HD) (74.25 MHz)

—Up to 1280x720 at 60 Hz progressive (720p HD) (74.25 MHz)

■Supports down to 7.652 MHz Dot Clock (320x240 QVGA)

■Hardware VGA

■Hardware supported 48x64 32-bit cursor with alpha blending

Video Processor

■Supports video scaling, mixing and VOP

■Hardware video up/down scalar

■Graphics/video alpha blending and color key muxing

■Digital VOP (SD and HD) or TFT outputs

■Legacy RGB mode

■VOP supports SD and HD 480p, 480i, 720p, and 1080i

GeodeLink™ PCI Bridge

■PCI 2.2 compliant

■3.3V signaling and 3.3V I/Os

■33 to 66 MHz operation

■32-bit interface

■Supports virtual PCI headers for GeodeLink devices

Video Input Port (VIP)

■VESA 1.1 and 2.0 compliant, 8 or 16-bit

■Video Blanking Interval (VBI) support

■8 or 16-bit 80 MHz SD or HD capable

Security Block

■Serial EEPROM interface for 2K bit unique ID and AES (Advanced Encryption Standard) hidden key storage (EEPROM optional inside package)

■Electronic Code Book (ECB) or Cipher Block Chaining (CBC)128-bit AES hardware support

■True random number generator (TRNG)

■VESA 1.1, 2.0 and BT.601 24-bit (out only), BT.656 compliant

Integrated Analog CRT DAC, System Clock PLLs and

Dot Clock PLL

■Integrated Dot Clock PLL with up to 350 MHz clock

■Integrated 3x8-bit DAC with up to 350 MHz sampling

■Integrated x86 core PLL

■Memory PLL

AMD Geode™ LX Processors Data Book |

13 |

33234H |

Overview |

|

|

14 |

AMD Geode™ LX Processors Data Book |

Architecture Overview |

33234H |

|

|

Architecture Overview2

The CPU Core provides maximum compatibility with the vast amount of Internet content available while the intelligent integration of several other functions, including graphics, makes the AMD Geode™ LX processor a true systemlevel multimedia solution.

The AMD Geode LX processor can be divided into major functional blocks (as shown in Figure 1-1 on page 11):

•CPU Core

•GeodeLink™ Control Processor

•GeodeLink Interface Units

•GeodeLink Memory Controller

•Graphics Processor

•Display Controller

•Video Processor

— TFT Controller/Video Output Port

•Video Input Port

•GeodeLink PCI Bridge

•Security Block

2.1CPU Core

The x86 core consists of an Integer Unit, cache memory subsystem, and an x87 compatible FPU (Floating Point Unit). The Integer Unit contains the instruction pipeline and associated logic. The memory subsystem contains the instruction and data caches, translation look-aside buffers (TLBs), and an interface to the GeodeLink Interface Units (GLIUs).

The instruction set supported by the core is a combination of Intel Pentium® processor, AMD Athlon™ processor, and AMD Geode LX processor specific instructions. Specifically, it supports the Pentium, Pentium Pro, AMD 3DNow!™ technology and MMX™ instructions for the AMD Athlon processor. It supports a subset of the specialized AMD Geode LX processor instructions including special SMM instructions. The CPU Core does not support the entire Katmai New Instruction (KNI) set as implemented in the Pentium 3. It does support the MMX instructions for the AMD Athlon processor, which are a subset of the Pentium 3 KNI instructions.

2.1.1Integer Unit

The Integer Unit consists of a single issue 8-stage pipeline and all the necessary support hardware to keep the pipeline running efficiently.

The instruction pipeline in the integer unit consists of eight stages:

1)Instruction Prefetch - Raw instruction data is fetched from the instruction memory cache.

2)Instruction Pre-decode - Prefix bytes are extracted from raw instruction data. This decode looks-ahead to the next instruction and the bubble can be squashed if the pipeline stalls down stream.

3)Instruction Decode - Performs full decode of instruction data. Indicates instruction length back to the Prefetch Unit, allowing the Prefetch Unit to shift the appropriate number of bytes to the beginning of the next instruction.

4)Instruction Queue - FIFO containing decoded x86 instructions. Allows Instruction Decode to proceed even if the pipeline is stalled downstream. Register reads for data operand address calculations are performed during this stage.

5)Address Calculation #1 - Computes linear address of operand data (if required) and issues request to the Data Memory Cache. Microcode can take over the pipeline and inject a micro-box here if multi-box instructions require additional data operands.

6)Address Calculation #2 - Operand data (if required) is returned and set up to the Execution stage with no bubbles if there was a data cache hit. Segment limit checking is performed on the data operand address. The µROM is read for setup to Execution Unit.

7)Execution Unit - Register and/or data memory fetch fed through the Arithmetic Logic Unit (ALU) for arithmetic or logical operations. µROM always fires for the first instruction box down the pipeline. Microcode can take over the pipeline and insert additional boxes here if the instruction requires multiple Execution Unit stages to complete.

8)Writeback - Results of the Execution Unit stages are written to the register file or to data memory.

AMD Geode™ LX Processors Data Book |

15 |

33234H |

Architecture Overview |

2.1.2Memory Management Unit

The memory management unit (MMU) translates the linear address supplied by the integer unit into a physical address to be used by the cache unit and the internal bus interface unit. Memory management procedures are x86-compati- ble, adhering to standard paging mechanisms.

The MMU also contains a load/store unit that is responsible for scheduling cache and external memory accesses. The load/store unit incorporates two performance-enhancing features:

•Load-store reordering gives memory reads required by the integer unit a priority over writes to external memory.

•Memory-read bypassing eliminates unnecessary memory reads by using valid data from the execution unit.

2.1.3Cache and TLB Subsystem

The cache and TLB subsystem of the CPU Core supplies the integer pipeline with instructions, data, and translated addresses (when necessary). To support the efficient delivery of instructions, the cache and TLB subsystem has a single clock access 64 KB 16-way set associative instruction cache and a 16-entry fully associative TLB. The TLB performs necessary address translations when in protected mode. For data, there is a 64 KB 16-way set associative writeback cache, and a 16-entry fully associative TLB. When there is a miss to the instruction or data TLBs, there is a second level unified (instruction and data) 64-entry 2- way set associative TLB that takes an additional clock to access. When there is a miss to the instruction or data caches or the TLB, the access must go to the GeodeLink Memory Controller (GLMC) for processing. Having both an instruction and a data cache and their associated TLBs improves overall efficiency of the integer unit by enabling simultaneous access to both caches.

The L1 caches are supported by a 128 KB unified L2 victim cache. The L2 cache can be configured to hold data, instructions, or both. The L2 cache is 4-way set associative.

2.1.4Bus Controller Unit

The bus controller unit provides a bridge from the processor to the GLIUs. When external memory access is required, due to a cache miss, the physical address is passed to the bus controller unit, that translates the cycle to a GeodeLink cycle.

2.1.5Floating Point Unit

The Floating Point Unit (FPU) is a pipelined arithmetic unit that performs floating point operations as per the IEEE 754 standard. The instruction sets supported are x87, MMX, and AMD 3DNow! technology. The FPU is a pipelined machine with dynamic scheduling of instructions to minimize stalls due to data dependencies. It performs out of order execution and register renaming. It is designed to support an instruction issue rate of one per clock from the

integer core. The datapath is optimized for single precision arithmetic. Extended precision instructions are handled in microcode and require multiple passes through the pipeline. There is an execution pipeline and a load/store pipeline. This allows load/store operations to execute in parallel with arithmetic instructions.

2.2GeodeLink™ Control Processor

The GeodeLink Control Processor (GLCP) is responsible for reset control, macro clock management, and debug support provided in the Geode LX processor. It contains the JTAG interface and the scan chain control logic. It supports chip reset, including initial PLL control and programming and runtime power management macro clock control.

The JTAG support includes a TAP Controller that is IEEE 1149.1 compliant. CPU control can be obtained through the JTAG interface into the TAP Controller, and all internal registers, including CPU Core registers, can be accessed. In-circuit emulation (ICE) capabilities are supported through this JTAG and TAP Controller interface.

The GLCP also includes the companion device interface. The companion device has several unique signals connected to this module that support Geode LX processor reset, interrupts, and system power management.

2.3GeodeLink™ Interface Units

Together, the two GeodeLink Interface Units (GLIU0 and GLIU1) make up the internal bus derived from the GeodeLink architecture. GLIU0 connects five high bandwidth modules together with a seventh link to GLIU1 that connects to the five low bandwidth modules.

2.4GeodeLink™ Memory Controller