Texas Instruments BQ2461X, BQ2463X EVM User Manual

User's Guide

SLUU396A – January 2010 – Revised July 2010

bq2461x/bq2463x EVM (HPA422) Multi-Cell Synchronous Switch-Mode Charger

|

|

Contents |

|

1 |

Introduction .................................................................................................................. |

2 |

|

|

1.1 |

EVM Features ...................................................................................................... |

2 |

|

1.2 |

General Description ................................................................................................ |

2 |

|

1.3 |

I/O Description ...................................................................................................... |

2 |

|

1.4 |

1.4 Controls and Key Parameters Setting ...................................................................... |

3 |

|

1.5 |

Recommended Operating Conditions ........................................................................... |

3 |

2 |

Test Summary ............................................................................................................... |

4 |

|

|

2.1 |

Definitions ........................................................................................................... |

4 |

|

2.2 |

Equipment ........................................................................................................... |

4 |

|

2.3 |

Equipment Setup ................................................................................................... |

5 |

|

2.4 |

Procedure ........................................................................................................... |

6 |

3 |

PCB Layout Guideline ...................................................................................................... |

7 |

|

4 |

Bill of Materials, Board Layout and Schematics ........................................................................ |

8 |

|

|

4.1 |

Bill of Materials ..................................................................................................... |

8 |

5 |

Board Layout ............................................................................................................... |

11 |

|

6 |

Schematics ................................................................................................................. |

19 |

|

|

List of Figures |

|

1 |

Original Test Setup for HPA422 (bq2461x/bq2463x EVM)............................................................ |

5 |

2 |

Top Layer................................................................................................................... |

11 |

3 |

2nd Layer .................................................................................................................... |

12 |

4 |

3rd Layer..................................................................................................................... |

13 |

5 |

Bottom Layer ............................................................................................................... |

14 |

6 |

Top Assembly .............................................................................................................. |

15 |

7 |

Bottom Assembly .......................................................................................................... |

16 |

8 |

Top Silkscreen ............................................................................................................. |

17 |

9 |

Bottom Silkscreen ......................................................................................................... |

18 |

10 |

bq2461x/bq2463x EVM Schematic ..................................................................................... |

19 |

|

|

List of Tables |

1 |

I/O Description............................................................................................................... |

2 |

2 |

Controls and Key Parameters Setting.................................................................................... |

3 |

3 |

Recommended Operating Conditions .................................................................................... |

3 |

4 |

Bill of Materials .............................................................................................................. |

8 |

SLUU396A –January 2010 –Revised July 2010 |

bq2461x/bq2463x EVM (HPA422) Multi-Cell Synchronous Switch-Mode Charger |

1 |

Copyright © 2010, Texas Instruments Incorporated

Introduction |

www.ti.com |

1 Introduction

1.1EVM Features

•Evaluation Module For bq2461x/bq2463x

•High Efficiency Synchronous Buck Charger

•User-programmable up to 26V Battery Voltage

•AC Adapter Operating Range 5 V–28 V

•LED Indication for Control and Status Signals.

•Test Points for Key Signals Available for Testing Purpose. Easy Probe Hook-up.

•Jumpers Available. Easy to Change Connections.

1.2General Description

The bq2461x is highly integrated Li-ion or Li-polymer switch-mode battery charge controllers. The bq2463x is highly integrated switch-mode battery charge controllers designed specifically to charge Lithium Phosphate battery chemistries.

They offer a constant-frequency synchronous PWM controller with high accuracy charge current and voltage regulation, adapter current regulation, termination, charge preconditioning, and charge status monitoring,

The bq2461x/bq2463x charges the battery in three phases: preconditioning, constant current, and constant voltage. Charge is terminated when the current reches a minimum user-selectable level. A programmable charge timer provides a safety backup for charge termination. The bq2461x/bq2463x automatically restarts the charge cycle if the battery voltage falls below an internal threshold, and enters a low-quiescent current sleep mode when the input voltage falls below the battery voltage.

The dynamic power management (DPM) function modifies the charge current depending on system load conditions, avoiding ac adapter overload.

High accuracy current sense amplifiers enable accurate measurement of the ac adapter current, allowing monitoring of overall system power.

For details, see bq24610 and bq24617 (SLUS892), bq24616 (SLUSA49) and bq2463x (SLUS894) data sheets.

1.3I/O Description

|

|

|

|

|

Table 1. I/O Description |

|

|

|

|

|

|

|

|

|

|

|

|

Jack |

Description |

|

|

||

|

|

|

|

|

|

||

|

|

J1–DCIN |

AC adapter, positive output |

|

|

||

|

|

|

|

|

|

||

|

|

J1–GND |

AC adapter, negative output |

|

|

||

|

|

|

|

|

|

||

|

|

J2–VEXT |

External power supply, positive output |

|

|

||

|

|

|

|

|

|

||

|

|

J2–GND |

External power supply, negative output |

|

|

||

|

|

|

|

|

|

||

|

|

J2–TTC |

Timer capacitor pin |

|

|

||

|

|

|

|

|

|

||

|

|

J3–ACSET |

Input current program pin |

|

|

||

|

|

|

|

|

|

||

|

|

J3–ISET1 |

Charge Current Program Pin |

|

|

||

|

|

|

|

|

|

||

|

|

J3–ISET2 |

Pre-charge/Termination program pin |

|

|

||

|

|

|

|

|

|

||

|

|

J3–GND |

Ground |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

Power Good (active low) |

|

|

|

|

J–PG |

|

|

|

||

|

|

J4–CHGEN |

Charge enable |

|

|

||

|

|

|

|

|

|

|

|

|

|

J4–VREF |

IC reference voltage VREF |

|

|

||

|

|

|

|

|

|

|

|

|

|

J4–TS |

Temperature Qualification Voltage Input |

|

|

||

|

|

|

|

|

|

|

|

|

|

J5–VSYS |

Connected to system |

|

|

||

|

|

|

|

|

|

|

|

|

|

J5–VBAT |

Connected to battery pack |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

bq2461x/bq2463x EVM (HPA422) Multi-Cell Synchronous Switch-Mode Charger |

SLUU396A –January 2010 –Revised July 2010 |

|||||

Copyright © 2010, Texas Instruments Incorporated

www.ti.com Introduction

|

Table 1. I/O Description (continued) |

|

|

|

|

Jack |

|

Description |

|

|

|

J5–GND |

|

Ground |

|

|

|

JP1–LOW |

|

Ground |

|

|

|

JP1–TTC |

|

Timer capacitor pin |

|

|

|

JP1–HI |

|

Pull-up voltage source |

|

|

|

JP2–HI |

|

Pull-up voltage source |

|

|

|

JP2–LEDPWR |

|

LED Pull-up power line |

|

|

|

JP3–VREF |

|

IC reference voltage VREF |

|

|

|

JP3–VPULLUP |

|

Pull-up voltage source |

|

|

|

JP3–EXT |

|

External voltage supply from J2 |

|

|

|

JP4–VCC |

|

Pull-up voltage source of ACDRV and BATDRV LED logic circuit |

|

|

|

JP4–VCOM |

|

Q7 and Q11 common source |

|

|

|

JP5–HI |

|

Pull-up voltage source |

|

|

|

JP5–CHGEN |

|

Charge enable |

|

|

|

1.41.4 Controls and Key Parameters Setting

Table 2. Controls and Key Parameters Setting

Jack |

|

Description |

Factory Setting |

|

|

|

|

||

|

TTC setting |

|

||

JP1 |

1-2 |

: Connect TTC to GROUND (Disable termination and the safety timer) |

Jumper on 2-3 (TTC and VPULLUP) |

|

2-3 |

: Connect TTC to VPULLUP (Allow termination, but disable the safety time) |

|||

|

|

|||

|

2 floating: Allow termination, CTTC sets the safety timer |

|

||

|

|

|

||

JP2 |

The pull-up power source supplies the LEDs when on. |

Jumper On |

||

LED has no power source when off. |

||||

|

|

|||

|

|

|

||

|

VPULLUP setting |

Jumper On 1-2 (VPULLUP and |

||

JP3 |

1-2 |

: Connect VPULLUP to VREF |

||

VREF) |

||||

|

2-3 |

: Connect VPULLUP to VEXT |

||

|

|

|||

|

|

|

||

JP4 |

The pull-up voltage source of ACDRV and BATDRV LED logic circuit. |

Jumper on |

||

|

|

|

||

|

CHGEN setting |

|

||

JP5 |

Jumper on: CHGEN to VPULLUP |

Jumper Off |

||

|

Jumper off: CHGEN is set to low by pull down resistor. |

|

||

|

|

|

|

|

1.5Recommended Operating Conditions

Table 3. Recommended Operating Conditions

Symbol |

Description |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

24(617) |

|

Supply voltage, VIN |

Input voltage from ac adapter input |

5 |

24 |

28 |

V |

|

|

|

|

(610/616/63x) |

|

|

|

|

|

|

|

Battery voltage, VBAT |

Voltage applied at VBAT terminal of J5 |

2.1 (61x) |

21 (61x) |

|

V |

1.8 (63x) |

18 (63x) |

|

|||

|

|

|

|

||

|

|

|

|

|

|

Supply current, IAC |

Maximum input current from ac adapter |

0 |

|

4.5 |

A |

input |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

Charge current, Ichrg |

Battery charge current |

2 |

3 |

8 |

A |

|

|

|

|

|

|

Operating junction |

|

0 |

|

125 |

°C |

temperature range, TJ |

|

|

|||

|

|

|

|

|

The bq2461x/bq2463x EVM board requires a regulated supply approximately 0.5 V minimum above the regulated voltage of the battery pack to a maximum input voltage of 28 VDC.

SLUU396A –January 2010 –Revised July 2010 |

bq2461x/bq2463x EVM (HPA422) Multi-Cell Synchronous Switch-Mode Charger |

3 |

Copyright © 2010, Texas Instruments Incorporated

Test Summary |

www.ti.com |

R25 and R28 can be changed to regulate output.

VBAT = 2.1V × [1+ R25/R28]; for bq2461x;

VBAT = 1.8V × [1+ R25/R28]; for bq2463x;

Adjust the input voltage as required. Output set to operate at 21V (bq2461x) or 18V (bq2463x) from the factory.

2 Test Summary

2.1Definitions

This procedure details how to configure the HPA422 evaluation board. On the test procedure the following naming conventions are followed. See the HPA422 schematic for details.

VXXX: |

External voltage supply name (VADP, VBT, VSBT) |

LOADW: |

External load name (LOADR, LOADI) |

V(TPyyy): |

Voltage at internal test point TPyyy. For example, V(TP12) means the voltage at TP12 |

V(Jxx): |

Voltage at jack terminal Jxx. |

V(TP(XXX)): |

Voltage at test point "XXX". For example, V(ACDET) means the voltage at the test |

|

point which is marked as "ACDET". |

V(XXX, YYY): |

Voltage across point XXX and YYY. |

I(JXX(YYY)): |

Current going out from the YYY terminal of jack XX. |

Jxx(BBB): |

Terminal or pin BBB of jack xx |

Jxx ON: |

Internal jumper Jxx terminals are shorted |

Jxx OFF: |

Internal jumper Jxx terminals are open |

Jxx (-YY-) ON: |

Internal jumper Jxx adjacent terminals marked as "YY" are shorted |

Measure:→ A,B |

Check specified parameters A, B. If measured values are not within specified limits the |

|

unit under test has failed. |

Observe → A,B |

Observe if A, B occur. If they do not occur, the unit under test has failed. |

Assembly drawings have location for jumpers, test points and individual components.

2.2Equipment

2.2.1Power Supplies

Power Supply #1 (PS#1): a power supply capable of supplying 30-V at 5-A is required.

Power Supply #2 (PS#2): a power supply capable of supplying 5-V at 1-A is required.

Power Supply #3 (PS#3): a power supply capable of supplying 5-V at 1-A is required.

2.2.2LOAD #1

A 30V (or above), 5A (or above) electronic load that can operate at constant current mode

2.2.3LOAD #2

A Kepco bipolar operational power supply/amplifier, 0 ±30V (or above), 0 ±6A (or above).

2.2.4Oscilloscope

Tektronix TDS3054 scope or equivalent, 10X voltage probe.

4 |

bq2461x/bq2463x EVM (HPA422) Multi-Cell Synchronous Switch-Mode Charger |

SLUU396A –January 2010 –Revised July 2010 |

Copyright © 2010, Texas Instruments Incorporated

www.ti.com |

Test Summary |

2.2.5METERS

Seven Fluke 75 multimeters, (equivalent or better)

Or: Four equivalent voltage meters and three equivalent current meters.

The current meters must be capable of measuring 5A+ current

2.3Equipment Setup

1.Set the power supply #1 for 0V ± 100mVDC, 5.0 ± 0.1A current limit and then turn off supply.

2.Connect the output of power supply #1 in series with a current meter (multimeter) to J1 (VIN, GND).

3.Connect a voltage meter across J1 (VIN, GND).

4.Set the power supply #2 for 0V ± 100mVDC, 1.0 ± 0.1A current limit and then turn off supply.

5.Connect the output of the power supply #2 to J4 and J5 (TS, GND).

6.Connect Load #1 in series with a current meter to J5 (SYS, GND). Turn off Load #1

7.Connect Load #2 in series with a current meter to J5 (BAT, GND). Turn off Load #2.

8.Connect a voltage meter across J5 (BAT, GND).

9.Connect an oscilloscope's probe across J5 (BAT, GND)

10.Connect a voltage meter across J5 (SYS, GND).

11.JP1 (TTC and HI): ON, JP2: ON, JP3 (VPULLUP and VREF): ON, JP4: ON, JP5: OFF.

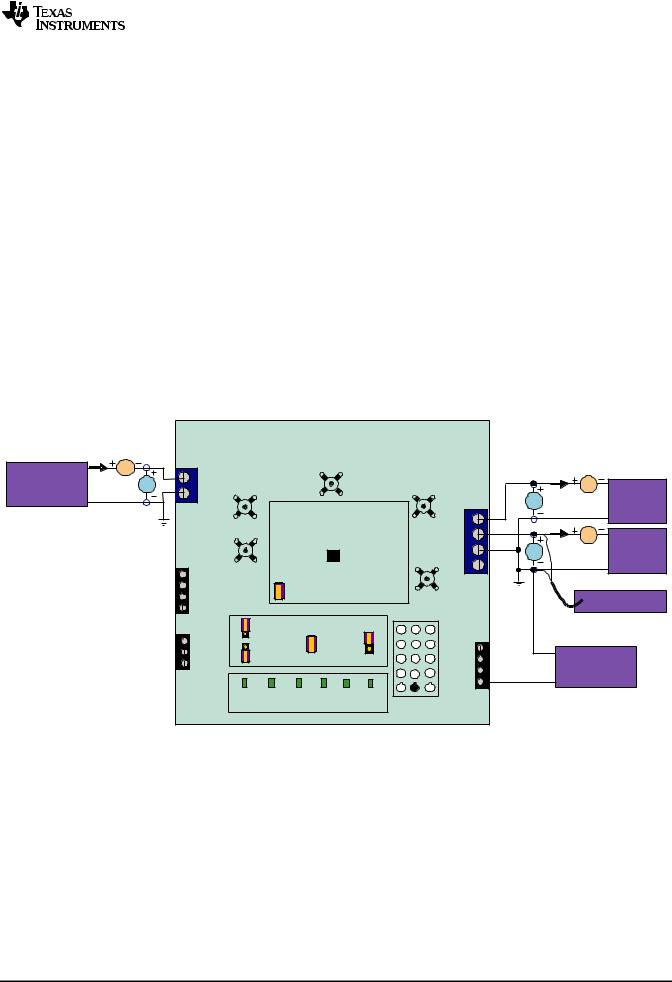

After the above steps, the test setup for HPA422 is shown in Figure 1.

Power supply #1

|

bq24610/616/617/30 EVM |

|

|

|

|

|

|

||

|

J1 |

HPA422 |

|

|

|

|

|

|

|

|

|

PH |

|

|

|

|

|

|

|

|

I |

|

|

|

|

|

Isys |

|

|

Iin |

ACPWR |

TP1 |

|

TP12 |

|

|

|

|

|

|

|

SYS |

|

|

|

|

|

||

V |

ACPWR |

|

|

|

|

I |

Load |

||

|

|

|

|

|

|

|

|||

|

PGND |

|

|

|

|

|

|

|

|

|

|

|

|

|

J5 |

V |

|

|

#1 |

|

|

|

|

|

SYS |

|

|

|

|

|

|

TP2 |

|

|

BAT |

|

|

I |

|

|

|

U1 |

|

|

|

|

Load |

||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

V |

Ibat |

|

|

|

J3 |

|

|

TP9 |

PGND |

|

#2 |

||

|

VCC |

|

|

|

|

|

|

||

|

ACSET |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ISET1 |

|

JP4 |

|

|

|

|

|

|

|

ISET2 |

|

|

|

|

|

|

|

|

|

|

|

VBAT |

|

|

|

Oscilloscope |

||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

GND |

|

APPLICATION CIRCUIT |

|

|

|

|

I |

|

|

|

|

|

|

|

|

|

||

|

|

VREF |

|

|

|

|

|

|

|

|

J2 |

JP3 |

|

J4 |

|

|

|

|

|

|

VEXT |

|

|

|

|

|

|

||

|

VEXT |

HI |

|

|

|

|

|

|

|

|

GND |

|

|

PG |

|

|

|

|

|

|

L |

JP1 |

|

|

|

|

Power |

|

|

|

TTC |

O |

JP2 |

JP5 |

STAT1 |

|

|

|

|

|

|

|

|

|

VREF |

|

sup ply #2 |

|

|

|

|

|

|

|

TS |

|

|

|

|

/ACDRV |

/BATDRV |

CE |

PG |

/STAT1 |

/STAT2 |

Figure 1. Original Test Setup for HPA422 (bq2461x/bq2463x EVM)

SLUU396A –January 2010 –Revised July 2010 |

bq2461x/bq2463x EVM (HPA422) Multi-Cell Synchronous Switch-Mode Charger |

5 |

Copyright © 2010, Texas Instruments Incorporated

Test Summary |

www.ti.com |

2.4Procedure

2.4.1AC Adapter Detection Threshold

1.Make sure EQUIPMENT SETUP steps are followed. Turn on PS#2.

2.Turn on PS#1

Measure → V(J5(SYS)) = 0 ± 500mV Measure → V(TP(VREF)) = 0V ± 1000mV Measure → V(TP(REGN)) = 0V ± 500mV

3.Increase the output voltage on PS#1 until D5 (PG) on but do not exceed 5V. Set the power supply #2 to 1.8V ± 100mVDC

Measure → V(J1(VIN)) = 4.5V ± 0.5V Measure → V(J5(SYS)) = 4.5V ± 0.5V Measure → V(TP(VREF)) = 3.3V ± 200mV Measure → V(TP(REGN)) = 0V ± 500mV Measure → D4 (/ACDRV) on, D5 (PG) on

2.4.2Charger Regulation Voltage

1.Increase the voltage of PS#1 until V(J1(VIN)) = 24V ± 0.1V. Measure → V(J5(BAT, GND)) = 0V ± 1V

2.Put JP5 on (Enable the charging). Observe → D3 (CE) on.

Measure → Peak V(J5(BAT)) = 21.0V ± 1V (bq2461x) Peak V(J5(BAT)) = 18.0V ± 1V (bq2463x)

Measure → V(TP(REGN)) = 6V ± 500mV

2.4.3Charge Current and AC Current Regultion (DPM)

1.Take off JP5 (Disable the charging).

2.Connect the Load #2 in series with a current meter (multimeter) to J5 (BAT, GND). Make sure a voltage meter is connected across J5 (BAT, GND). Turn on the Load #2. Set the output voltage to 12V (bq2461x) or 2V (bq2463x).

3.Connect the output of the Load #1 in series with a current meter (multimeter) to J5 (SYS, GND). Make sure a voltage meter is connected across J5 (SYS, GND). Turn on the power of the Load #1. Set the load current to 3.0A ± 50mA but disable the load #1. The setup is now like Figure 1 for HPA422. Make sure Ibat = 0A ± 10mA and Isys = 0A ± 10mA.

4.Put JP5 on (Enable the charging). Observe → D3 (CE) on

Measure → Ibat = 300mA ± 200mA (bq2461x) Ibat = 125mA ± 60mA (bq2463x)

Observe → D7 (STAT1) on; D8 (STAT2) off.

5.Set the Load #2 output voltage to 16.5V. Measure → Ibat = 3000mA ± 300mA Observe → D7 (STAT1) on; D8 (STAT2) off.

6.Enable the output of the Load #1

Measure → Isys = 3000mA ± 200mA, Ibat = 1400mA ± 500mA, Iin = 4000mA ± 500mA

7.Turn off the Load #1.

Measure → Isys = 0 ± 100mA, Ibat = 3000mA ± 300mA.

8.Increase the Load #2 output voltage from 16.5V to 22V (61x) or 19V (63x). Measure → Isys = 0 ± 100mA, Ibat = 0mA ± 100mA.

Observe → D7 (STAT1) off; D8 (STAT2) on.

9.Decrease the Load #2 output voltage back to 16.5V. Observe → D7 (STAT1) on; D8 (STAT2) off.

6 |

bq2461x/bq2463x EVM (HPA422) Multi-Cell Synchronous Switch-Mode Charger |

SLUU396A –January 2010 –Revised July 2010 |

Copyright © 2010, Texas Instruments Incorporated

www.ti.com |

PCB Layout Guideline |

2.4.4Charger Cut-Off by Thermistor

1.Slowly increase the output voltage of PS2 until Ibat = 0 ± 10mA. Measure → V(J4(TS)) = 2.44V ± 200mV

Observe → D7 (STAT1) off; D8 (STAT2) off.

2.Slowly decrease the output voltage of PS2 to 1.4V ± 0.1V. Measure → V(J4(TS)) = 1.4V ± 100mV

Measure → Ibat = 3000mA ± 300mA (bq24610/617) Ibat = 0mA ± 100mA (bq24616)

Ibat = 375mA ± 150mA (bq2463x)

Observe → D7 (STAT1) on; D8 (STAT2) off (bq24610/617/630) Observe → D7 (STAT1) off; D8 (STAT2) off (bq24616)

3.Slowly decrease the output voltage of PS2.

Charge will resume. Continue to decrease the output voltage of PS2 slowly until Ibat = 0 ±10mA. Measure → V(J4(TS)) = 1.14V ± 200mV

Observe → D7 (STAT1) off; D8 (STAT2) off.

4.Slowly increase the output voltage of PS2 to 1.8V ± 100mV. Measure → Ibat = 3000mA ± 200mA

Observe → D7 (STAT1) on; D8 (STAT2) off.

2.4.5Power Path Selection

1.Take off JP5 (Disable the charging) Observe → D3 (CE) off; D7 (STAT1) off.

2.Set JP3 Jumper On 2-3 (VPULLUP and VEXT). Connect the output of the power supply #3 to J2(VEXT, GND). Set the power supply #3 for 3.3V ± 200mVDC, 1.0 ± 0.1A current limit.

3.Set the Load #2 output voltage to 16.5V ± 500mV.

4.Measure → V(J5(SYS)) = 24V ± 1V (adapter connected to system)

Observe → D4 (ACDRV) on, D6 (BATDRV) off, D5 (PG) on, D7 (STAT1) off, D8 (STAT2) off.

5.Turn off PS#1.

6.Measure → V(J5(SYS)) = 16.5V ± 0.5V (battery connected to system)

7.Observe → D4 (ACDRV) off, D6 (BATDRV) on, D5 (PG) off, D7 (STAT1) off, D8 (STAT2) off.

8.Turn off power supply #2 and #3. Set JP3 on 1-2 (VPULLUP and VREF).

3PCB Layout Guideline

1.It is critical that the exposed power pad on the backside of the bq2461x/bq2463x package be soldered to the PCB ground. Make sure there are sufficient thermal vias right underneath the IC, connecting to the ground plane on the other layers.

2.The control stage and the power stage should be routed separately. At each layer, the signal ground and the power ground are connected only at the power pad.

3.AC current sense resistor must be connected to ACP and ACN with a Kelvin contact. The area of this loop must be minimized. The decoupling capacitors for these pins should be placed as close to the IC as possible.

4.Charge current sense resistor must be connected to SRP, SRN with a Kelvin contact. The area of this loop must be minimized. The decoupling capacitors for these pins should be placed as close to the IC as possible.

5.Decoupling capacitors for DCIN, VREF, VCC, REGN should make the interconnections to the IC as short as possible.

6.Decoupling capacitors for BAT must be placed close to the corresponding IC pins and make the interconnections to the IC as short as possible.

7.Decoupling capacitor(s) for the charger input must be placed close to top buck FET's drain and bottom buck FET’s source.

SLUU396A –January 2010 –Revised July 2010 |

bq2461x/bq2463x EVM (HPA422) Multi-Cell Synchronous Switch-Mode Charger |

7 |

Copyright © 2010, Texas Instruments Incorporated

Loading...

Loading...