Texas Instruments TMS320x28xx, 28xxx User Manual

TMS320x28xx, 28xxx Enhanced Pulse Width

Modulator (ePWM) Module

Reference Guide

Literature Number: SPRU791D

November 2004–Revised October 2007

2 |

SPRU791D–November 2004–Revised October 2007 |

Submit Documentation Feedback

Contents

Preface ............................................................................................................................... |

|

|

|

9 |

|

1 |

Introduction |

............................................................................................................. |

|

13 |

|

|

1.1 |

Introduction......................................................................................................... |

|

14 |

|

|

1.2 |

Submodule Overview ............................................................................................. |

|

14 |

|

|

1.3 |

Register Mapping.................................................................................................. |

|

17 |

|

2 |

ePWM Submodules ................................................................................................... |

|

19 |

||

|

2.1 |

Overview............................................................................................................ |

|

20 |

|

|

2.2 |

Time-Base (TB) Submodule ..................................................................................... |

|

23 |

|

|

|

2.2.1 Purpose of the Time-Base Submodule................................................................ |

|

23 |

|

|

|

2.2.2 Controlling and Monitoring the Time-base Submodule.............................................. |

|

24 |

|

|

|

2.2.3 Calculating PWM Period and Frequency.............................................................. |

|

25 |

|

|

|

2.2.4 Phase Locking the Time-Base Clocks of Multiple ePWM Modules................................ |

|

30 |

|

|

|

2.2.5 Time-base Counter Modes and Timing Waveforms ................................................. |

|

30 |

|

|

2.3 |

Counter-Compare (CC) Submodule ............................................................................ |

|

32 |

|

|

|

2.3.1 Purpose of the Counter-Compare Submodule ....................................................... |

|

33 |

|

|

|

2.3.2 Controlling and Monitoring the Counter-Compare Submodule..................................... |

|

33 |

|

|

|

2.3.3 Operational Highlights for the Counter-Compare Submodule...................................... |

|

34 |

|

|

|

2.3.4 Count Mode Timing Waveforms ....................................................................... |

|

34 |

|

|

2.4 |

Action-Qualifier (AQ) Submodule ............................................................................... |

|

37 |

|

|

|

2.4.1 Purpose of the Action-Qualifier Submodule .......................................................... |

|

37 |

|

|

|

2.4.2 Action-Qualifier Submodule Control and Status Register Definitions ............................. |

|

37 |

|

|

|

2.4.3 |

Action-Qualifier Event Priority .......................................................................... |

|

40 |

|

|

2.4.4 Waveforms for Common Configurations .............................................................. |

|

41 |

|

|

2.5 |

Dead-Band Generator (DB) Submodule ....................................................................... |

|

50 |

|

|

|

2.5.1 Purpose of the Dead-Band Submodule ............................................................... |

|

50 |

|

|

|

2.5.2 Controlling and Monitoring the Dead-Band Submodule............................................. |

|

50 |

|

|

|

2.5.3 Operational Highlights for the Dead-Band Submodule.............................................. |

|

51 |

|

|

2.6 |

PWM-Chopper (PC) Submodule ................................................................................ |

|

55 |

|

|

|

2.6.1 Purpose of the PWM-Chopper Submodule ........................................................... |

|

55 |

|

|

|

2.6.2 Controlling the PWM-Chopper Submodule ........................................................... |

|

55 |

|

|

|

2.6.3 Operational Highlights for the PWM-Chopper Submodule.......................................... |

|

55 |

|

|

|

2.6.4 |

Waveforms ................................................................................................ |

|

56 |

|

2.7 |

Trip-Zone (TZ) Submodule....................................................................................... |

|

59 |

|

|

|

2.7.1 Purpose of the Trip-Zone Submodule ................................................................. |

|

59 |

|

|

|

2.7.2 Controlling and Monitoring the Trip-Zone Submodule............................................... |

|

60 |

|

|

|

2.7.3 Operational Highlights for the Trip-Zone Submodule................................................ |

|

60 |

|

|

|

2.7.4 Generating Trip Event Interrupts ....................................................................... |

|

62 |

|

|

2.8 |

Event-Trigger (ET) Submodule .................................................................................. |

|

63 |

|

|

|

2.8.1 Operational Overview of the Event-Trigger Submodule............................................. |

|

64 |

|

3 |

Applications to Power Topologies .............................................................................. |

|

69 |

||

|

3.1 |

Overview of Multiple Modules ................................................................................... |

|

70 |

|

|

3.2 |

Key Configuration Capabilities................................................................................... |

|

70 |

|

|

3.3 |

Controlling Multiple Buck Converters With Independent Frequencies ..................................... |

|

71 |

|

SPRU791D–November 2004–Revised October 2007 |

Contents |

3 |

|||

Submit Documentation Feedback

|

3.4 |

Controlling Multiple Buck Converters With Same Frequencies ............................................. |

75 |

|

3.5 |

Controlling Multiple Half H-Bridge (HHB) Converters ........................................................ |

78 |

|

3.6 |

Controlling Dual 3-Phase Inverters for Motors (ACI and PMSM) ........................................... |

80 |

|

3.7 |

Practical Applications Using Phase Control Between PWM Modules...................................... |

84 |

|

3.8 |

Controlling a 3-Phase Interleaved DC/DC Converter......................................................... |

85 |

|

3.9 |

Controlling Zero Voltage Switched Full Bridge (ZVSFB) Converter ........................................ |

89 |

4 |

Registers ................................................................................................................. |

93 |

|

|

4.1 |

Time-Base Submodule Registers ............................................................................... |

94 |

|

4.2 |

Counter-Compare Submodule Registers....................................................................... |

97 |

|

4.3 |

Action-Qualifier Submodule Registers.......................................................................... |

99 |

|

4.4 |

Dead-Band Submodule Registers ............................................................................. |

103 |

|

4.5 |

PWM-Chopper Submodule Control Register................................................................. |

105 |

|

4.6 |

Trip-Zone Submodule Control and Status Registers........................................................ |

106 |

|

4.7 |

Event-Trigger Submodule Registers .......................................................................... |

110 |

|

4.8 |

Proper Interrupt Initialization Procedure ...................................................................... |

115 |

A |

Revision History ..................................................................................................... |

117 |

|

4 |

Contents |

SPRU791D–November 2004–Revised October 2007 |

Submit Documentation Feedback

List of Figures

1-1 |

Multiple ePWM Modules................................................................................................... |

|

15 |

1-2 |

Submodules and Signal Connections for an ePWM Module ......................................................... |

|

16 |

1-3 |

ePWM Submodules and Critical Internal Signal Interconnects ...................................................... |

|

17 |

2-1 |

Time-Base Submodule Block Diagram .................................................................................. |

|

23 |

2-2 |

Time-Base Submodule Signals and Registers ......................................................................... |

|

24 |

2-3 |

Time-Base Frequency and Period ....................................................................................... |

|

26 |

2-4 |

Time-Base Counter Synchronization Scheme 1 ....................................................................... |

|

27 |

2-5 |

Time-Base Counter Synchronization Scheme 2 ....................................................................... |

|

28 |

2-6 |

Time-Base Counter Synchronization Scheme 3 ....................................................................... |

|

29 |

2-7 |

Time-Base Up-Count Mode Waveforms ................................................................................ |

|

30 |

2-8 |

Time-Base Down-Count Mode Waveforms ............................................................................. |

|

31 |

2-9 |

Time-Base Up-Down-Count Waveforms, TBCTL[PHSDIR = 0] Count Down On Synchronization Event...... |

31 |

|

2-10 |

Time-Base Up-Down Count Waveforms, TBCTL[PHSDIR = 1] Count Up On Synchronization Event ......... |

32 |

|

2-11 |

Counter-Compare Submodule............................................................................................ |

|

32 |

2-12 |

Detailed View of the Counter-Compare Submodule................................................................... |

|

33 |

2-13 |

Counter-Compare Event Waveforms in Up-Count Mode ............................................................. |

|

35 |

2-14 |

Counter-Compare Events in Down-Count Mode....................................................................... |

|

35 |

2-15 |

Counter-Compare Events In Up-Down-Count Mode, TBCTL[PHSDIR = 0] Count Down On |

|

|

|

Synchronization Event .................................................................................................... |

|

36 |

2-16 |

Counter-Compare Events In Up-Down-Count Mode, TBCTL[PHSDIR = 1] Count Up On Synchronization |

|

|

|

Event ........................................................................................................................ |

|

36 |

2-17 |

Action-Qualifier Submodule ............................................................................................... |

|

37 |

2-18 |

Action-Qualifier Submodule Inputs and Outputs ....................................................................... |

|

38 |

2-19 |

Possible Action-Qualifier Actions for EPWMxA and EPWMxB Outputs ............................................ |

|

39 |

2-20 |

Up-Down-Count Mode Symmetrical Waveform ........................................................................ |

|

42 |

2-21 |

Up, Single Edge Asymmetric Waveform, With Independent Modulation on EPWMxA and |

|

|

|

EPWMxB—Active High.................................................................................................... |

|

43 |

2-22 |

Up, Single Edge Asymmetric Waveform With Independent Modulation on EPWMxA and |

|

|

|

EPWMxB—Active Low .................................................................................................... |

|

44 |

2-23 |

Up-Count, Pulse Placement Asymmetric Waveform With Independent Modulation on EPWMxA .............. |

45 |

|

2-24 |

Up-Down-Count, Dual Edge Symmetric Waveform, With Independent Modulation on EPWMxA and |

|

|

|

EPWMxB — Active Low................................................................................................... |

|

47 |

2-25 |

Up-Down-Count, Dual Edge Symmetric Waveform, With Independent Modulation on EPWMxA and |

|

|

|

EPWMxB — Complementary ............................................................................................. |

|

48 |

2-26 |

Up-Down-Count, Dual Edge Asymmetric Waveform, With Independent Modulation on EPWMxA—Active |

|

|

|

Low........................................................................................................................... |

|

49 |

2-27 |

Dead_Band Submodule ................................................................................................... |

|

50 |

2-28 |

Configuration Options for the Dead-Band Submodule ................................................................ |

|

51 |

2-29 |

Dead-Band Waveforms for Typical Cases (0% < Duty < 100%)..................................................... |

|

53 |

2-30 |

PWM-Chopper Submodule ............................................................................................... |

|

55 |

2-31 |

PWM-Chopper Submodule Operational Details........................................................................ |

|

56 |

2-32 |

Simple PWM-Chopper Submodule Waveforms Showing Chopping Action Only.................................. |

|

56 |

2-33 |

PWM-Chopper Submodule Waveforms Showing the First Pulse and Subsequent Sustaining Pulses ......... |

57 |

|

2-34 |

PWM-Chopper Submodule Waveforms Showing the Pulse Width (Duty Cycle) Control of Sustaining |

|

|

|

Pulses........................................................................................................................ |

|

58 |

2-35 |

Trip-Zone Submodule...................................................................................................... |

|

59 |

2-36 |

Trip-Zone Submodule Mode Control Logic ............................................................................. |

|

62 |

2-37 |

Trip-Zone Submodule Interrupt Logic.................................................................................... |

|

63 |

2-38 |

Event-Trigger Submodule ................................................................................................. |

|

63 |

2-39 |

Event-Trigger Submodule Inter-Connectivity of ADC Start of Conversion and Interrupt Signals................ |

64 |

|

2-40 |

Event-Trigger Submodule Showing Event Inputs and Prescaled Outputs.......................................... |

|

65 |

2-41 |

Event-Trigger Interrupt Generator........................................................................................ |

|

66 |

2-42 |

Event-Trigger SOCA Pulse Generator .................................................................................. |

|

67 |

SPRU791D–November 2004–Revised October 2007 |

List of Figures |

5 |

|

Submit Documentation Feedback

2-43 |

Event-Trigger SOCB Pulse Generator .................................................................................. |

67 |

3-1 |

Simplified ePWM Module.................................................................................................. |

70 |

3-2 |

EPWM1 Configured as a Typical Master, EPWM2 Configured as a Slave ........................................ |

71 |

3-3 |

Control of Four Buck Stages. Here FPWM1¹ FPWM2¹ FPWM3¹ FPWM4 .................................................. |

72 |

3-4 |

Buck Waveforms for Figure 3-3 (Note: Only three bucks shown here) ............................................. |

73 |

3-5 |

Control of Four Buck Stages. (Note: FPWM2 = N x FPWM1)............................................................. |

75 |

3-6 |

Buck Waveforms for Figure 3-5 (Note: FPWM2 = FPWM1)) .............................................................. |

76 |

3-7 |

Control of Two Half-H Bridge Stages (FPWM2 = N x FPWM1) ........................................................... |

78 |

3-8 |

Half-H Bridge Waveforms for Figure 3-7 (Note: Here FPWM2 = FPWM1 ).............................................. |

79 |

3-9 |

Control of Dual 3-Phase Inverter Stages as Is Commonly Used in Motor Control ................................ |

81 |

3-10 |

3-Phase Inverter Waveforms for Figure 3-9 (Only One Inverter Shown) ........................................... |

82 |

3-11 |

Configuring Two PWM Modules for Phase Control.................................................................... |

84 |

3-12 |

Timing Waveforms Associated With Phase Control Between 2 Modules .......................................... |

85 |

3-13 |

Control of a 3-Phase Interleaved DC/DC Converter................................................................... |

86 |

3-14 |

3-Phase Interleaved DC/DC Converter Waveforms for Figure 3-13 ................................................ |

87 |

3-15 |

Controlling a Full-H Bridge Stage (FPWM2 = FPWM1)..................................................................... |

89 |

3-16 |

ZVS Full-H Bridge Waveforms ........................................................................................... |

90 |

4-1 |

Time-Base Period Register (TBPRD).................................................................................... |

94 |

4-2 |

Time-Base Phase Register (TBPHS).................................................................................... |

94 |

4-3 |

Time-Base Counter Register (TBCTR) .................................................................................. |

94 |

4-4 |

Time-Base Control Register (TBCTL) ................................................................................... |

95 |

4-5 |

Time-Base Status Register (TBSTS) .................................................................................... |

97 |

4-6 |

Counter-Compare A Register (CMPA) .................................................................................. |

97 |

4-7 |

Counter-Compare B Register (CMPB) .................................................................................. |

98 |

4-8 |

Counter-Compare Control Register (CMPCTL) ........................................................................ |

99 |

4-9 |

Action-Qualifier Output A Control Register (AQCTLA)............................................................... |

100 |

4-10 |

Action-Qualifier Output B Control Register (AQCTLB)............................................................... |

101 |

4-11 |

Action-Qualifier Software Force Register (AQSFRC) ................................................................ |

102 |

4-12 |

Action-Qualifier Continuous Software Force Register (AQCSFRC)................................................ |

102 |

4-13 |

Dead-Band Generator Control Register (DBCTL).................................................................... |

103 |

4-14 |

Dead-Band Generator Rising Edge Delay Register (DBRED)...................................................... |

105 |

4-15 |

Dead-Band Generator Falling Edge Delay Register (DBFED) ..................................................... |

105 |

4-16 |

PWM-Chopper Control Register (PCCTL)............................................................................. |

105 |

4-17 |

Trip-Zone Select Register (TZSEL) .................................................................................... |

107 |

4-18 |

Trip-Zone Control Register (TZCTL) ................................................................................... |

108 |

4-19 |

Trip-Zone Enable Interrupt Register (TZEINT)........................................................................ |

108 |

4-20 |

Trip-Zone Flag Register (TZFLG)....................................................................................... |

109 |

4-21 |

Trip-Zone Clear Register (TZCLR) ..................................................................................... |

110 |

4-22 |

Trip-Zone Force Register (TZFRC)..................................................................................... |

110 |

4-23 |

Event-Trigger Selection Register (ETSEL) ............................................................................ |

111 |

4-24 |

Event-Trigger Prescale Register (ETPS) .............................................................................. |

112 |

4-25 |

Event-Trigger Flag Register (ETFLG).................................................................................. |

113 |

4-26 |

Event-Trigger Clear Register (ETCLR) ................................................................................ |

114 |

4-27 |

Event-Trigger Force Register (ETFRC)................................................................................ |

115 |

6 |

List of Figures |

SPRU791D–November 2004–Revised October 2007 |

Submit Documentation Feedback

List of Tables

1-1 |

ePWM Module Control and Status Register Set Grouped by Submodule.......................................... |

|

18 |

2-1 |

Submodule Configuration Parameters................................................................................... |

|

20 |

2-2 |

Time-Base Submodule Registers ........................................................................................ |

|

24 |

2-3 |

Key Time-Base Signals.................................................................................................... |

|

25 |

2-4 |

Counter-Compare Submodule Registers ............................................................................... |

|

33 |

2-5 |

Counter-Compare Submodule Key Signals............................................................................. |

|

34 |

2-6 |

Action-Qualifier Submodule Registers................................................................................... |

|

37 |

2-7 |

Action-Qualifier Submodule Possible Input Events .................................................................... |

|

38 |

2-8 |

Action-Qualifier Event Priority for Up-Down-Count Mode............................................................. |

|

40 |

2-9 |

Action-Qualifier Event Priority for Up-Count Mode..................................................................... |

|

40 |

2-10 |

Action-Qualifier Event Priority for Down-Count Mode ................................................................. |

|

40 |

2-11 |

Behavior if CMPA/CMPB is Greater than the Period .................................................................. |

|

41 |

2-12 |

Dead-Band Generator Submodule Registers........................................................................... |

|

50 |

2-13 |

Classical Dead-Band Operating Modes ................................................................................ |

|

52 |

2-14 |

Dead-Band Delay Values in μS as a Function of DBFED and DBRED ............................................ |

|

54 |

2-15 |

PWM-Chopper Submodule Registers ................................................................................... |

|

55 |

2-16 |

Possible Pulse Width Values for SYSCLKOUT = 100 MHz .......................................................... |

|

57 |

2-17 |

Trip-Zone Submodule Registers ......................................................................................... |

|

60 |

2-18 |

Possible Actions On a Trip Event ........................................................................................ |

|

61 |

2-19 |

Event-Trigger Submodule Registers .................................................................................... |

|

65 |

4-1 |

Time-Base Period Register (TBPRD) Field Descriptions ............................................................. |

|

94 |

4-2 |

Time-Base Phase Register (TBPHS) Field Descriptions.............................................................. |

|

94 |

4-3 |

Time-Base Counter Register (TBCTR) Field Descriptions............................................................ |

|

94 |

4-4 |

Time-Base Control Register (TBCTL) Field Descriptions ............................................................. |

|

95 |

4-5 |

Time-Base Status Register (TBSTS) Field Descriptions.............................................................. |

|

97 |

4-6 |

Counter-Compare A Register (CMPA) Field Descriptions ............................................................ |

|

98 |

4-7 |

Counter-Compare B Register (CMPB) Field Descriptions ............................................................ |

|

98 |

4-8 |

Counter-Compare Control Register (CMPCTL) Field Descriptions ................................................. |

|

99 |

4-9 |

Action-Qualifier Output A Control Register (AQCTLA) Field Descriptions ....................................... |

|

100 |

4-10 |

Action-Qualifier Output B Control Register (AQCTLB) Field Descriptions ....................................... |

|

101 |

4-11 |

Action-Qualifier Software Force Register (AQSFRC) Field Descriptions.......................................... |

|

102 |

4-12 |

Action-qualifier Continuous Software Force Register (AQCSFRC) Field Descriptions.......................... |

|

103 |

4-13 |

Dead-Band Generator Control Register (DBCTL) Field Descriptions.............................................. |

|

104 |

4-14 |

Dead-Band Generator Rising Edge Delay Register (DBRED) Field Descriptions ............................... |

|

105 |

4-15 |

Dead-Band Generator Falling Edge Delay Register (DBFED) Field Descriptions ............................... |

|

105 |

4-16 |

PWM-Chopper Control Register (PCCTL) Bit Descriptions ........................................................ |

|

105 |

4-17 |

Trip-Zone Submodule Select Register (TZSEL) Field Descriptions ............................................... |

|

107 |

4-18 |

Trip-Zone Control Register (TZCTL) Field Descriptions ............................................................. |

|

108 |

4-19 |

Trip-Zone Enable Interrupt Register (TZEINT) Field Descriptions ................................................. |

|

108 |

4-20 |

Trip-Zone Flag Register (TZFLG) Field Descriptions ................................................................ |

|

109 |

4-21 |

Trip-Zone Clear Register (TZCLR) Field Descriptions .............................................................. |

|

110 |

4-22 |

Trip-Zone Force Register (TZFRC) Field Descriptions .............................................................. |

|

110 |

4-23 |

Event-Trigger Selection Register (ETSEL) Field Descriptions ..................................................... |

|

111 |

4-24 |

Event-Trigger Prescale Register (ETPS) Field Descriptions ....................................................... |

|

112 |

4-25 |

Event-Trigger Flag Register (ETFLG) Field Descriptions ........................................................... |

|

114 |

4-26 |

Event-Trigger Clear Register (ETCLR) Field Descriptions .......................................................... |

|

114 |

4-27 |

Event-Trigger Force Register (ETFRC) Field Descriptions ......................................................... |

|

115 |

A-1 |

Changes for Revision D.................................................................................................. |

|

117 |

SPRU791D–November 2004–Revised October 2007 |

List of Tables |

7 |

|

Submit Documentation Feedback

8 |

List of Tables |

SPRU791D–November 2004–Revised October 2007 |

Submit Documentation Feedback

Preface

SPRU791D–November 2004–Revised October 2007

Read This First

This guide describes the Enhanced Pulse Width Modulator (ePWM) Module. It includes an overview of the module and information about each of the sub-modules:

∙Time-Base Module

∙Counter Compare Module

∙Action Qualifier Module

∙Dead-Band Generator Module

∙PWM Chopper (PC) Module

∙Trip Zone Module

∙Event Trigger Module

Related Documentation From Texas Instruments

The following books describe the TMS320x280x and related support tools that are available on the TI website:

Data Manuals—

SPRS230— TMS320F2809, F2808, F2806, F2802, F2801, C2802, C2801, and F2801x DSPs Data Manual contains the pinout, signal descriptions, as well as electrical and timing specifications for the F280x devices.

SPRS357— TMS320F28044 Digital Signal Processor Data Manual contains the pinout, signal descriptions, as well as electrical and timing specifications for the F28044 device.

CPU User's Guides—

SPRU430— TMS320C28x DSP CPU and Instruction Set Reference Guide describes the central processing unit (CPU) and the assembly language instructions of the TMS320C28x fixed-point digital signal processors (DSPs). It also describes emulation features available on these DSPs.

SPRU712— TMS320x280x, 2801x, 2804x System Control and Interrupts Reference Guide describes the various interrupts and system control features of the 280x digital signal processors (DSPs).

Peripheral Guides—

SPRU566— TMS320x28xx, 28xxx Peripheral Reference Guide describes the peripheral reference guides of the 28x digital signal processors (DSPs).

SPRU716— TMS320x280x, 2801x, 2804x Analog-to-Digital Converter (ADC) Reference Guide describes how to configure and use the on-chip ADC module, which is a 12-bit pipelined ADC.

SPRU791— TMS320x28xx, 28xxx Enhanced Pulse Width Modulator (ePWM) Module Reference Guide describes the main areas of the enhanced pulse width modulator that include digital motor control, switch mode power supply control, UPS (uninterruptible power supplies), and other forms of power conversion

SPRU924— TMS320x28xx, 28xxx High-Resolution Pulse Width Modulator (HRPWM) describes the operation of the high-resolution extension to the pulse width modulator (HRPWM)

SPRU807— TMS320x28xx, 28xxx Enhanced Capture (eCAP) Module Reference Guide describes the enhanced capture module. It includes the module description and registers.

SPRU791D–November 2004–Revised October 2007 |

Read This First |

9 |

Submit Documentation Feedback |

|

|

www.ti.com

Related Documentation From Texas Instruments

SPRU790— TMS320x28xx, 28xxx Enhanced Quadrature Encoder Pulse (eQEP) Reference Guide describes the eQEP module, which is used for interfacing with a linear or rotary incremental encoder to get position, direction, and speed information from a rotating machine in high performance motion and position control systems. It includes the module description and registers

SPRU074— TMS320x28xx, 28xxx Enhanced Controller Area Network (eCAN) Reference Guide describes the eCAN that uses established protocol to communicate serially with other controllers in electrically noisy environments.

SPRU051— TMS320x28xx, 28xxx Serial Communication Interface (SCI) Reference Guide describes the SCI, which is a two-wire asynchronous serial port, commonly known as a UART. The SCI modules support digital communications between the CPU and other asynchronous peripherals that use the standard non-return-to-zero (NRZ) format.

SPRU059— TMS320x28xx, 28xxx Serial Peripheral Interface (SPI) Reference Guide describes the SPI - a high-speed synchronous serial input/output (I/O) port - that allows a serial bit stream of programmed length (one to sixteen bits) to be shifted into and out of the device at a programmed bit-transfer rate.

SPRU721— TMS320x28xx, 28xxx Inter-Integrated Circuit (I2C) Reference Guide describes the features and operation of the inter-integrated circuit (I2C) module that is available on the TMS320x280x digital signal processor (DSP).

SPRU722— TMS320x280x, 2801x, 2804x Boot ROM Reference Guide describes the purpose and features of the bootloader (factory-programmed boot-loading software). It also describes other contents of the device on-chip boot ROM and identifies where all of the information is located within that memory.

Tools Guides—

SPRU513— TMS320C28x Assembly Language Tools User's Guide describes the assembly language tools (assembler and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for the TMS320C28x device.

SPRU514— TMS320C28x Optimizing C Compiler User's Guide describes the TMS320C28x™ C/C++ compiler. This compiler accepts ANSI standard C/C++ source code and produces TMS320 DSP assembly language source code for the TMS320C28x device.

SPRU608— The TMS320C28x Instruction Set Simulator Technical Overview describes the simulator, available within the Code Composer Studio for TMS320C2000 IDE, that simulates the instruction set of the C28x™ core.

SPRU625— TMS320C28x DSP/BIOS Application Programming Interface (API) Reference Guide describes development using DSP/BIOS.

Application Reports—

SPRAAM0— Getting Started With TMS320C28x™ Digital Signal Controllers is organized by development flow and functional areas to make your design effort as seamless as possible. Tips on getting started with C28x™ DSP software and hardware development are provided to aid in your initial design and debug efforts. Each section includes pointers to valuable information including technical documentation, software, and tools for use in each phase of design.

SPRAAD5— Power Line Communication for Lighting Apps using BPSK w/ a Single DSP Controller presents a complete implementation of a power line modem following CEA-709 protocol using a single DSP.

SPRAA85— Programming TMS320x28xx and 28xxx Peripherals in C/C++ explores a hardware abstraction layer implementation to make C/C++ coding easier on 28x DSPs. This method is compared to traditional #define macros and topics of code efficiency and special case registers are also addressed.

10 |

Read This First |

SPRU791D–November 2004–Revised October 2007 |

Submit Documentation Feedback

www.ti.com

Related Documentation From Texas Instruments

SPRA958— Running an Application from Internal Flash Memory on the TMS320F28xx DSP covers the requirements needed to properly configure application software for execution from on-chip flash memory. Requirements for both DSP/BIOS™ and non-DSP/BIOS projects are presented. Example code projects are included.

SPRAA91— TMS320F280x DSC USB Connectivity Using TUSB3410 USB-to-UART Bridge Chip presents hardware connections as well as software preparation and operation of the development system using a simple communication echo program.

SPRAA58— TMS320x281x to TMS320x280x Migration Overview describes differences between the Texas Instruments TMS320x281x and TMS320x280x DSPs to assist in application migration from the 281x to the 280x. While the main focus of this document is migration from 281x to 280x, users considering migrating in the reverse direction (280x to 281x) will also find this document useful.

SPRAAD8— TMS320280x and TMS320F2801x ADC Calibration describes a method for improving the absolute accuracy of the 12-bit ADC found on the TMS320280x and TMS3202801x devices. Inherent gain and offset errors affect the absolute accuracy of the ADC. The methods described in this report can improve the absolute accuracy of the ADC to levels better than 0.5%. This application report has an option to download an example program that executes from RAM on the F2808 EzDSP.

SPRAAI1— Using Enhanced Pulse Width Modulator (ePWM) Module for 0-100% Duty Cycle Control provides a guide for the use of the ePWM module to provide 0% to 100% duty cycle control and is applicable to the TMS320x280x family of processors.

SPRAA88— Using PWM Output as a Digital-to-Analog Converter on a TMS320F280x presents a method for utilizing the on-chip pulse width modulated (PWM) signal generators on the TMS320F280x family of digital signal controllers as a digital-to-analog converter (DAC).

SPRAAH1— Using the Enhanced Quadrature Encoder Pulse (eQEP) Module provides a guide for the use of the eQEP module as a dedicated capture unit and is applicable to the TMS320x280x, 28xxx family of processors.

SPRA820— Online Stack Overflow Detection on the TMS320C28x DSP presents the methodology for online stack overflow detection on the TMS320C28x™ DSP. C-source code is provided that contains functions for implementing the overflow detection on both DSP/BIOS™ and non-DSP/BIOS applications.

SPRA806— An Easy Way of Creating a C-callable Assembly Function for the TMS320C28x DSP provides instructions and suggestions to configure the C compiler to assist with understanding of parameter-passing conventions and environments expected by the C compiler.

Trademarks

TMS320C28x, C28x are trademarks of Texas Instruments.

SPRU791D–November 2004–Revised October 2007 |

Read This First |

11 |

Submit Documentation Feedback

12 |

Read This First |

SPRU791D–November 2004–Revised October 2007 |

Submit Documentation Feedback

Chapter 1

SPRU791D–November 2004–Revised October 2007

Introduction

The enhanced pulse width modulator (ePWM) peripheral is a key element in controlling many of the power-related systems found in both commercial and industrial equipments. These systems include digital motor control, switch mode power supply control, uninterruptible power supplies (UPS), and other forms of power conversion. The ePWM peripheral performs a digital to analog (DAC) function, where the duty cycle is equivalent to a DAC analog value; it is sometimes referred to as a Power DAC.

This reference guide is applicable for the ePWM found on the TMS320x280x, TMS320x2801x and TMS320x2804x processors. This includes all Flash-based, ROM-based, and RAM-based devices.

Topic |

|

Page |

1.1 |

Introduction.............................................................................. |

14 |

1.2 |

Submodule Overview................................................................. |

14 |

1.3 |

Register Mapping...................................................................... |

17 |

SPRU791D–November 2004–Revised October 2007 |

Introduction |

13 |

Submit Documentation Feedback |

|

|

www.ti.com

Introduction

1.1Introduction

An effective PWM peripheral must be able to generate complex pulse width waveforms with minimal CPU overhead or intervention. It needs to be highly programmable and very flexible while being easy to understand and use. The ePWM unit described here addresses these requirements by allocating all needed timing and control resources on a per PWM channel basis. Cross coupling or sharing of resources has been avoided; instead, the ePWM is built up from smaller single channel modules with separate resources and that can operate together as required to form a system. This modular approach results in an orthogonal architecture and provides a more transparent view of the peripheral structure, helping users to understand its operation quickly.

In this document the letter x within a signal or module name is used to indicate a generic ePWM instance on a device. For example output signals EPWMxA and EPWMxB refer to the output signals from the ePWMx instance. Thus, EPWM1A and EPWM1B belong to ePWM1 and likewise EPWM4A and EPWM4B belong to ePWM4.

1.2Submodule Overview

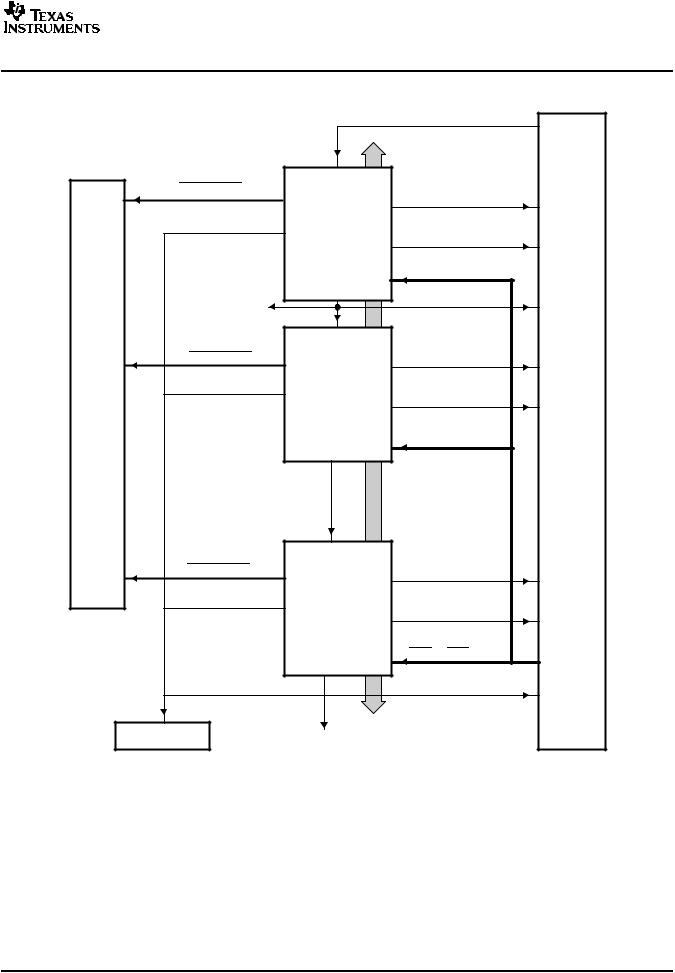

The ePWM module represents one complete PWM channel composed of two PWM outputs: EPWMxA and EPWMxB. Multiple ePWM modules are instanced within a device as shown in Figure 1-1. Each ePWM instance is identical with one exception. Some instances include a hardware extension that allows more precise control of the PWM outputs. This extension is the high-resolution pulse width modulator (HRPWM) and is described in the TMS320x28xx, 28xxx High-Resolution Pulse Width Modulator (HRPWM) Reference Guide (SPRU924). See the device-specific data manual to determine which ePWM instances include this feature. Each ePWM module is indicated by a numerical value starting with 1. For example ePWM1 is the first instance and ePWM3 is the 3rd instance in the system and ePWMx indicates any instance.

The ePWM modules are chained together via a clock synchronization scheme that allows them to operate as a single system when required. Additionally, this synchronization scheme can be extended to the capture peripheral modules (eCAP). The number of modules is device-dependent and based on target application needs. Modules can also operate stand-alone.

Each ePWM module supports the following features:

∙Dedicated 16-bit time-base counter with period and frequency control

∙Two PWM outputs (EPWMxA and EPWMxB) that can be used in the following configurations::

–Two independent PWM outputs with single-edge operation

–Two independent PWM outputs with dual-edge symmetric operation

–One independent PWM output with dual-edge asymmetric operation

∙Asynchronous override control of PWM signals through software.

∙Programmable phase-control support for lag or lead operation relative to other ePWM modules.

∙Hardware-locked (synchronized) phase relationship on a cycle-by-cycle basis.

∙Dead-band generation with independent rising and falling edge delay control.

∙Programmable trip zone allocation of both cycle-by-cycle trip and one-shot trip on fault conditions.

∙A trip condition can force either high, low, or high-impedance state logic levels at PWM outputs.

∙All events can trigger both CPU interrupts and ADC start of conversion (SOC)

∙Programmable event prescaling minimizes CPU overhead on interrupts.

∙PWM chopping by high-frequency carrier signal, useful for pulse transformer gate drives.

Each ePWM module is connected to the input/output signals shown in Figure 1-1. The signals are described in detail in subsequent sections.

14 |

Introduction |

SPRU791D–November 2004–Revised October 2007 |

Submit Documentation Feedback

www.ti.com

Submodule Overview

Figure 1-1. Multiple ePWM Modules

|

|

|

xSYNCI |

|

|

SYNCI |

|

|

EPWM1INT |

|

|

|

|

|

EPWM1A |

|

EPWM1SOC |

|

|

|

|

ePWM1 module |

EPWM1B |

|

|

|

|

|

|

SYNCO |

|

|

To eCAP1 |

|

xSYNCO |

|

|

|

|

|

|

SYNCI |

|

|

EPWM2INT |

|

EPWM2A |

PIE |

EPWM2SOC |

ePWM2 module |

GPIO |

|

|

EPWM2B |

|

|

|

|

|

|

|

|

MUX |

|

|

SYNCO |

|

|

|

SYNCI |

|

|

EPWMxINT |

|

EPWMxA |

|

|

|

|

|

EPWMxSOC |

ePWMx module |

|

|

|

EPWMxB |

|

|

|

|

|

|

|

|

TZ1 to TZ6 |

|

|

SYNCO |

|

|

|

|

xSOC |

|

|

Peripheral |

|

|

ADC |

Frame 1 |

|

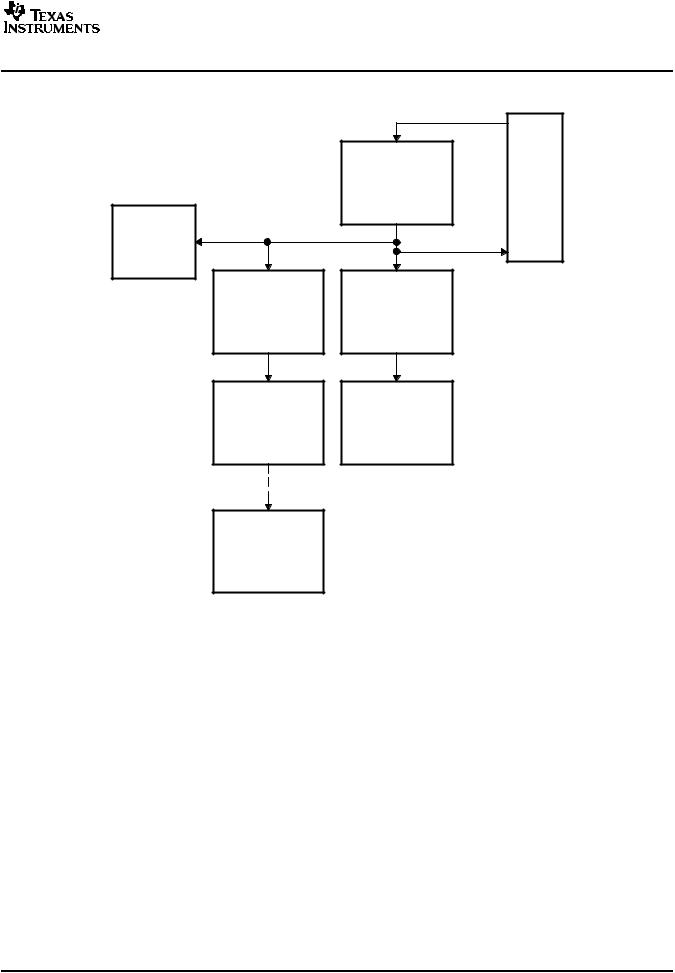

The order in which the ePWM modules are connected may differ from what is shown in Figure 1-1. See Section 2.2.3.2 for the synchronization scheme for a particular device. Each ePWM module consists of seven submodules and is connected within a system via the signals shown in Figure 1-2.

SPRU791D–November 2004–Revised October 2007 |

Introduction |

15 |

Submit Documentation Feedback

www.ti.com

Submodule Overview

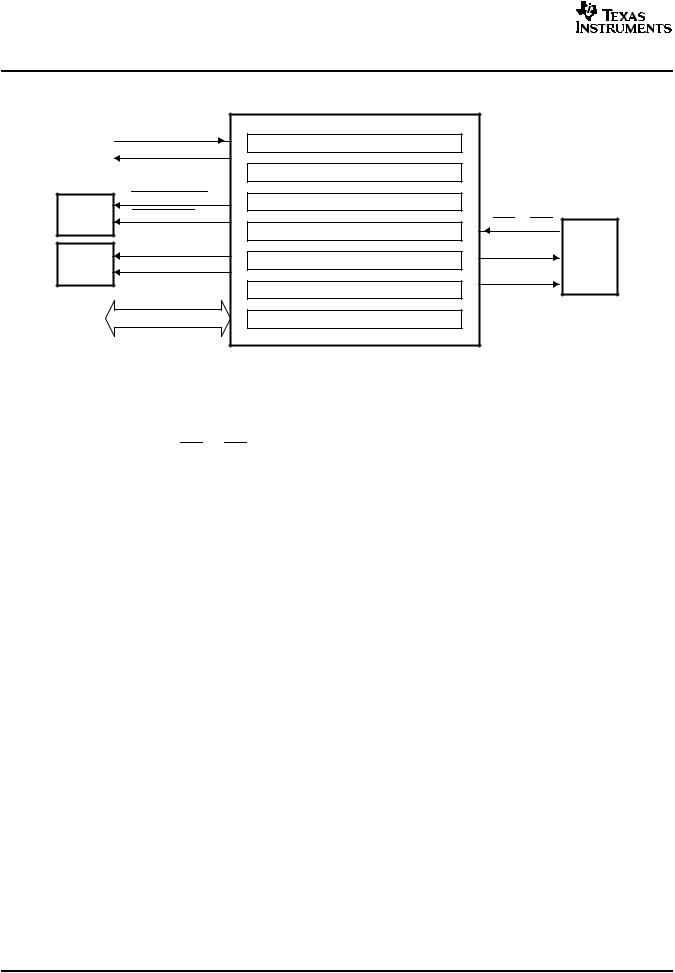

Figure 1-2. Submodules and Signal Connections for an ePWM Module

|

EPWMxSYNCI |

ePWM module |

|

|

|

Time-base (TB) module |

|

|

|

|

EPWMxSYNCO |

|

|

|

|

|

|

|

|

|

|

Counter-compare (CC) module |

|

|

|

EPWMxTZINT |

Action-qualifier (AQ) module |

|

|

PIE |

|

|

|

|

EPWMxINT |

|

TZ1 to TZ6 |

|

|

|

|

Dead-band (DB) module |

|

|

|

|

|

|

|

ADC |

EPWMxSOCA |

PWM-chopper (PC) module |

EPWMxA |

GPIO |

EPWMxSOCB |

|

MUX |

||

|

EPWMxB |

|||

|

|

Event-trigger (ET) module |

|

|

|

|

|

|

|

|

Peripheral bus |

Trip-zone (TZ) module |

|

|

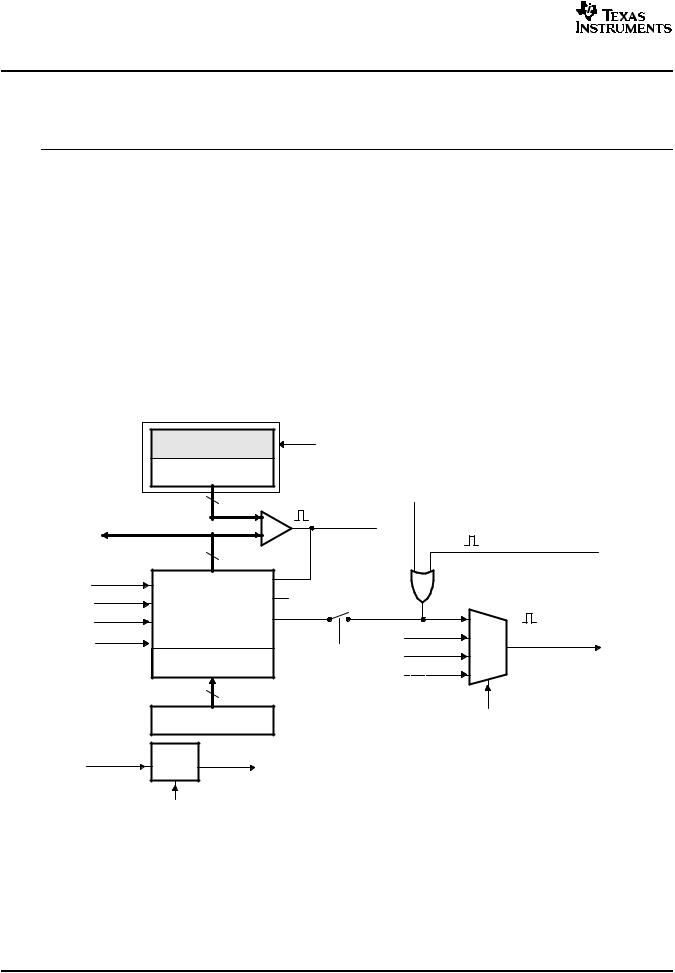

Figure 1-3 shows more internal details of a single ePWM module. The main signals used by the ePWM module are:

∙PWM output signals (EPWMxA and EPWMxB).

The PWM output signals are made available external to the device through the GPIO peripheral described in the system control and interrupts guide for your device.

∙Trip-zone signals (TZ1 to TZ6).

These input signals alert the ePWM module of an external fault condition. Each module on a device can be configured to either use or ignore any of the trip-zone signals. The trip-zone signals can be configured as asynchronous inputs through the GPIO peripheral.

∙Time-base synchronization input (EPWMxSYNCI) and output (EPWMxSYNCO) signals.

The synchronization signals daisy chain the ePWM modules together. Each module can be configured to either use or ignore its synchronization input. The clock synchronization input and output signal are brought out to pins only for ePWM1 (ePWM module #1). The synchronization output for ePWM1 (EPWM1SYNCO) is also connected to the SYNCI of the first enhanced capture module (eCAP1).

∙ADC start-of-conversion signals (EPWMxSOCA and EPWMxSOCB).

Each ePWM module has two ADC start of conversion signals (one for each sequencer). Any ePWM module can trigger a start of conversion for either sequencer. Which event triggers the start of conversion is configured in the Event-Trigger submodule of the ePWM.

∙Peripheral Bus

The peripheral bus is 32-bits wide and allows both 16-bit and 32-bit writes to the ePWM register file.

16 |

Introduction |

SPRU791D–November 2004–Revised October 2007 |

Submit Documentation Feedback

www.ti.com

Register Mapping

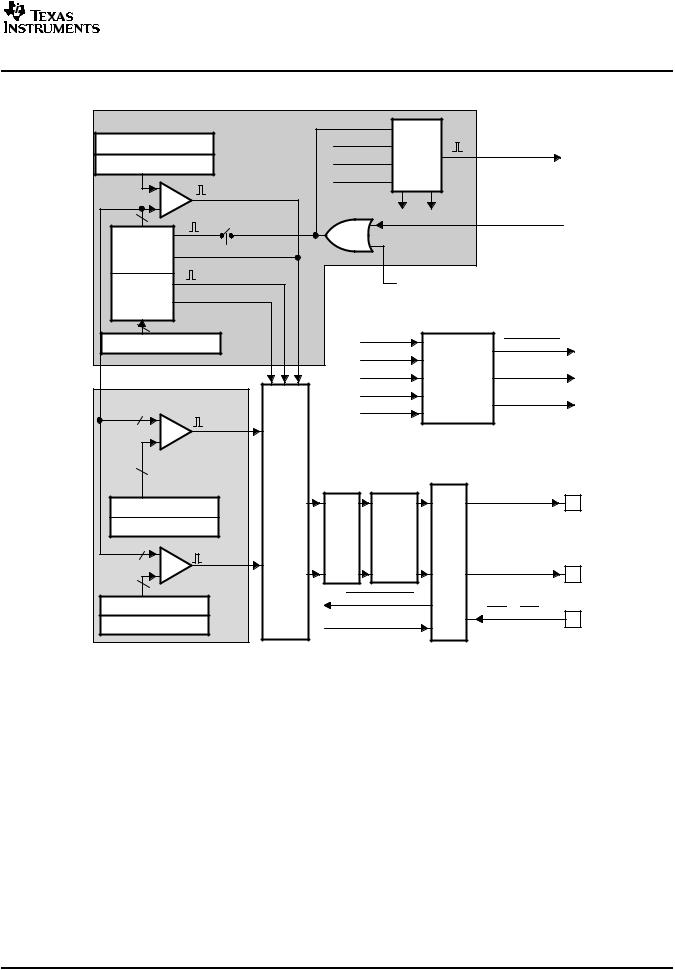

Figure 1-3. ePWM Submodules and Critical Internal Signal Interconnects

Time-base (TB) |

|

|

|

Sync |

|

|

||

|

|

|

|

|

|

|

||

TBPRD shadow (16) |

|

|

|

in/out |

|

EPWMxSYNCO |

||

|

|

|

|

|

select |

|

||

TBPRD active (16) |

|

|

|

|

|

|||

|

|

|

MUX |

|

|

|||

|

|

|

|

|

|

|

||

|

|

CTR_PRD |

|

S0 |

S1 |

|

|

|

16 |

|

|

|

|

TBCTL[SWFSYNC] |

|

EPWMxSYNCI |

|

Counter |

|

|

|

|

|

|

|

|

UP/DWN |

TBCTL[PHSEN] |

|

|

|

|

|

||

(16 bit) |

CTR = ZERO |

|

|

TBCTL[SWFSYNC] (software |

||||

TBCTR |

|

|

||||||

|

|

|

|

|

forced sync) |

|||

active |

CTR_Dir |

|

|

|

||||

|

|

|

|

|

|

|||

(16) |

|

|

|

|

|

|

|

|

16 |

|

Phase |

|

CTR = PRD |

|

|

|

|

TBPHS active (16) |

|

|

|

EPWMxINT |

||||

control |

|

CTR = ZERO |

|

|

||||

|

|

|

Event |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

CTR = CMPA |

trigger and |

EPWMxSOCA |

||

|

|

|

|

CTR = CMPB |

interrupt |

|

|

|

Counter compare (CC) |

|

|

(ET) |

|

EPWMxSOCB |

|||

|

|

|

CTR_Dir |

|

||||

|

|

|

|

|

|

|

|

|

16 |

|

|

|

|

|

|

|

|

|

CTR = CMPA |

|

|

|

|

|

|

|

16 |

|

|

|

|

|

|

|

|

|

|

|

Action |

|

|

|

|

|

CMPA active (16) |

|

qualifier |

|

|

|

|

EPWMxA |

|

|

(AQ) |

|

|

|

|

|

||

|

|

|

|

PWM |

|

|

|

|

CMPA shadow (16) |

|

|

Dead |

|

|

|

||

|

|

band |

chopper |

|

|

|

||

|

|

|

|

|

|

|

||

16 |

|

|

|

(DB) |

(PC) |

Trip |

|

|

|

|

|

|

|

|

zone |

EPWMxB |

|

|

CTR = CMPB |

|

|

|

(TZ) |

|||

16 |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

CMPB active (16) |

|

|

EPWMxTZINT |

|

|

|

||

|

|

|

|

|

|

TZ1 to TZ6 |

||

|

|

|

|

CTR=ZERO |

|

|

||

CMPB shadow (16) |

|

|

|

|

|

|||

|

|

|

|

|

|

|

||

Figure 1-3 also shows the key internal submodule interconnect signals. Each submodule is described in detail in its respective section.

1.3Register Mapping

The complete ePWM module control and status register set is grouped by submodule as shown in Table 1-1. Each register set is duplicated for each instance of the ePWM module. The start address for each ePWM register file instance on a device is specified in the appropriate data manual.

SPRU791D–November 2004–Revised October 2007 |

Introduction |

17 |

Submit Documentation Feedback

www.ti.com

Register Mapping

Table 1-1. ePWM Module Control and Status Register Set Grouped by Submodule

|

Offset (1) |

Size |

|

|

Name |

(x16) |

Shadow |

Description |

|

|

|

|

|

Time-Base Submodule Registers |

TBCTL |

0x0000 |

1 |

No |

Time-Base Control Register |

TBSTS |

0x0001 |

1 |

No |

Time-Base Status Register |

TBPHSHR |

0x0002 |

1 |

No |

Extension for HRPWM Phase Register (2) |

TBPHS |

0x0003 |

1 |

No |

Time-Base Phase Register |

TBCTR |

0x0004 |

1 |

No |

Time-Base Counter Register |

TBPRD |

0x0005 |

1 |

Yes |

Time-Base Period Register |

|

|

|

|

Counter-Compare Submodule Registers |

CMPCTL |

0x0007 |

1 |

No |

Counter-Compare Control Register |

CMPAHR |

0x0008 |

1 |

No |

Extension for HRPWM Counter-Compare A Register (2) |

CMPA |

0x0009 |

1 |

Yes |

Counter-Compare A Register |

CMPB |

0x000A |

1 |

Yes |

Counter-Compare B Register |

|

|

|

|

Action-Qualifier Submodule Registers |

AQCTLA |

0x000B |

1 |

No |

Action-Qualifier Control Register for Output A (EPWMxA) |

AQCTLB |

0x000C |

1 |

No |

Action-Qualifier Control Register for Output B (EPWMxB) |

AQSFRC |

0x000D |

1 |

No |

Action-Qualifier Software Force Register |

AQCSFRC |

0x000E |

1 |

Yes |

Action-Qualifier Continuous S/W Force Register Set |

|

|

|

|

Dead-Band Generator Submodule Registers |

DBCTL |

0x000F |

1 |

No |

Dead-Band Generator Control Register |

DBRED |

0x0010 |

1 |

No |

Dead-Band Generator Rising Edge Delay Count Register |

DBFED |

0x0011 |

1 |

No |

Dead-Band Generator Falling Edge Delay Count Register |

|

|

|

|

Trip-Zone Submodule Registers |

TZSEL |

0x0012 |

1 |

No |

Trip-Zone Select Register |

TZCTL |

0x0014 |

1 |

No |

Trip-Zone Control Register (3) |

TZEINT |

0x0015 |

1 |

No |

Trip-Zone Enable Interrupt Register (3) |

TZFLG |

0x0016 |

1 |

No |

Trip-Zone Flag Register (3) |

TZCLR |

0x0017 |

1 |

No |

Trip-Zone Clear Register (3) |

TZFRC |

0x0018 |

1 |

No |

Trip-Zone Force Register (3) |

|

|

|

|

Event-Trigger Submodule Registers |

ETSEL |

0x0019 |

1 |

No |

Event-Trigger Selection Register |

ETPS |

0x001A |

1 |

No |

Event-Trigger Pre-Scale Register |

ETFLG |

0x001B |

1 |

No |

Event-Trigger Flag Register |

ETCLR |

0x001C |

1 |

No |

Event-Trigger Clear Register |

ETFRC |

0x001D |

1 |

No |

Event-Trigger Force Register |

|

|

|

|

PWM-Chopper Submodule Registers |

PCCTL |

0x001E |

1 |

No |

PWM-Chopper Control Register |

|

|

|

|

High-Resolution Pulse Width Modulator (HRPWM) Extension Registers |

HRCNFG |

0x0020 |

1 |

No |

HRPWM Configuration Register (2) (3) |

(1)Locations not shown are reserved.

(2)These registers are only available on ePWM instances that include the high-resolution PWM extension. Otherwise these locations are reserved. These registers are described in the TMS320x28xx, 28xxx High-Resolution Pulse Width Modulator (HRPWM) Reference Guide (SPRU924). See the device specific data manual to determine which instances include the HRPWM.

(3)EALLOW protected registers as described in the specific device version of the System Control and Interrupts Reference Guide listed in Section 1.

18 |

Introduction |

SPRU791D–November 2004–Revised October 2007 |

Submit Documentation Feedback

Chapter 2

SPRU791D–November 2004–Revised October 2007

ePWM Submodules

Seven submodules are included in every ePWM peripheral. Each of these submodules performs specific tasks that can be configured by software.

Topic |

|

Page |

2.1 |

Overview.................................................................................. |

20 |

2.2 |

Time-Base (TB) Submodule........................................................ |

23 |

2.3 |

Counter-Compare (CC) Submodule ............................................. |

32 |

2.4 |

Action-Qualifier (AQ) Submodule ................................................ |

37 |

2.5 |

Dead-Band Generator (DB) Submodule........................................ |

50 |

2.6 |

PWM-Chopper (PC) Submodule .................................................. |

55 |

2.7 |

Trip-Zone (TZ) Submodule ......................................................... |

59 |

2.8 |

Event-Trigger (ET) Submodule.................................................... |

63 |

SPRU791D–November 2004–Revised October 2007 |

ePWM Submodules |

19 |

Submit Documentation Feedback |

|

|

www.ti.com

Overview

2.1Overview

Table 2-1 lists the seven key submodules together with a list of their main configuration parameters. For example, if you need to adjust or control the duty cycle of a PWM waveform, then you should see the counter-compare submodule in Section 2.3 for relevant details.

|

|

Table 2-1. Submodule Configuration Parameters |

|

Submodule |

Configuration Parameter or Option |

||

Time-base (TB) |

∙ |

Scale the time-base clock (TBCLK) relative to the system clock (SYSCLKOUT). |

|

|

∙ |

Configure the PWM time-base counter (TBCTR) frequency or period. |

|

|

∙ |

Set the mode for the time-base counter: |

|

|

|

– count-up mode: used for asymmetric PWM |

|

|

|

– count-down mode: used for asymmetric PWM |

|

|

|

– count-up-and-down mode: used for symmetric PWM |

|

|

∙ |

Configure the time-base phase relative to another ePWM module. |

|

|

∙ |

Synchronize the time-base counter between modules through hardware or software. |

|

|

∙ |

Configure the direction (up or down) of the time-base counter after a synchronization event. |

|

|

∙ |

Configure how the time-base counter will behave when the device is halted by an emulator. |

|

|

∙ |

Specify the source for the synchronization output of the ePWM module: |

|

|

|

– |

Synchronization input signal |

|

|

– Time-base counter equal to zero |

|

|

|

– Time-base counter equal to counter-compare B (CMPB) |

|

|

|

– No output synchronization signal generated. |

|

Counter-compare (CC) |

∙ |

Specify the PWM duty cycle for output EPWMxA and/or output EPWMxB |

|

|

∙ |

Specify the time at which switching events occur on the EPWMxA or EPWMxB output |

|

Action-qualifier (AQ) |

∙ |

Specify the type of action taken when a time-base or counter-compare submodule event occurs: |

|

|

|

– |

No action taken |

|

|

– Output EPWMxA and/or EPWMxB switched high |

|

|

|

– Output EPWMxA and/or EPWMxB switched low |

|

|

|

– Output EPWMxA and/or EPWMxB toggled |

|

|

∙ |

Force the PWM output state through software control |

|

|

∙ |

Configure and control the PWM dead-band through software |

|

Dead-band (DB) |

∙ |

Control of traditional complementary dead-band relationship between upper and lower switches |

|

|

∙ |

Specify the output rising-edge-delay value |

|

|

∙ |

Specify the output falling-edge delay value |

|

|

∙ |

Bypass the dead-band module entirely. In this case the PWM waveform is passed through |

|

|

|

without modification. |

|

PWM-chopper (PC) |

∙ |

Create a chopping (carrier) frequency. |

|

|

∙ |

Pulse width of the first pulse in the chopped pulse train. |

|

|

∙ |

Duty cycle of the second and subsequent pulses. |

|

|

∙ |

Bypass the PWM-chopper module entirely. In this case the PWM waveform is passed through |

|

|

|

without modification. |

|

Trip-zone (TZ) |

∙ |

Configure the ePWM module to react to one, all, or none of the trip-zone pins. |

|

|

∙ |

Specify the tripping action taken when a fault occurs: |

|

|

|

– Force EPWMxA and/or EPWMxB high |

|

|

|

– Force EPWMxA and/or EPWMxB low |

|

|

|

– Force EPWMxA and/or EPWMxB to a high-impedance state |

|

|

|

– Configure EPWMxA and/or EPWMxB to ignore any trip condition. |

|

|

∙ |

Configure how often the ePWM will react to each trip-zone pin: |

|

|

|

– |

One-shot |

|

|

– Cycle-by-cycle |

|

|

∙ |

Enable the trip-zone to initiate an interrupt. |

|

|

∙ |

Bypass the trip-zone module entirely. |

|

20 |

ePWM Submodules |

SPRU791D–November 2004–Revised October 2007 |

|

|

Submit Documentation Feedback |

www.ti.com

|

|

Overview |

|

Table 2-1. Submodule Configuration Parameters (continued) |

|

Submodule |

Configuration Parameter or Option |

|

Event-trigger (ET) |

∙ |

Enable the ePWM events that will trigger an interrupt. |

|

∙ |

Enable ePWM events that will trigger an ADC start-of-conversion event. |

|

∙ |

Specify the rate at which events cause triggers (every occurrence or every second or third |

|

|

occurrence) |

|

∙ |

Poll, set, or clear event flags |

Code examples are provided in the remainder of this document that show how to implement various ePWM module configurations. These examples use the constant definitions shown in Example 2-1. These definitions are also used in the C280x C/C++ Header Files and Peripheral Examples (SPRC191).

Example 2-1. Constant Definitions Used in the Code Examples

//TBCTL (Time-Base Control)

//= = = = = = = = = = = = = = = = = = = = = = = = = =

//TBCTR MODE bits

#define |

TB_COUNT_UP |

0x0 |

#define |

TB_COUNT_DOWN |

0x1 |

#define |

TB_COUNT_UPDOWN |

0x2 |

#define |

TB_FREEZE |

0x3 |

// PHSEN bit |

|

|

#define |

TB_DISABLE |

0x0 |

#define |

TB_ENABLE |

0x1 |

// PRDLD bit |

|

|

#define |

TB_SHADOW |

0x0 |

#define |

TB_IMMEDIATE |

0x1 |

// SYNCOSEL bits |

|

|

#define |

TB_SYNC_IN |

0x0 |

#define |

TB_CTR_ZERO |

0x1 |

#define |

TB_CTR_CMPB |

0x2 |

#define |

TB_SYNC_DISABLE |

0x3 |

// HSPCLKDIV and CLKDIV bits |

|

|

#define |

TB_DIV1 |

0x0 |

#define |

TB_DIV2 |

0x1 |

#define |

TB_DIV4 |

0x2 |

// PHSDIR bit |

|

|

#define |

TB_DOWN |

0x0 |

#define |

TB_UP |

0x1 |

//CMPCTL (Compare Control)

//= = = = = = = = = = = = = = = = = = = = = = = = = =

//LOADAMODE and LOADBMODE bits

#define |

CC_CTR_ZERO |

0x0 |

#define |

CC_CTR_PRD |

0x1 |

#define |

CC_CTR_ZERO_PRD |

0x2 |

#define |

CC_LD_DISABLE |

0x3 |

// SHDWAMODE and SHDWBMODE bits |

|

|

#define |

CC_SHADOW |

0x0 |

#define |

CC_IMMEDIATE |

0x1 |

//AQCTLA and AQCTLB (Action-qualifier Control)

//= = = = = = = = = = = = = = = = = = = = = = = = = =

//ZRO, PRD, CAU, CAD, CBU, CBD bits

#define |

AQ_NO_ACTION |

0x0 |

#define |

AQ_CLEAR |

0x1 |

#define |

AQ_SET |

0x2 |

#define |

AQ_TOGGLE |

0x3 |

//DBCTL (Dead-Band Control)

//= = = = = = = = = = = = = = = = = = = = = = = = = =

//MODE bits

#define |

DB_DISABLE |

0x0 |

|

#define |

DBA_ENABLE |

0x1 |

|

#define |

DBB_ENABLE |

0x2 |

|

#define DB_FULL_ENABLE 0x3 |

|

|

|

// POLSEL bits |

|

|

|

#define |

DB_ACTV_HI |

0x0 |

|

#define |

DB_ACTV_LOC |

0x1 |

|

#define |

DB_ACTV_HIC |

0x2 |

|

SPRU791D–November 2004–Revised October 2007 |

ePWM Submodules |

21 |

|

Submit Documentation Feedback

www.ti.com

Overview

Example 2-1. Constant Definitions Used in the Code Examples (continued)

#define |

DB_ACTV_LO |

0x3 |

//PCCTL (chopper control)

//= = = = = = = = = = = = = = = = = = = = = = = = = =

//CHPEN bit

#define |

CHP_ENABLE |

0x0 |

#define CHP_DISABLE 0x1 |

|

|

// CHPFREQ bits |

|

|

#define |

CHP_DIV1 |

0x0 |

#define |

CHP_DIV2 |

0x1 |

#define |

CHP_DIV3 |

0x2 |

#define |

CHP_DIV4 |

0x3 |

#define |

CHP_DIV5 |

0x4 |

#define |

CHP_DIV6 |

0x5 |

#define |

CHP_DIV7 |

0x6 |

#define |

CHP_DIV8 |

0x7 |

// CHPDUTY bits |

|

|

#define |

CHP1_8TH |

0x0 |

#define |

CHP2_8TH |

0x1 |

#define |

CHP3_8TH |

0x2 |

#define |

CHP4_8TH |

0x3 |

#define |

CHP5_8TH |

0x4 |

#define |

CHP6_8TH |

0x5 |

#define |

CHP7_8TH |

0x6 |

//TZSEL (Trip-zone Select)

//= = = = = = = = = = = = = = = = = = = = = = = = = =

//CBCn and OSHTn bits

#define |

TZ_ENABLE |

0x0 |

#define |

TZ_DISABLE |

0x1 |

//TZCTL (Trip-zone Control)

//= = = = = = = = = = = = = = = = = = = = = = = = = =

//TZA and TZB bits

#define |

TZ_HIZ |

0x0 |

#define |

TZ_FORCE_HI |

0x1 |

#define |

TZ_FORCE_LO |

0x2 |

#define |

TZ_DISABLE |

0x3 |

//ETSEL (Event-trigger Select)

//= = = = = = = = = = = = = = = = = = = = = = = = = =

//INTSEL, SOCASEL, SOCBSEL bits

#define |

ET_CTR_ZERO |

0x1 |

#define |

ET_CTR_PRD |

0x2 |

#define |

ET_CTRU_CMPA |

0x4 |

#define |

ET_CTRD_CMPA |

0x5 |

#define |

ET_CTRU_CMPB |

0x6 |

#define |

ET_CTRD_CMPB |

0x7 |

//ETPS (Event-trigger Prescale)

//= = = = = = = = = = = = = = = = = = = = = = = = = =

//INTPRD, SOCAPRD, SOCBPRD bits

#define |

ET_DISABLE |

0x0 |

#define |

ET_1ST |

0x1 |

#define |

ET_2ND |

0x2 |

#define |

ET_3RD |

0x3 |

22 |

ePWM Submodules |

SPRU791D–November 2004–Revised October 2007 |

Submit Documentation Feedback

www.ti.com

Time-Base (TB) Submodule

2.2Time-Base (TB) Submodule

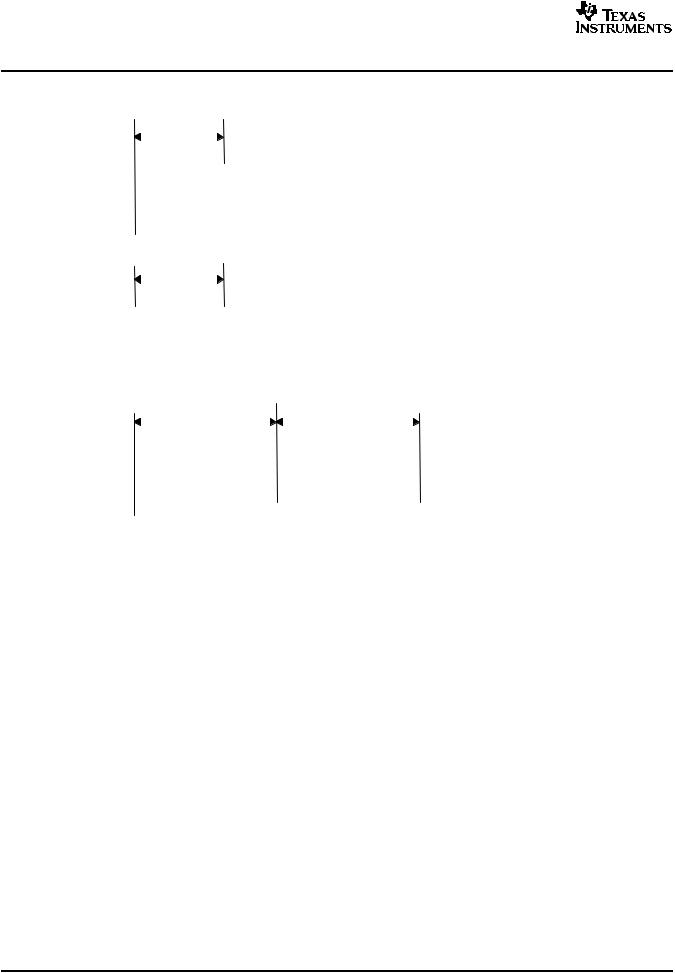

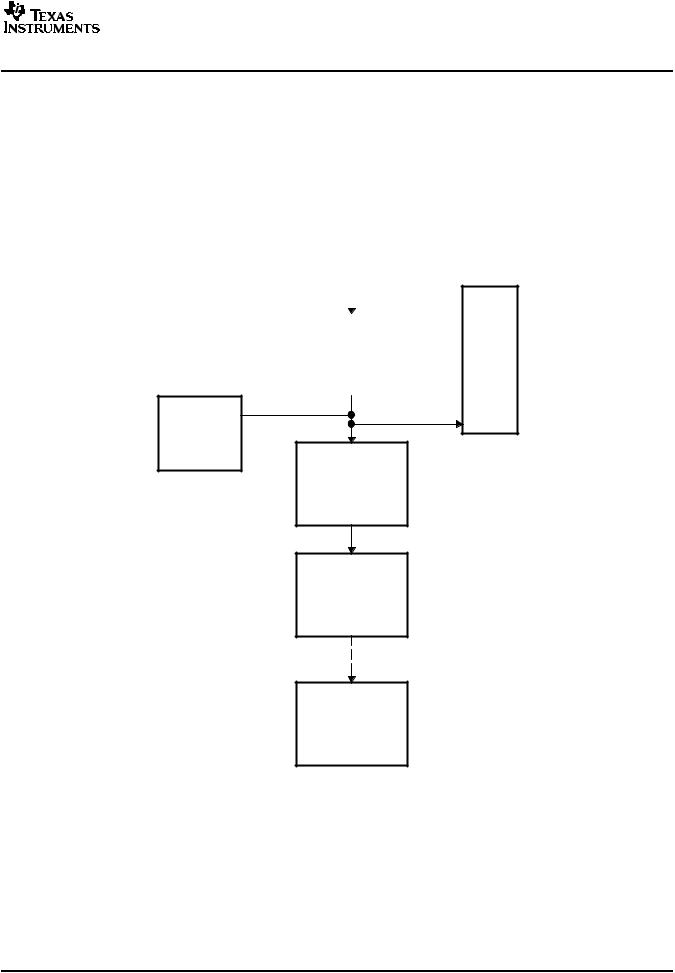

Each ePWM module has its own time-base submodule that determines all of the event timing for the ePWM module. Built-in synchronization logic allows the time-base of multiple ePWM modules to work together as a single system. Figure 2-1 illustrates the time-base module's place within the ePWM.

|

Figure 2-1. Time-Base Submodule Block Diagram |

|

|

|||||

|

|

|

|

CTR = PRD |

|

EPWMxINT |

|

|

|

|

|

|

|

CTR = 0 |

Event |

PIE |

|

|

|

|

|

|

|

|||

|

|

|

Action |

CTR = CMPA |

Trigger |

EPWMxSOCA |

|

|

|

|

|

and |

|

||||

EPWMxSYNCI |

|

|

Qualifier |

|

||||

|

|

|

|

Interrupt |

|

|

||

|

CTR = PRD |

(AQ) |

CTR = CMPB |

|

|

|||

|

|

|

ADC |

|||||

|

Time-Base |

|

|

|

CTR_Dir |

(ET) |

|

|

EPWMxSYNCO |

CTR = 0 |

|

|

EPWMxSOCB |

|

|||

|

(TB) |

CTR_Dir |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EPWMxA |

|

|

|

EPWMxA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Dead |

PWM- |

Trip |

|

|

|

|

CTR = CMPA |

|

Band |

chopper |

Zone |

|

|

|

|

|

(DB) |

|

GPIO |

|||

|

Counter |

|

|

(PC) |

(TZ) |

EPWMxB |

||

|

|

|

|

|

|

MUX |

||

|

Compare |

|

EPWMxB |

|

|

|

||

|

CTR = CMPB |

|

|

|

|

|

||

|

(CC) |

|

|

CTR = 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIE |

EPWMxTZINT |

|

TZ1 to TZ6 |

|

|

|

|

|

|

|

|

|

|

2.2.1 Purpose of the Time-Base Submodule

You can configure the time-base submodule for the following:

∙Specify the ePWM time-base counter (TBCTR) frequency or period to control how often events occur.

∙Manage time-base synchronization with other ePWM modules.

∙Maintain a phase relationship with other ePWM modules.

∙Set the time-base counter to count-up, count-down, or count-up-and-down mode.

∙Generate the following events:

–CTR = PRD: Time-base counter equal to the specified period (TBCTR = TBPRD) .

–CTR = Zero: Time-base counter equal to zero (TBCTR = 0x0000).

∙Configure the rate of the time-base clock; a prescaled version of the CPU system clock (SYSCLKOUT). This allows the time-base counter to increment/decrement at a slower rate.

SPRU791D–November 2004–Revised October 2007 |

ePWM Submodules |

23 |

Submit Documentation Feedback

www.ti.com

Time-Base (TB) Submodule

2.2.2 Controlling and Monitoring the Time-base Submodule

Table 2-2 shows the registers used to control and monitor the time-base submodule.

Table 2-2. Time-Base Submodule Registers

Register |

Address offset |

Shadowed |

Description |

TBCTL |

0x0000 |

No |

Time-Base Control Register |

TBSTS |

0x0001 |

No |

Time-Base Status Register |

TBPHSHR |

0x0002 |

No |

HRPWM extension Phase Register (1) |

TBPHS |

0x0003 |

No |

Time-Base Phase Register |

TBCTR |

0x0004 |

No |

Time-Base Counter Register |

TBPRD |

0x0005 |

Yes |

Time-Base Period Register |

(1)This register is available only on ePWM instances that include the high-resolution extension (HRPWM). On ePWM modules that do not include the HRPWM, this location is reserved. This register is described in the TMS320x28xx, 28xxx High-Resolution Pulse Width Modulator (HRPWM) Reference Guide (SPRU924). See the device specific data manual to determine which ePWM instances include this feature.

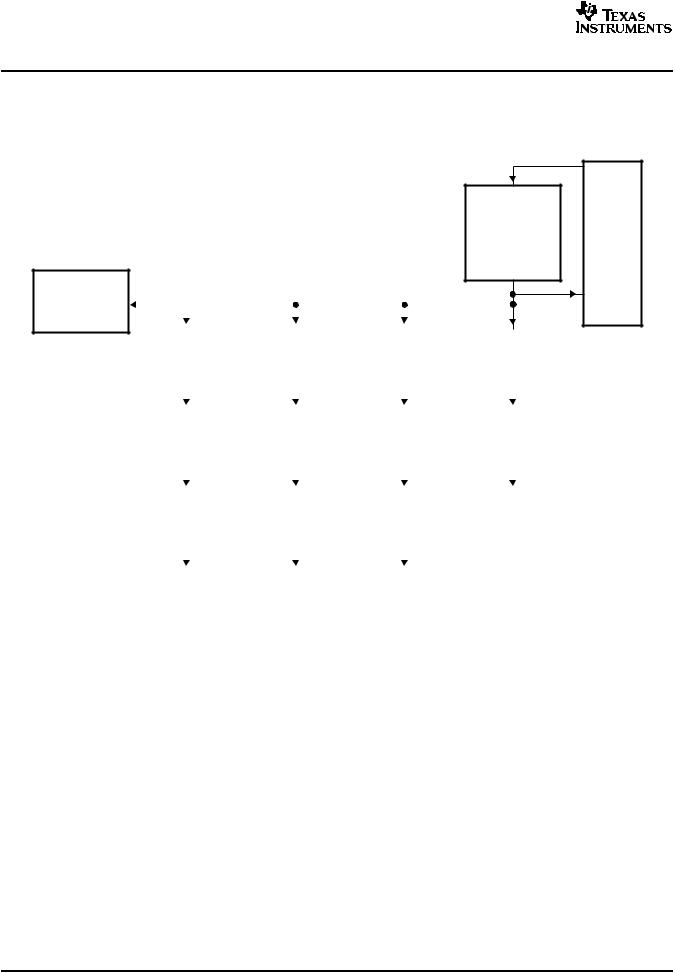

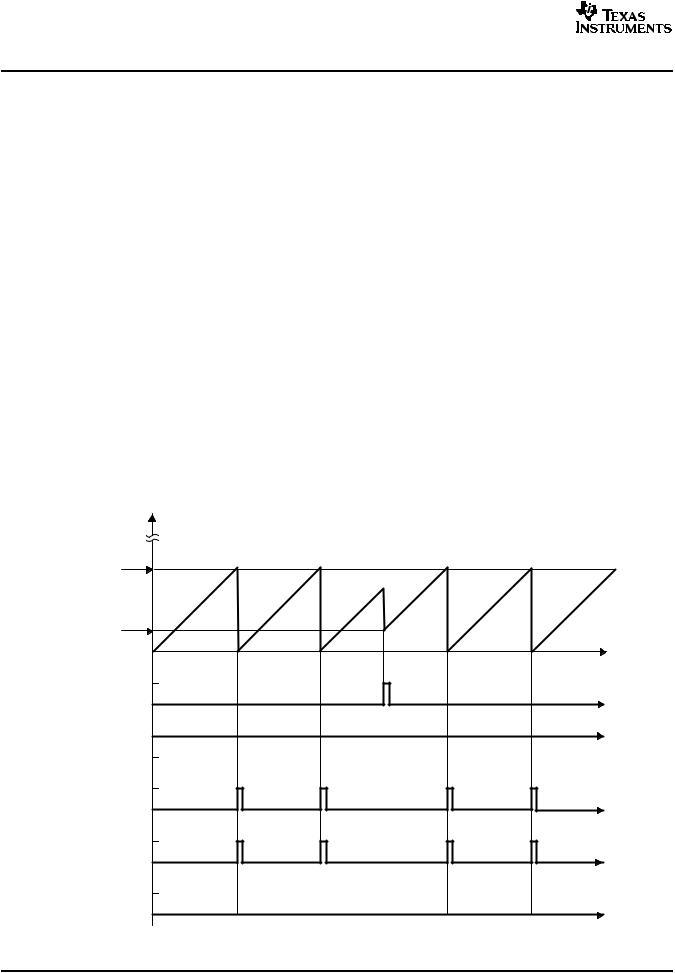

The block diagram in Figure 2-2 shows the critical signals and registers of the time-base submodule. Table 2-3 provides descriptions of the key signals associated with the time-base submodule.

Figure 2-2. Time-Base Submodule Signals and Registers

|

|

TBPRD |

|

TBCTL[PRDLD] |

|

|

|

|

Period Shadow |

|

|

|

|||

|

|

|

|

|

|||

|

|

TBPRD |

|

|

|

|

|

|

|

Period Active |

|

|

|

|

|

|

|

16 |

|

TBCTL[SWFSYNC] |

|

|

|

|

|

|

|

|

|

|

|

TBCTR[15:0] |

|

|

CTR = PRD |

|

|

|

|

|

|

16 |

|

|

|

|

EPWMxSYNCI |

|

|

|

|

|

|

|

|

CTR = Zero |

|

Counter |

Reset |

|

|

|

|

|

Zero |

|

|

|

|

||

CTR_dir |

Mode |

TBCTL[CTRMODE] |

|

|

|

||

Dir |

UP/DOWN |

|

|

|

|||

|

|

|

|

|

|

|

|

CTR_max |

Max |

|

Load |

|

|

|

|

|

|

|

CTR = Zero |

|

|

||

TBCLK |

|

|

|

|

Sync |

EPWMxSYNCO |

|

clk |

|

|

|

|

|||

|

|

|

|

|

Out |

||

|

|

|