Intel Core 2 Duo User Manual

Intel® CoreTM 2 Duo Processor and

Intel ® Q35 Express Chipset

Development Kit

User’s Manual

October 2007

Order Number: 318476-001US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See http://www.intel.com/products/processor_number for details.

The Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Hyper-Threading Technology requires a computer system with an Intel® Pentium® 4 processor supporting HT Technology and a HT Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See http://www.intel.com/ products/ht/Hyperthreading_more.htm for additional information.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, IPLink, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others. Copyright © 2007, Intel Corporation. All Rights Reserved.

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit |

|

User’s Manual |

October 2007 |

2 |

Order Number: 318476-001US |

Contents—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

Contents

1.0 About This Manual ..................................................................................................... |

6 |

||

1.1 |

Content Overview................................................................................................ |

6 |

|

1.2 |

Text Conventions ................................................................................................ |

6 |

|

1.3 |

Glossary of Terms and Acronyms........................................................................... |

7 |

|

1.4 |

Support Options.................................................................................................. |

8 |

|

|

1.4.1 |

Electronic Support Systems ....................................................................... |

8 |

|

1.4.2 |

Additional Technical Support ...................................................................... |

8 |

1.5 |

Product Literature ............................................................................................... |

8 |

|

2.0 Development Kit Hardware Features ....................................................................... |

10 |

||

2.1 |

Intel® Q35 Express Chipset Development Kit Overview.......................................... |

10 |

|

2.2 |

System Block Diagram ....................................................................................... |

11 |

|

2.3 |

Development Kit Inventory Checklists .................................................................. |

12 |

|

2.4 |

Processor Support ............................................................................................. |

14 |

|

2.5 |

System Memory ................................................................................................ |

14 |

|

|

2.5.1 Dual Channel (Interleaved) Mode Configurations ........................................ |

15 |

|

|

2.5.2 Single Channel (Asymmetric) Mode Configurations...................................... |

17 |

|

2.6 |

Back-Panel Connectors....................................................................................... |

18 |

|

|

2.6.1 |

Audio-Connectors................................................................................... |

18 |

|

2.6.2 RJ-45 LAN Connector with Integrated LEDs................................................ |

19 |

|

|

2.6.3 |

USB Port ............................................................................................... |

19 |

|

2.6.4 Coaxial S/PDIF In/Out Connector.............................................................. |

19 |

|

|

2.6.5 |

eSATA Port ............................................................................................ |

19 |

2.7 |

Debug Features................................................................................................. |

20 |

|

|

2.7.1 |

Extended Debug Probe (XDP)................................................................... |

20 |

|

2.7.2 |

Power LEDs ........................................................................................... |

20 |

|

2.7.3 Port 80 POST Code LEDs ......................................................................... |

20 |

|

|

2.7.4 |

Voltage Reference .................................................................................. |

21 |

2.8 |

Development Kit Major Connectors and Jumpers.................................................... |

21 |

|

|

2.8.1 |

Jumper Functions ................................................................................... |

22 |

|

2.8.2 USB 2.0 Front Panel ............................................................................... |

22 |

|

|

2.8.3 |

1394a Header ........................................................................................ |

22 |

2.9 |

SPI Removal / Installation Technique ................................................................... |

23 |

|

|

2.9.1 |

SPI Device Removal................................................................................ |

24 |

|

2.9.2 |

SPI Device Installation ............................................................................ |

24 |

3.0 Setting Up and Configuring the Development Kit ..................................................... |

26 |

||

3.1 |

Overview ......................................................................................................... |

26 |

|

3.2 |

Installing Board Standoffs .................................................................................. |

26 |

|

3.3 |

BTX Heatsink Setup with SRM ............................................................................. |

28 |

|

|

3.3.1 SRM Alignment on any BTX Board ............................................................ |

28 |

|

3.4 |

Board Setup and Configuration before Boot........................................................... |

30 |

|

3.5 |

Post Codes Definitions........................................................................................ |

32 |

|

|

3.5.1 |

Normal Post Codes ................................................................................. |

32 |

Figures

1 |

Board Features ........................................................................................................ |

11 |

2 |

Intel® Q35 Express Chipset Development Kit block diagram .......................................... |

12 |

3 |

Memory Channel and DIMM Configuration ................................................................... |

15 |

4 |

Dual Channel (Interleaved) Mode Configuration with 2x DIMMs ...................................... |

16 |

5 |

Dual Channel (Interleaved) Mode Configuration with 3x DIMMs ...................................... |

16 |

|

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit |

|

October 2007 |

User’s Manual |

|

Order Number: 318476-001US |

3 |

|

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Contents

6 |

Dual Channel (Interleaved) Mode Configuration with 4x DIMMs....................................... |

17 |

7 |

Single Channel (Asymmetric) Mode Configuration with 1x DIMM ..................................... |

17 |

8 |

Single Channel (Asymmetric) Mode Configuration with 3x DIMMs.................................... |

18 |

9 |

Back-panel Connectors.............................................................................................. |

18 |

10 |

LAN Connector LED locations...................................................................................... |

19 |

11 |

ITP-XDP Connector location (J2BC) ............................................................................. |

20 |

12 |

Major Jumper and Header Locations............................................................................ |

21 |

13 |

Location for 1394a Header and USB Front Panel ........................................................... |

23 |

14 |

SPI Socket with Retaining Clip.................................................................................... |

24 |

15 |

SPI Device Installation .............................................................................................. |

25 |

16 |

Intel® Q35 Development Kits .................................................................................... |

26 |

17 |

Mounting Hole Locations............................................................................................ |

27 |

18 |

Mounting the Standoff for BTX Heatsink....................................................................... |

28 |

19 |

Casing with “Support and Retention Module” ................................................................ |

28 |

20 |

BTX board alignment on SRM ..................................................................................... |

29 |

21 |

Heatsink Alignment................................................................................................... |

29 |

22 |

Tightening Heatsink on the SRM and Board .................................................................. |

30 |

23 |

CPU Fan location ...................................................................................................... |

31 |

24 |

2x12 Standard power supply and 2x2 power supply ...................................................... |

32 |

Tables |

|

|

1 |

Definition ................................................................................................................. |

7 |

2 |

Intel Literature Centers .............................................................................................. |

9 |

3 |

Development Kit Hardware Items ............................................................................... |

12 |

4 |

Development Kit Board Specification ........................................................................... |

13 |

5 |

Internal I/O headers ................................................................................................. |

13 |

6 |

Supported Intel Technologies ..................................................................................... |

13 |

7 |

Additional Features ................................................................................................... |

14 |

8 |

LAN Connector LED status ......................................................................................... |

19 |

9 |

Voltage Reference detail............................................................................................ |

21 |

10 |

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit Board |

|

|

Jumpers Description ................................................................................................. |

22 |

11 |

USB Front Panel ....................................................................................................... |

22 |

12 |

1394a Header .......................................................................................................... |

23 |

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit |

|

User’s Manual |

October 2007 |

4 |

Order Number: 318476-001US |

Revision History—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

Revision History

Date |

Revision |

Description |

|

|

|

October 2007 |

001 |

Initial release |

|

|

|

|

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit |

October 2007 |

User’s Manual |

Order Number: 318476-001US |

5 |

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—About This Manual

1.0About This Manual

This user’s manual describes the use of the Intel® Q35 Express Chipset Development Kit. This manual has been written for OEMs, system evaluators, and embedded system developers. All jumpers, headers, LED functions, and their locations on the board, along with subsystem features and POST codes, are defined in this document.

For the latest information about the Intel® Q35 Express Chipset Development Kit reference platform, visit:

http://developer.intel.com/design/intarch/devkits/ index.htm?iid=embed_body+devkits

For design documents related to this platform, such as schematics and layout, please contact your Intel Representative.

1.1Content Overview

Chapter 1.0, “About This Manual”

This chapter contains a description of conventions used in this manual. The last few sections explain how to obtain literature and contact customer support.

Chapter 2.0, “Development Kit Hardware Features”

This chapter provides information on the development kit features and the board capability. This includes the information on board component features, jumper settings, pin-out information for connectors and overall development kit board capability.

Chapter 3.0, “Setting Up and Configuring the Development Kit”

This chapter provides instructions on how to configure the evaluation board and processor assembly by setting BTX heatsink, jumpers, connecting peripherals, providing power, and configuring the BIOS.

1.2Text Conventions

The following notations may be used throughout this manual.

# |

The pound symbol (#) appended to a signal name indicates that |

|

the signal is active low. |

Variables |

Variables are shown in italics. Variables must be replaced with |

|

correct values. |

Instructions |

Instruction mnemonics are shown in uppercase. When you are |

|

programming, instructions are not case-sensitive. You may use |

|

either upper-case or lower-case. |

Numbers |

Hexadecimal numbers are represented by a string of |

|

hexadecimal digits followed by the character H. A zero prefix is |

|

added to numbers that begin with A through F. (For example, FF |

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit |

|

User’s Manual |

October 2007 |

6 |

Order Number: 318476001US |

About This Manual—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

is shown as 0FFH.) Decimal and binary numbers are represented by their customary notations (That is, 255 is a decimal number and 1111 1111 is a binary number). In some cases, the letter B is added for clarity.

Units of Measure |

The following abbreviations are used to represent units of |

|

|

measure: |

|

|

GByte |

gigabytes |

|

KByte |

kilobytes |

|

MByte |

megabytes |

|

MHz |

megahertz |

|

W |

watts |

|

V |

volts |

Signal Names |

Signal names are shown in uppercase. When several signals |

|

|

share a common name, an individual signal is represented by |

|

the signal name followed by a number, while the group is represented by the signal name followed by a variable (n). For example, the lower chip-select signals are named CS0#, CS1#, CS2#, and so on; they are collectively called CSn#. A pound symbol (#) appended to a signal name identifies an active-low signal. Port pins are represented by the port abbreviation, a period, and the pin number (e.g., P1.0).

1.3Glossary of Terms and Acronyms

|

This section defines conventions and terminology used throughout this document. |

||

Table 1. |

Definition |

(Sheet 1 of 2) |

|

|

|

|

|

|

Term |

|

Description |

|

|

|

|

|

|

|

Advanced Digital Display Card – 2nd Generation. This card provides digital display options |

|

|

|

for an Intel Graphics Controller that supports ADD2+ cards. It plugs into a x16 PCI |

|

ADD2 Card |

|

Express* connector but uses the multiplexed SDVO interface. The card adds Video In |

|

|

capabilities to platform. This Advanced Digital Display Card will not work with an Intel |

|

|

|

|

|

|

|

|

Graphics Controller that supports DVO and ADD cards. It will function as an ADD2 card in |

|

|

|

an ADD2 supported system, but video in capabilities will not work. |

|

|

|

|

|

ACPI |

|

Advanced Configuration and Power Interface |

|

|

|

|

|

Core |

|

The internal base logic in the (G)MCH |

|

|

|

|

|

DDR2 |

|

A second generation Double Data Rate SDRAM memory technology |

|

|

|

|

|

DMI |

|

(G)MCH-IntelÆ ICH9 Direct Media Interface |

|

DVI |

|

Digital Video Interface. Specification that defines the connector and interface for digital |

|

|

displays. |

|

|

|

|

|

|

|

|

|

|

FSB |

|

Front Side Bus. FSB is synonymous with Host or processor bus |

|

|

|

|

|

GMA 3100 |

|

Intel® Graphic Media Accelerator 3100 |

|

|

|

|

|

|

|

Eighth generation I/O Controller Hub component that contains additional functionality |

|

IntelÆ ICH9 |

|

compared to previous ICHs. The I/O Controller Hub component contains the primary PCI |

|

|

|

interface, LPC interface, USB2, ATA-100, and other I/O functions. It communicates with |

|

|

|

the (G)MCH over a proprietary interconnect called DMI. |

|

|

|

|

|

IGD |

|

Internal Graphics Device. |

|

|

|

|

|

LVDS |

|

Low Voltage Differential Signaling. A high speed, low power data transmission standard |

|

|

used for display connections to LCD panels. |

|

|

|

|

|

|

|

|

|

|

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit |

October 2007 |

User’s Manual |

Order Number: 318476001US |

7 |

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—About This Manual

Table 1. |

Definition |

(Sheet 2 of 2) |

|

|

|

|

|

|

Term |

|

Description |

|

|

|

|

|

|

|

Advanced Digital Display Card – 2nd Generation. This card provides digital display options |

|

|

|

for an Intel Graphics Controller that supports ADD2+ cards. It plugs into a x16 PCI |

|

ADD2 Card |

|

Express* connector but uses the multiplexed SDVO interface. The card adds Video In |

|

|

capabilities to platform. This Advanced Digital Display Card will not work with an Intel |

|

|

|

|

|

|

|

|

Graphics Controller that supports DVO and ADD cards. It will function as an ADD2 card in |

|

|

|

an ADD2 supported system, but video in capabilities will not work. |

|

|

|

|

|

|

|

Memory Controller Hub component that contains the processor interface, DRAM |

|

MCH |

|

controller, and x16 PCI Express* port (typically, the external graphics interface). It |

|

|

communicates with the I/O controller hub (Intel ICH9) and other I/O controller hubs over |

|

|

|

|

|

|

|

|

the DMI interconnect. In this document MCH refers to the Intel® Q35 MCH component. |

|

|

|

|

|

MEC |

|

Media Expansion Card, also known as ADD2+ card. Refer to ADD2+ term for description. |

|

|

|

|

|

|

|

Third Generation input/output graphics attach called PCI Express* Graphics. PCI Express* |

|

PCI Express* |

|

is a high-speed serial interface whose configuration is software compatible with the |

|

|

existing PCI specifications. The specific PCI Express* implementation intended for |

|

|

|

|

|

|

|

|

connecting the (G)MCH to an external Graphics Controller is a x16 link and replaces AGP. |

|

|

|

|

|

|

|

The Primary PCI is the physical PCI bus that is driven directly by the ICH9 component. |

|

Primary PCI |

|

Communication between Primary PCI and the (G)MCH occurs over DMI. Note that the |

|

|

|

Primary PCI bus is not PCI Bus 0 from a configuration standpoint. |

|

|

|

|

|

|

|

Serial Digital Video Out (SDVO). SDVO is a digital display channel that serially transmits |

|

|

|

digital display data to an external SDVO device. The SDVO device accepts this serialized |

|

SDVO |

|

format and then translates the data into the appropriate display format (i.e., TMDS, |

|

|

LVDS, TV-Out). This interface is not electrically compatible with the previous digital |

|

|

|

|

|

|

|

|

display channel - DVO. For the 82Q965 GMCH, it will be multiplexed on a portion of the |

|

|

|

x16 graphics PCI Express* interface. |

|

|

|

|

|

SDVO Device |

|

Third party codec that uses SDVO as an input. May have a variety of output formats, |

|

|

including DVI, LVDS, HDMI, TV-out, etc. |

|

|

|

|

|

|

|

|

|

|

|

|

System Management Interrupt. SMI is used to indicate any of several system conditions |

|

SMI |

|

(such as, thermal sensor events, throttling activated, access to System Management |

|

|

|

RAM, chassis open, or other system state related activity). |

|

|

|

|

|

|

|

A unit of DRAM corresponding to eight x8 SDRAM devices in parallel or four x16 SDRAM |

|

Rank |

|

devices in parallel, ignoring ECC. These devices are usually, but not always, mounted on a |

|

|

|

single side of a DIMM. |

|

|

|

|

1.4Support Options

1.4.1Electronic Support Systems

Intel’s site on the World Wide Web (http://www.intel.com/) provides up-to-date technical information and product support. This information is available 24 hours per day, 7 days per week, providing technical information whenever you need it.

Product documentation is provided online in a variety of web-friendly formats at:

(http://developer.intel.com/)

1.4.2Additional Technical Support

If you require additional technical support, please contact your field sales representative or local distributor.

1.5Product Literature

Product literature can be ordered from the following Intel literature centers:

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit |

|

User’s Manual |

October 2007 |

8 |

Order Number: 318476001US |

About This Manual—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

Table 2. |

Intel Literature Centers |

|

|

|

|

|

Location |

Telephone Number |

|

|

|

|

U.S. and Canada |

1-800-548-4725 |

|

|

|

|

U.S. (from overseas) |

708-296-9333 |

|

|

|

|

Europe (U.K.) |

44(0)1793-431155 |

|

|

|

|

Germany |

44(0)1793-421333 |

|

|

|

|

France |

44(0)1793-421777 |

|

|

|

|

Japan (fax only) |

81(0)120-47-88-32 |

|

|

|

|

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit |

October 2007 |

User’s Manual |

Order Number: 318476001US |

9 |

Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Development Kit Hardware Features

2.0Development Kit Hardware Features

This chapter describes the features of the Intel® Q35 Development Kit. These recommendations would largely apply to other designs incorporating Intel® Q35 chipset. This documentation should be used in conjunction with the datasheets, specification updates and platform design guides for the Intel® I/O Controller Hub 9 (ICH9) Family and the Intel® Q35 Express Chipset. Contact your Intel representative for the availability of these documents.

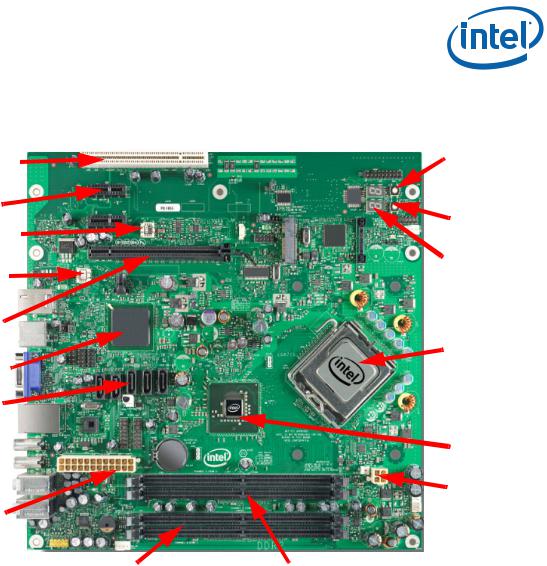

2.1Intel® Q35 Express Chipset Development Kit Overview

Figure 1 shows overview of the major features present on the development kit board. Refer to next page for system block diagram of the development kit’s motherboard.

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit |

|

User’s Manual |

October 2007 |

10 |

Order Number: 318476001US |

Development Kit Hardware Features—Intel Core 2 Duo Processor and Intel Q35 Express Chipset

Figure 1. |

|

Board Features |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Reset button |

|||||

|

|

|

|

PCI Slot |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

PCI Express |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

x1 Slot |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Power Button |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SPI EEPROM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

(Secondary) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Port 80 LED Display |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SPI EEPROM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

(Primary) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

PCI Express |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

x16 Graphics |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

Slot |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LGA775 Processor |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Socket |

|

||||

|

|

|

Intel® I/O |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

Controller Hub |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

(ICH) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

SATA Port |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Intel® Q35 Memory |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Controller Hub (MCH) |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2x2 Standard |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Power Supply |

|

|

|

|

|

|

|

|

|

2x12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

Standard |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Power Supply |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2-DIMM per channel DDR2 |

|

2-DIMM per channel DDR2 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

667/800 (Channel-B) |

|

667/800 (Channel-A) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2.2System Block Diagram

This section will document the common features that are applicable to the Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit. Figure 2 shows a simple block diagram of the development kit.

|

Intel® CoreTM 2 Duo Processor and Intel ® Q35 Express Chipset Development Kit |

October 2007 |

User’s Manual |

Order Number: 318476001US |

11 |

Loading...

Loading...